Tag: 指令集

100%自主指令集 GRUB 2.12正式支持龍芯龍架構

快科技12月27日消息,2.06版本發布兩年半之後,來自GNU項目的啟動引導程序GRUB近日迎來最大升級版本2.12,加入了對中國龍芯中科自研的LoongArch龍架構的完整支持。

GRUB用於在計算機啟動時加載作業系統,允許用戶選擇要啟動的作業系統和啟動參數,並提供交互式命令行界面。

利用GRUB,用戶可以在多個作業系統之間切換,或在啟動時進行一些配置和診斷。

它還提供了一些有用的命令和選項,例如加載驅動程序、查看系統信息、設置啟動參數等。

總之, GRUB是一個功能強大且靈活的啟動引導程序,為用戶提供更多的控制和靈活性,使計算機啟動過程更加可靠方便。

GRUB 2.12版本運行截圖

GRUB 2.12使用中文及主題運行截圖

GRUB正式支持龍架構,標志著龍芯軟體生態又向前邁進堅實一步,對於龍芯生態、龍芯產業鏈上的中下游廠商和龍芯用戶來說,都是重大利好,有助於促進龍芯處理器的應用和發展。

對於龍芯生態,這增強了龍芯處理器的可移植性和兼容性。

通過與主流引導程序相兼容,龍芯處理器應用范圍進一步擴大,從而降低龍架構學習成本,並吸引更多開發者和廠商關注龍芯處理器,促進生態繁榮。

對於龍芯產業鏈上的中下游廠商,這降低了開發成本和難度。

廠商可以更容易地將自己的產品與龍芯處理器相結合,無需花費大量時間和資源來開發或維護引導程序。有助於提高產品競爭力,促進整個產業鏈的發展。

對於龍芯用戶,這有助於提升使用體驗。

龍芯用戶可以更加方便地安裝和切換作業系統,同時也可以享受更加穩定可靠的引導體驗。

來源:快科技

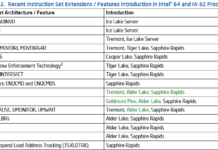

Intel AVX-512指令集發飆 性能暴漲17倍:自家CPU卻不能跑

Intel近日更新了開源的C++頭文件庫,正式支持AVX-512 SIMD指令集,相比此前的AVX-2指令集,可以提供更高性能的SIMD排序。

基於AVX-512指令集,C++頭文件庫可以對16位、64位數據類型進行快速排序,實測在一套Intel Tiger Lake 11代酷睿系統上,NumPy Python的性能提升了多達10-17倍。

具體來說,16位數據排序性能提升了17倍,32位數據也有12-13倍,64位浮點數據則可以提速10倍。

這證明,AVX-512隻要適配優化得當,帶來的性能提升是十分顯著的,而且不一定非得吃掉多高功耗。

不過,Intel 12/13代酷睿因為引入混合架構,不得不犧牲了AVX-512,自然無法從中受益,AMD Zen4架構的銳龍7000系列則首次加入了AVX-512。

這就有點尷尬了。

來源:快科技

AMD Zen4銳龍7000打修正檔:正式開啟AVX-512指令集

AMD銳龍7000系列不但帶來了5nm工藝、Zen4架構、RDNA2 GPU核心、DDR5記憶體、PCIe 5.0總線、AM5接口,,這在之前可是Intel的獨門絕技。

近日,AMD更新了Linux GCC編譯器的基礎代碼,相當於為新的Zenver4打了個小修正檔,加入了對AVX-512指令集的支持。

具體支持指令包括:AVX512F、AVX512DQ、AVX512IFMA、AVX512CD、AVX512BW、AVX512VL、AVX512BF16、AVX512VBMI、AVX512VBMI2、GFNI、AVX512VNNI、AVX512BITALG、AVX512VPOPCNTDQ。

即將在年底發布的同樣Zen4架構的下一代霄龍9004系列,同樣會為AMD的伺服器、數據中心方案帶來AVX-512指令集。

值得一提的是,同樣是AVX-512指令集,Intel是完整的512-bit通道,AMD則砍到了256-bit,因此在執行512-bit的指令就需要拆分成兩個256-bit指令,官方稱這可以節省晶片面積,避免發熱過大、性能降低。

諸多新指令中,VNNI、BF16是面向AI加速的,官方號稱FP32浮點推理多線程性能可提升1.31倍,VNNI INT8整數推理多線程性能可提升2.47倍!

來源:快科技

微軟確認CPU太先進會讓Win11出現數據損壞:打完修正檔更尷尬了

遇到這樣的BUG已經很無語了,沒想到修復方案更令人尷尬。

微軟日前確認,Windows 11和Windows Server 2022存在BUG,在支持VAES指令集的環境下,可能到導致數據損壞。

Intel從10代酷睿(Ice Lake)和第三代至強可擴展處理器(IceLake-SP)開始才添加了對VAES的支持,AMD這邊則是Zen 3銳龍5000,它也是AVX-512的組成部分。

沒想到,因為處理器太先進,導緻密碼本算法模式不同,進而可能造成數據損毀。

不過,微軟接著表示,早在5月(預覽版)、6月份(正式版),它們就推送了修復修正檔。

可更尷尬的事情在於,打修正檔後會造成性能下降,尤其是在BitLocker、TLS、硬碟密集傳輸負載場景下時,調用AES指令集的任務可能因此慢兩倍。

被炮轟後,微軟現在建議用戶再次安裝6月23日和7月12日的最新修正檔,這次通過修改Windows核心加密庫的代碼路徑,減輕了性能下滑問題。

來源:快科技

12代酷睿封殺的AVX-512被AMD Zen4支持了:玩模擬器遊戲沖破240幀

第三代高級矢量擴展擴展指令集AVX-512居然讓Intel都舉棋不定。11代酷睿用上後,一度成為電老虎代名詞,導致功耗「爆炸」。

12代酷睿雖然一開始大方支持,可是Intel從今年3月份居然從硬體層面屏蔽了AVX-512。

不過,如果你是PS3模擬器RPCS3用戶,那麼手頭有支持AVX-512指令集的處理器,那可就真是撿漏了。

在開發者Whatcookie的最新文章中,詳述了處理器指令集對模擬器性能發揮的重要影響,測試選取的是酷睿i9-12900K。

運行《戰神》時,開啟SSE2指令集,幀數只有5FPS;打開SSE 4.1後,幀數暴增到160FPS;再開啟AVX2/FMA指令集,又增加了13%性能;直到最後打開AVX-512,則提高了30%,達到242FPS。

雖然,新批次的12代酷睿幹掉了AVX-512,但即將推出的AMD Zen 4銳龍7000則歡喜迎娶之。

來源:快科技

Intel 12代酷睿無情封殺AVX-512指令集:看一眼LOGO就知道了

AVX-512指令集雖然褒貶不一,但一直是Intel的招牌,

但是在自家酷睿處理器產品上,Intel對於AVX-512的支持卻一直搖擺不定,尤其是12代酷睿,大概是引入了混合架構的緣故,AVX-512更是神秘莫測。

在最早的開發者指導上,12代酷睿桌面版的大核心明確標注支持AVX-512,但隨後Intel做出更改,強調這一代不提供AVX-512。

發布之後,12代酷睿很快被破解,可以開啟AVX-512,一些主板廠商也公開提供支持。

不幸的是,到了3月份,Intel痛下殺手,,再無破解可能。

如果你真的需要在12代酷睿上跑AVX-512指令集,其實有一種很簡單的方法找到支持它的批次,那就是看錶面Intel LOGO。

如上圖:如果LOGO是環形的,那就是2021年生產的批次,支持,可破解;如果是方形的,那就是2022年產的,不支持了。

其實,有很多用戶在看到這個方形LOGO的時候,還認為是不是假貨,但,風格都更加方正。

來源:快科技

龍芯3C5000伺服器處理器發布:16核性能媲美ARM 64核

6月6日下午消息,在今日舉辦的「2022年LoongArch生態發展暨通明湖創新應用論壇」線上活動中,龍芯發布了3C5000伺服器處理器,進一步完善了龍芯三號產品線家族。

據介紹,3C5000系列是面向伺服器領域的高性能通用處理器,採用純自主LoongArch指令架構,可滿足通用計算、大型數據中心、雲計算中心的計算需求。

性能方面,官方表示16核心單晶片unixbench分值9500以上,雙精度計算能力達560GFlops,16核處理器峰值性能與典型ARM 64核處理器的峰值性能相當,並支持最高16路互連,搭配新一代龍芯7A2000橋片,PCIe吞吐帶寬比上一代提升400%以上。

安全方面,該處理器通過晶片級安全機制可為等保2.0、可信計算、國密算法替代、網絡安全漏洞防護等提供CPU級內生支持。

另據,3C5000L主頻2.0~2.2GHz,最大16核,每個CPU核擁有128KB一級緩存、256KB二級緩存、每4核共享16MB三級緩存,支持DDR4-3200 ECC記憶體,典型功耗130W(2.2GHz)。

來源:快科技

AMD確認Zen 4單核性能提升15%是保守了:IPC增幅稍後公布

本周,AMD分享了Zen 4銳龍7000處理器的大量核心信息,但同時也留下一些外界好奇的疑問。

在TPU分享的Q&A中,AMD技術營銷總監Robert Hallock就大量外界好奇的點給出答案。

1、16核32線程將是銳龍7000系列處理器發布時最大核心數設定。

2、Robert認為現在談論最終遊戲性能有些為時尚早。他承認,目前給出的單線程性能提升15%的確是保守數字,關於IPC(每時鍾周期指令集,基本等價同頻性能)的增幅、還有功耗、晶片面積等情況,會在今夏晚些時候對外公布。

3、Zen 4確認支持AVX 512指令集,也就是第三代矢量加速指令集(AVX3),其中AVX 512 VNNI用於加速神經網絡計算,AVX 512 BLOAT16用於加速推理,Robert贊揚它們的加速效果很好。

來源:快科技

銳龍7000支持Intel獨家AVX512指令集?Zen4有AI加速了

AMD今天發布了銳龍7000系列處理器,秋季上市,CPU升級5nm Zen4,IO核心升級6nm,還集成了RDNA2架構的核顯,支持DDR5及PCIe 5.0等新技術。

有關銳龍7000的新特性也在不斷被挖掘,比如新的指令集,在發布會上AMD提到Zen4會增加一些與AI有關的加速指令集,不過AMD並沒有提及細節。

消費級CPU中增加AI指令是Intel在10代酷睿處理器首次實現的,目前的新一代酷睿都有類似的功能,這些指令是Intel的AVX512指令集中的一部分,可以提升AI性能,增加個三五倍沒有問題。

AMD的銳龍7000支持的AI指令應該也是差不多,甚至就是AVX512中的,此前早有傳聞稱Zen4會支持AVX512了,不過消費級的Zen4不一定是完整支持,支持其中部分加速指令集就可以。

預計用於伺服器市場的Zen4架構EPYC處理器才會支持更完整的AVX512指令集,畢竟目前AMD的AVX指令集支持才到AVX2,需要填補空白了。

來源:快科技

Intel 12代酷睿破解開啟AVX-512指令集:性能上去、功耗下來

Intel 12代酷睿突破性地採用了P核+E核的混合架構設計,但為了確保此架構的順利執行,刻意關閉了P核原本支持的AVX-512指令集。

事實上,12代酷睿發布之前,原本是可以開啟AVX-512指令集的,早期的Z690主板工程樣板上也有相關選項,但在最後時刻,Intel確定將其屏蔽掉,後續的H670、B660、H610主板都默認關閉。

近日,微星悄然為Z690 Unify-X等主板發放了新版A22 BIOS,赫然可以選擇是否開啟AVX-512,而且可以同時關閉E核、只保留P核。

AVX-512指令集對遊戲玩家可以說毫無用處,但它包含了一系列可以加速工作負載的指令,比如科學模擬、金融分析、人工智慧、深度學習、3D建模、音視頻處理器、加密解密、數據壓縮等,在特定項目、跑分測試中效果明顯。

之前的11代酷睿等平台上,AVX-512堪稱電老虎,用它烤機功耗直接爆炸,但這一次似乎有些不同。

比如在Y-Cruncher測試中,i9-12900K利用這塊微星Z690主板打開AVX-512之後,跑分創下8核處理器的新高,功耗反而還降低了!

當然,這種玩法不建議一般用戶嘗試,微星也明確標注只是試驗性的功能。

按照慣例,它可能很快就會被封殺。

來源:快科技

自研CPU指令集 龍芯稱已支持x86+Windows下應用及列印機

2021年龍芯發布了自主研發的LoongArch指令集,跟ARM、x86等指令集是獨立的,所以軟體兼容性是一大難題,現在龍芯方面表示,已經通過二進位翻譯支持了x86+windows系統下的部分應用及大量列印機外設。

在龍芯中科的首屆生態創新大會上,龍芯方面表示,目前,龍芯自主指令系統LoongArch已經初步構建了基礎軟體技術體系。

包括BIOS、內核、GCC編譯器、LLVM編譯器、GoLang編譯器、Java虛擬機、JavaScript虛擬機、.NET虛擬機、瀏覽器、媒體播放器、圖形庫、KVM虛擬機等作業系統核心模塊已經完成向LoongArch的遷移,並集成在龍芯中科基礎版作業系統Loongnix中提供給生態夥伴。

系統及軟體方面,統信作業系統、麒麟作業系統、龍蜥作業系統、WPS辦公軟體、微信、360瀏覽器等均已支持LoongArch。

此外,龍芯提到,通過二進位翻譯支持了X86/Linux平台和X86/Windows平台的部分應用以及X86/Windows平台的大量列印機外設。

未來,龍芯中科將推出基於LoongArch的充分考慮兼容需求的自主編程框架。

來源:快科技

龍芯:Linux內核正在支持自研LoongArch指令集

龍芯中科在去年推出了自研的CPU指令集LoongArch,龍芯推出的龍芯3A5000及伺服器版龍芯3C5000已經全面支持LoongArch指令,今天在生態大會上龍芯表示Linux內核社區正在實現對LoongArch的支持。

龍芯表示,龍芯中科正在積極推動在上游社區建立LoongArch 分支,在國際開源社區建立與 X86、ARM等並列的LoongArch 分支是龍芯生態的根基。

目前,LoongArch 已從GNU組織獲得表徵二進位格式的ELF Machine編號(258 號),二進位開發工具 binutils 已經並入開源社區,GCC、C 庫、內核正在並入開源社區,包括瀏覽器在內的部分基礎軟體已並入開源社區。

2022 年起,龍芯將每年投入一定的經費資助海外社區開發者的工作。在得到上游開源社區支持後,LoongArch 生態將隨社區自動演進,可以極大豐富支持 LoongArch 的軟體版本,大幅減少軟體遷移適配工作。

根據龍芯的數據,Linux內核官方版正在實現對LoongArch的完善支持,GCC等三大編譯器正在實現對LoongArch的特性支持,JAVA虛擬機的JDK14中貢獻率全球第四,.NET社區正在實現對LoongArch架構的支持,瀏覽器及流媒體播放中已經有產品實現對LoongArch的支持。

來源:快科技

主板廠商確認 B660/H610主板出廠默認禁用AVX512指令集

最近有關12代酷睿AVX512指令集的問題引發了玩家關注,包括華碩、微星等主板廠商在內,他們在Intel要求下升級了BIOS,在Z690主板中禁用了AVX512指令集。

AVX512是Intel最新的AVX適量擴展指令集,可以大幅提升浮點性能,這一版指令集首發於2013年,主要是給至強處理器用的,這幾年來在消費級酷睿上也有支持。

在最新的12代酷睿上,Intel從來提到過處理器支持AVX512,但實際使用中有用戶發現可以開啟AVX512支持,只需要禁用E-Core,也就是能效核,P-Core性能核就可以支持AVX512了。

但是Intel及主板廠商現在封殺的就是這種方式,多家主板廠商最近都升級了BIOS,已經不再允許關閉E-Core核,大核也開啟不了AVX512指令集了。

在堵上Z690主板這個漏洞之後,這兩天發布的主流晶片組,如B660、H610系列更是從源頭上就封殺了AVX512,主板廠商已經確認出廠時的BIOS就默認禁用了AVX512指令集,大家不用多想了。

話說回來,對消費級酷睿用戶來說,AVX512指令集也沒什麼可糾結的,支持該指令集的應用並不多,對遊戲性能更沒什麼影響,開啟之後功耗還會大幅增加,沒有就沒有吧。

來源:快科技

Intel 12代酷睿封殺AVX-512指令集:不再允許關閉小核

Intel似乎要做出一個讓人有些詫異的決定,即徹底禁用12代酷睿對AVX-512指令集的支持。

據悉,AVX-512也就是AVX3,也就是「高級矢量擴展」,第一代AVX出現於Sandy Bridge二代酷睿,第二代AVX2誕生於2011年的四代酷睿(Haswell),最新的第三代則發布於2013年,最早用於至強產品線,目前已經下放給11代酷睿Rocket Lake。

簡單來說,AVX-512包含一系列可以加速工作負載的指令,包括科學模擬、金融分析、人工智慧、深度學習、3D建模、音視頻處理器、加密解密、數據壓縮等。

雖然外界想當然地認為Alder Lake支持AVX-512,且用戶發現可以在BIOS中禁用E核來啟用AXV-512,但Intel卻表示,這樣會帶來未知錯誤,將通過微碼更新在BIOS中完全封殺掉AVX-512。

顯而易見的原因是,12代酷睿Alder Lake採用混合架構,小核(E核)Gracemont並不支持AVX-512,為了這一指令集關閉E核的做法,Intel難以接受。

之所以說詭異是因為,IgorLabs測試發現,12代酷睿大核Golden Cove開啟AVX-512後能效甚至比AVX2還高,這和11代酷睿大相逕庭,後者的AVX-512簡直電老虎。另外,前不久還在社交平台建議12代酷睿用戶關閉E核開啟P核AVX512指令集,這樣可實現遊戲幀數大幅提升。

合理的解釋應該是,雖然AVX-512開啟後的確在某些場景下有加成,可代價是犧牲E核,在Intel看來,還有更多的工作負載需要P核+E核共同參與,這樣得不償失。

顯然,如果你當前的主板BIOS還能有開啟AVX-512的可能且懂得如何駕馭,那還是暫緩升級BIOS了。

來源:快科技

AVX512指令集加成:12代酷睿運行PS3模擬器速度起飛

又多了一個選購12代酷睿、放棄AMD Zen3的理由?

知名PS3模擬器RPCS3在社交平台和用戶分享稱,AVX512指令集對模擬器性能的加成很明顯。

所以對12代酷睿用戶,要做的就是屏蔽掉E核和超線程,實測在鎖定5.2GHz頻率的情況下,對12900K對比11900K能提升15%的幀數,以《戰神:升天(Gold of War: Ascension)》為例,從68FPS提升到78FPS。

AVX512的優勢還體現在,即便是11代酷睿,運行RPCS3模擬器的性能也要比AMD Zen3銳龍5000有著大幅優勢。

據悉,AVX-512也就是AVX3,也就是「高級矢量擴展」,第一代AVX出現於Sandy Bridge二代酷睿,第二代AVX2誕生於2011年的四代酷睿(Haswell),最新的第三代則發布於2013年,最早用於至強產品線,目前已經下放到Ice Lake 10代酷睿以後產品。

AVX、AVX2此前已得到AMD處理器的支持,AVX-512則一直是Intel的「專利」(盡管應用並不多),而接下來的AMD Zen4可能會加入對AVX-512的支持。

來源:快科技

龍芯自主指令集二進位翻譯應用:可流暢打CS

龍芯中科宣布,推出基於自主指令系統LoongArch的二進位翻譯應用解決方案,二進位翻譯為核心技術,旨在消除指令壁壘,實現不同平台軟體的兼容運行。

支持場景包括MIPS、x86、ARM平台上廠商已停止支持的老舊軟硬體,以及廠商無法提供充分技術支持的商業閉源軟體。

官方稱,龍芯架構具有完全自主、技術先進、兼容生態三方面特點,LoongArch指令集也在設計之初就充分考慮了生態兼容需求,把實現將異構平台現有應用軟體平滑遷移到龍芯平台作為設計目標。

除了基礎指令、虛擬機擴展指令等指令外,LoongArch還包含二進位翻譯擴展指令,以支持龍芯二進位翻譯系統對其他架構下二進位指令的高效翻譯。

龍芯二進位翻譯系統基於LoongArch二進位翻譯擴展指令實現,利用軟硬體結合的翻譯優化技術,實現跨指令集、跨作業系統間的應用兼容、高效運行。

龍芯二進位翻譯應用解決方案通過三個龍芯二進位翻譯系統LATM(LAT from MIPS)、LATA(LAT from ARM)、LATX(LAT from X86),分別支持MIPS、ARM、x86平台的應用在龍芯平台的安裝運行。

龍芯二進位翻譯系統作為中間層,通過架構層支持與軟硬協同算法優化,充分利用本地硬體,最大化提升模擬效率,為上層應用軟體提供目標指令集的良好虛擬運行環境。

二進位翻譯技術是實現跨指令系統兼容的重要手段,通過在宿主機(host)上用軟體模擬目標機/客戶機(guest)指令系統兼容的CPU,從而在宿主機上執行客戶機的二進位代碼,達到兼容的目的。

該方案的最大問題是效率,因為純軟體模擬的CPU,要比硬體直接實現的CPU慢很多,運行速度往往都是數量級的差異。

龍芯二進位翻譯系統利用動態二進位翻譯技術,使用了多種軟硬體結合的翻譯優化技術,利用LoongArch指令集二進位翻譯擴展提供的EFLAGS運算標志指令與浮點特殊尋址模式支持,大幅減少翻譯代價,提升二進位翻譯程序的運行效率。

龍芯二進位翻譯解決方案的三大優勢:

- 高效

基於軟硬體結合的高效二進位翻譯技術,比傳統軟體模擬方式有數量級的性能提升。應用級翻譯實現對3D加速、視頻編解碼等功能的硬體支持。

- 兼容

跨指令集應用兼容運行,通過wine中間件可實現Windows到Linux的作業系統級別兼容,支持多平台應用在龍芯平台的運行。

- 自主

與龍芯自主指令集設計深度協同,通過持續優化改進翻譯器和指令集,實現更高效的翻譯與更廣泛的兼容性。

通過龍芯二進位翻譯系統,基於wine中間件技術,可以在龍芯平台上流暢運行常用桌面應用,如微信、Photoshop等等。

它還支持硬體加速,可加速音視頻、3D等應用場景,比如流暢運行CS等3D遊戲,後續還將不斷適配更多x86應用。

目前,龍芯二進位翻譯技術已經落地多個解決方案場景,比如龍芯辦公外設利舊通用解決方案(虛擬列印)。

來源:快科技

龍芯發布完全自主指令集架構LoongArch

上月,擁有MIPS指令集的Wave Computing轉投RISC-V陣營的消息引發關注。今天,MIPS生態的重要維護者龍芯也放棄MIPS指令系統,發布了完全自主指令集架構Loongson Architecture,簡稱龍芯架構或LoongArch。

龍芯委託國內第三方知名智慧財產權評估機構對龍芯基礎架構進行深入細致的智慧財產權評估。從2020年二季度開始,雙方投入上百人月,將LoongArch與ALPHA、ARM、MIPS、POWER、RISC-V、X86等國際上主要指令系統有關資料和幾萬件專利進行深入對比分析。

2021年1月,針對被評估的基礎架構版本該評估機構認為:

LoongArch在指令系統設計、指令格式、指令編碼、尋址模式等方面進行了自主設計。

LoongArch指令系統手冊在章節結構、指令說明結構和指令內容表達方面與上述國際上主要指令系統存在明顯區別。

LoongArch基礎架構未發現對上述國際上主要指令系統中國專利的侵權風險。

CPU指令系統是計算機的軟硬體界面,是CPU所執行的軟體指令的二進位編碼格式規范。一種指令系統承載了一個軟體生態,如x86指令系統和Windows作業系統形成的Wintel生態以及ARM指令系統和Android作業系統形成的AA生態。

無論是x86還是ARM指令系統,都需要獲得「授權」才能研製與之相兼容的CPU。採用授權指令系統可以研製產品,但不可能形成自主產業生態。

用個形象的比喻來解釋,中國人可以用英文寫小說,但不可能基於英文形成民族文化。這也就是擁有指令集的公司很容易就能對獲得授權的晶片設計公司卡脖子的原因,完全開源的RISCV,也是來源於美國伯克利大學,因此Loongson Architecture對中國集成電路產業而言是一個歷史性突破。

龍芯架構包括基礎架構部分和向量指令、虛擬化、二進位翻譯等擴展部分,近2000條指令,不包含MIPS指令系統,具有完全自主、技術先進、兼容生態三方面特點。

具體而言,龍芯架構從整個架構的頂層規劃,到各部分的功能定義,再到細節上每條指令的編碼、名稱、含義,在架構上進行自主重新設計,具有充分的自主性。

同時,龍芯架構摒棄了傳統指令系統中部分不適應當前軟硬體設計技術發展趨勢的陳舊內容,吸納了近年來指令系統設計領域諸多先進的技術發展成果。同原有兼容指令系統相比,不僅在硬體方面更易於高性能低功耗設計,而且在軟體方面更易於編譯優化和作業系統、虛擬機的開發。

生態方面,龍芯架構充分考慮兼容生態需求,融合了各國際主流指令系統的主要功能特性,基於龍芯團隊在二進位翻譯方面十餘年的技術積累創新,不僅能夠確保現有龍芯電腦上應用二進位的無損遷移,而且能夠實現多種國際主流指令系統的高效二進位翻譯。

龍芯2020年起新研的CPU均支持LoongArch架構。首款支持LoongArch架構的龍芯3A5000處理器晶片已成功流片,基於新架構的完整作業系統已經在3A5000計算機上穩定運行。同時,從其它主流指令系統到LoongArch的二進位翻譯系統已經可以在3A5000計算機上演示運行基於其它主流指令系統的復雜應用程式。

目前,龍芯中科已經在一定范圍內發布LoongArch的基礎架構指令系統手冊。待完成包括境外專利分析在內的進一步智慧財產權評估後,龍芯中科將在更大范圍內發布更完整的LoongArch指令系統手冊。龍芯中科還將聯合產業鏈夥伴在適當的時間建立開放指令系統聯盟,在聯盟成員內免費共享LoongArch及有關龍芯IP核。

來源:cnBeta

Arm發佈全新v9架構:新指令集、更大IPC提升、更強AI性能

Arm發佈了全新的v9架構,將會為移動裝置帶來光追以及可變速著色率、新的SVE2指令集以及更大的性能提升。根據Arm官方,新的v9架構將會至少使用10年,首批使用v9架構處理器的裝置將會在今年出現,未來兩代基於v9的處理器性能有望提升至少30%。

這次新加入的SVE2指令集,是Arm旗下Scalable Vector Extensions的最新版本,由富士通協助研發。如果大家還有印象的話,目前全世界第一、使用Arm架構處理器的超級計算機Fugaku正是由富士通打造的。Arm表示,新的SVE2指令集將會提升5G系統、AR/VR的,以及移動裝置上各種需要機器學習的任務處理效能,例如AI圖像質量提升等。說起AI,Arm在未來幾年也會為其Mali GPU以及Ethos NPU提供額外AI兼容性。

新的Arm v9架構也可以讓處理器的運算更加安全,因為v9將會包括一項名為「Realms」的概念,從Windows上的沙盒到手機上安全銀行應用等的虛擬環境,Realms都可以提供更好的保護。Arm更加表示,即便移動裝置的作業系統被攻破或者滲透了,Realms都依然可以繼續保護重要的數據數據。

在性能方面,Arm表示v9可以為兩代處理器合共提供至少30%的性能提升,因為這30%只是IPC方面的提升而已,如果使用Arm架構的廠家再自行調整頻率或者設計的話,處理器的性能提升就不只30%了。

Arm並沒有給出這些功能特性具體會在甚麼時候出來,但是認為未來將會有3000億個晶片用上v9架構。

來源:超能網

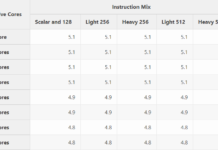

AVX512指令集終於滿血 11代酷睿8核穩定4.8GHz不降頻

與AMD處理器相比,Intel在高性能計算上有個殺手鐧,那就是AVX-512指令集,它可以讓浮點性能提升數倍,之前主要用於至強,現在10代酷睿移動版、11代酷睿移動、桌面版也開始支持。

然而,AVX-512指令集有個很尷尬的地方,那就是一旦使用了這個指令集,往往會因為功耗較高而導致CPU大幅降頻,他舉例說至強W-2104處理器在非AVX下頻率可達3.2GHz,AVX-512下就只有2.4GHz。

AVX-512指令集大降頻的問題在11代酷睿上似乎解決了,有網友測試了酷睿i9-11900K跑各種AVX指令集,包括128位、256位及輕度、重度512位下的CPU頻率。

從上面的結果來看,哪怕是負載最重的512位指令集下,11900K處理器1-4核下都能保持5.1GHz的頻率,5-6核下頁游4.9GHz,7-8核心下還有4.8GHz。

11900K處理器在ABT加速下最高可以做到8核5.1GHz,但實際使用中很考驗散熱條件,如今在AVX-512下都能做到8核4.8GHz,對比之前動不動就大幅降頻,這意味着AVX-512指令集終於可以滿血跑了,有助於這個指令集推廣。

作者:憲瑞來源:快科技

12nm、16核 龍芯3系列最新處理器即將出貨 引入自主指令集

來自統信軟件的消息,日前他們聯合龍芯中科副總裁張戈、倪光南院士等人舉行了一次小型會談,談到了國內的OS系統及處理器進展。龍芯中科副總裁張戈、高翔向倪院士匯報了龍芯產品最新進展,基於自主指令系統的龍芯3A5000/3C5000系列產品即將面世。 這是今年以來龍芯在公開場合確認新一代龍芯處理器上市的消息,去年龍芯董事長胡偉武表示將在2020年底上市新一代龍芯處理器,現在來看顯然是疫情耽誤了進度。

根據龍芯之前的消息,龍芯3A5000及龍芯3C5000系列處理器中,龍芯3A5000是新一代桌面處理器,採用12nm工藝,每芯片包含4核,主頻2.5GHz,單核性能達到30分左右。

龍芯3C5000是新一代服務器處理器,同樣採用12nm工藝,每芯片包含16核,支持4至16路服務器,具備高端服務器的商業競爭力。

2019年底,龍芯在北京推出了龍芯3A4000及龍芯3B4000處理器,使用與上一代產品3A3000/3B3000相同的28nm工藝,採用龍芯最新研製的新一代處理器核GS464V,主頻1.8GHz-2.0GHz,SPEC CPU2006定點和浮點單核分值均超過20分,是上一代產品的兩倍以上。

據胡偉武介紹,3A4000通用處理性能與AMD公司28nm工藝最後產品「挖掘機」處理器相當。

來源:cnBeta

Chrome將支持SSE3指令集,不支持的CPU將不能運行新版Chrome

Google Chrome准備放棄對沒有SSE3指令集CPU的支持,如果還有玩家是在用這些上古CPU的話,那麼或許現在會是一個更新(或者直接買新?)的契機。

SSE3(Streaming SIMD Extensions 3)是Intel基於SSE2發展出來的指令集,主要是增強了CPU在處理視頻編碼、線程同步、復雜算法等操作時的性能表現。SSE3最早是在Intel於2004年推出基於Prescott核心的Pentium 4 CPU上,而AMD也緊隨其後在2005年為Venice以及San Diego核心的Athlon 64新增了SSE3的子集。

從Chrome 89版開始,Chrome將不會在沒有SSE3指令集的Windows裝置上運行。如果用戶的計算機是不支持SSE3的話,那麼在嘗試運行Chrome 89版時會導致崩潰。

考慮到不支持SSE3指令集的CPU都已經至少有15年的歷史,Google認為受到這個決定影響的用戶數量是非常少的:

「我們的分析表明,目前只有非常少量運行Windows系統的裝置所使用的CPU是不支持SSE3的。」

不過即便是這樣,Google也會對於這部分用戶給予充足的提醒以及警告:

「直到我們實裝SSE3前,Chrome都會向受影響的用戶(用的x86 CPU不支持SSE3的)發出警告,提醒他們新版Chrome將不可以在他們的計算機上運行。這樣的警告是通過//chrome/browser/obsolete_system內的框架實現的,用戶會看到一個可關閉的警告窗口,另外在chrome://settings/help頁面內也會出現一個永久警告。"

這個警告將會是似類下圖這樣的。

更詳細的訊息可以在這里看到。 ...

RISC-V指令集處理器頻率已超5GHz 功耗僅Intel至強百分之一

十年前,一個想法誕生於加利福尼亞大學伯克利分校的一個實驗室中,他們創造了一種通用的計算機芯片語言,按照他們的設想,這套指令將被能所有芯片製造商所使用,而不屬於任何公司。

它本意不是想成為一種令人印象深刻的新技術,它只是希望可以使整個行業處於同一頁面上,以簡化芯片製造以推動發展。

但是,在邁向全球芯片標準的過程中發生了一件有趣的事情:正如伯克利所做的努力一樣,RISC-V已經開始在芯片設計方面產生一些技術突破。

僅舉一個例子,最近使用RISC-V的微處理器設計的時鍾速度已經達到5 GHz,遠高於最新的運行於3.2 GHz頻率的英特爾頂級至強服務器芯片E7。然而,新型RISC-V芯片在1.1伏特時僅消耗1瓦功率,還不到英特爾至強所消耗功率的百分之一。

RISC-V的速度和功率效率也超過了Exynos 4的規格,Exynos 4是三星電子為其智能手機生產的頂級產品,它基於英特爾主要競爭對手ARM Holdings Plc提供的計算核心。

加州大學伯克利分校的教授David Patterson在接受ZDNet采訪時說:「這真是太令人驚訝了。因為我認為IBM大型機具有5GHZ頻率的產品應該需要液冷,且耗電100瓦「。

令Patterson感到驚訝的是,技術創新正在興起。他說,「創新的潛力永遠存在」,但是當他和伯克利大學的同伴KrsteAsanović於2011年首次為RISC-V撰寫宣言時,這並不是他們主要的期望。

他說:「我認為將會發生的一件事是,因為它是開放的,我們將看到所有這些競爭。「

Patterson說:「也許是由於所有競爭,我們開始在設計領域看到一些真正有趣的觀點。」

這個新型的5 GHz處理器原型並不是由初創公司的創建。它是由硅谷知識產權設計公司Micro Magic Inc.製造的,該公司已經與所有大型硅谷公司進行了25年的合作。少量但經驗豐富的芯片設計人員完成這項任務的能力表明,設計復興可能即將到來。

嵌入式基準微處理器聯盟(Embedded Benchmark Microprocessor Consortium)記錄,該芯片不僅在功耗更低的情況下速度更快,而且在原始CPU性能的基準得分(稱為CoreMark)上的得分也高於英特爾和三星。RISC-V芯片的得分為13,000,是基於ARM的Exynos的每核性能得分的兩倍以上。

盡管Intel Xeon的每個內核名義上要高一些,為26,009,但Xeon部件需要更多的120個執行線程才能達到該性能。

長期擔任芯片行業高管的Andy Huang博士擔任Micro Magic的業務聯絡人。他在接受電話采訪時向ZDNet解釋說,突破在於CPU和記憶體交互的方式。Micro Magic的兩位創始人Mark Santoro和Lee Tavrow在90年代初獲得了SRAM計算機記憶體芯片的專利,這是有史以來最快的這種記憶體。

RISC-V原型消除了快速記憶體和慢速芯片可能存在的瓶頸。

「如果記憶體運行速度為5 GHz,邏輯運行速度為1 GHz,瓶頸在哪里呢?「 黃笑了笑,但沒有透露細節。

Huang說,關鍵在於,由於RISC-V是開放的,與英特爾芯片的復雜指令集架構甚至ARM芯片中的RISC版本不同,RISCV可以通過芯片設計來解決這一瓶頸。如果芯片的指令被鎖定,則不可能。

他使用的類比是Android與iOS。

「我問兒子為什麼比蘋果更喜歡三星(智能手機),他說這是因為如果他想要改變某些東西,他可以要求他的一位編程朋友為他做,因為Android是開放的,與iOS不同,」黃說。

Huang說:「這就是為什麼我們將所有成功歸功於Patterson博士的原因。「 「到目前為止,他創建了最高效,最優雅的RISC體系結構。」

黃說:「我們應該叫他SaintPatterson。「

修補指令集的能力僅僅是Micro...

《星際公民》升級要求AVX指令集 奔騰、賽揚團滅

太空模擬經營遊戲《星際公民》最近更新了Alpha 3.11版修正檔,正式要求處理器必須支持AVX指令集,才能啟動遊戲。

AVX指令集最早是在2011年的Intel Sandy Bridge二代酷睿、AMD Bulldoer推土機處理器上引入的,這意味着更早的一代酷睿、羿龍等處理器都無法再運行此遊戲。

更要命的是,Intel時至今日的所有奔騰、賽揚處理器,依然完全不支持AVX指令集,因此在《星際公民》面前,它們就集體撲街了。

這當然都源於Intel一貫的閹割技術劃分產品線的做法,不過消息顯示,Intel未來也會為更多處理器加入AVX指令集,比如說下一代低功耗架構Gracemont,就會支持AVX、AVX2、AVX-VNNI,它們就會用於奔騰、賽揚N/J系列,但不知道桌面的奔騰、賽揚何時支持。

AMD處理器目前則是全系支持AVX指令集。

很多依然在使用古董老平台、奔騰/賽揚入門平台的玩家紛紛抗議,但是考慮到《星際公民》是一款龐大的遊戲,對於CPU的需求也很高,官方這麼做並不意外,相信通過對AVX指令的優化,未來可以進一步提升遊戲性能。

同時,官方也沒有計劃為上述處理器創建AVX指令集的SSE兼容層。

- THE END -

轉載請註明出處:快科技

#Intel#CPU處理器#奔騰#賽揚#星際公民#指令集

責任主編:上方文Q作者:上方文Q來源:快科技

有問有答:AVX指令集是什麼?它的應用又有哪些?

很多讀者朋友可能在閱讀我們的文章時經常會看到AVX指令集這個名詞,比如說在CPU評測中就往往能夠看到它的身影,一些新入坑的玩家可能會不明白這個名詞的含義,今天這篇文章就簡單介紹一下該指令集的來龍去脈,並且梳理一下它目前在實際中的應用情況。

從SIMD說起

要搞明白AVX指令集的作用,首先要講明白它是什麼。定義很簡單,它就是x86處理器上面的一套SIMD指令集,是經典的SSE系列指令集的直接繼承者。那麼SIMD又是什麼呢?

在計算機剛剛出現的早期階段,馮·諾伊曼式計算機每次輸入一個指令只能夠操作一對數據,比如說"+,a,b"可以讓ab進行相加,這就是單指令流單數據流(Single Instruction Stream, Single Data Stream)。顯然,在面對大量數據的時候,這種操作數據的方法效率較低,程式設計師想要讓一次操作就對多組數據生效,怎麼辦呢?單指令流多數據流操作(Single Instruction Stream, Multiple Data Stream)的思路就被引入了,它讓輸入一次指令就操作多組數據變成了可能。

更直觀的區別可以看上面的示意圖。

上世紀八九十年代,很多處理器開發商都意識到了SIMD的前景,他們開始往自家的處理器里加入SIMD支持。1996年,Intel發布了基於新版P55C架構(最早一版Pentium處理器為P5架構)的Pentium MMX系列處理器,其中引入了新的MMX指令集,開始支持SIMD。

從MMX到SSE,再到AVX

Pentium MMX系列處理器上新引入的MMX指令集開創了x86處理器支持SIMD操作的先河,該指令集定義了8個64-bit寬度的寄存器,每個寄存器的64-bit容量中可以放入八個8-bit長度的整數或四個16-bit長度整數或兩個32-bit整數,CPU在識別到MMX指令集的新指令時會自動將寄存器中的數據進行分割計算,這樣一來,單個指令就成功操作了多個數據,實現了SIMD。

但MMX畢竟太嫩,它實際上是通過復用CPU內部x87浮點單元的寄存器來實現SIMD的,所以與運行浮點運算的x87指令集有衝突,兩者不能交叉使用,必須先進行切換。另外,由於上述的衝突,它只支持整數操作,在即將要到來的3D時代中顯得有些不夠用。

Intel當然很清楚MMX指令集的局限之處,而競爭對手新搗鼓出來的3DNow!指令集(1998年,AMD K6-2)已經支持了浮點SIMD運算,於是他們趕緊在經典的奔3處理器上面引入了新的SSE(Streaming SIMD Extensions)指令集,時間點為1999年2月份。

SSE指令集解決了MMX指令集身上存在的兩大問題,通過引入新的獨立寄存器解決了與浮點運算間的衝突問題,同時也就支持了浮點SIMD運算。當然它相對於MMX有很大加強,表現在它的寄存器寬度隨著處理器架構的進步而達到了128-bit,這樣一來一次SIMD指令能夠操作更多的數據,效率上有大幅度的提高。不過初代SSE指令集的單個寄存器只支持32-bit長度的浮點數,還是有很大的局限性,這個問題在Pentium 4(Willamette,2000年)上面引入的SSE2中被解決了,SIMD操作的靈活度高了很多。

隨後在約莫8年的時間里,Intel一直在更新SSE指令集,從SSE出到SSE4,AMD方面則是一直在跟進,到了SSE4.2,AMD開始想要在指令集上面尋找自己的翻身點,於是推出了只有自家支持的SSE4a子集,隨後更是提前於Intel提出了SSE5。

但Intel不干,我是x86的老大,我不能跟著你來。他們另起爐灶,准備在未來的Sandy Bridge架構中引入一套新的SIMD指令集,這套新指令集在2008年公布,被命名為高級向量擴展(Advanced Vector Extensions)。

革新的AVX,越來越寬的寄存器

相比起疊代了多年的SSE系列指令集,AVX指令集帶來了巨大的革新,其中最為主要的是,它在兼容SSE指令集性的同時,將SSE時代最大寬度為128-bit的寄存器拓寬到了256-bit。

不過初代AVX指令集還是比較保守的,它沒有將所有指令寬度拓寬到256-bit,而是選擇停留在128-bit上面。全面進入256-bit時代這個任務,還是交給了隨後的Haswell架構來完成(2013年6月份)。

同處理器用不同指令集的能效對比

但如果以為Intel會就此停下腳步的話,那就大錯特錯了,他們很快搗鼓出了更寬的AVX-512指令集,顧名思義,其寄存器寬度再次加倍,來到512-bit。

首個支持AVX-512指令集的處理器其實是Intel的Xeon Phi加速卡,首次跑到CPU上已經是Skylake-X系列了。而AVX-512也並不再是一個單一的指令集,它實際上指代的是多個指令集的集合,目前這個數字是17,之後可能還會增多。所有支持AVX-512的處理器都必須支持AVX-512 Foundation子集,從命名上也可以看出,它其實是AVX-512指令集的基礎。

長長的AVX-512子集列表

目前只有基於Skylake-Server和Ice Lake這兩個架構的處理器可以支持AVX-512(Cannon Lake死了,不然也算),使用門檻較高,一般新一點的應用也只是針對AVX2進行優化。

寬度越大,處理器的計算能力也就越強,尤其是在浮點運算方面,理論上提升有一倍之多,而實際應用中,如果優化得當,其提升幅度還要大一些。但是,新指令集在帶來性能增長的同時也帶來了另一個讓人感到頭痛的問題——功耗。

性能強了,峰值功耗也高了

AVX指令集在帶來更高性能的同時讓CPU的峰值功耗也變高了,可以通過下面的例子進行理解:

飛機發動機是按照最大起飛重量設計的,如果實際的載重沒有到最大起飛重量的話,飛行員就可以減推力起飛來降低油耗。CPU也是一樣的,最吃功耗的執行單元是根據最大寬度來設計的,平時用不到最大寬度的時候它的功耗就小了,而一旦用到極限,它也就會全開,此時CPU的功耗就上去了。

Intel...

Intel 10nm全線引入新指令集 緩存效率大漲

Intel今天公布了指令集擴展參考指南的第39個版本,透露未來的10nm家族將全線引入一個名為「CLDEMOTE「的新指令集,重點提升緩存效率與性能。

新指令集的全稱為「Cache Line Demont」,也就是「緩存行降級」的意思,可以讓操作系統告知一個處理器核心,如果緩存行里的特定內容不需要過於靠近處理器核心,就可以將其轉移到遠離核心的緩存內,但又不會推到系統主記憶體中。

也就是說,如果一級緩存里的某些數據不是處理器當前急需使用的,就可以轉移到二級乃至三級緩存;如果二級緩存里有類似的數據,就可以轉移到三級緩存。

這樣一來,一級、二級緩存的壓力就可以大大減輕,容量更小、距離處理器核心更近、速度更快的它們可以更高效地存儲更急需的數據。

另外,一二級緩存都是每個核心獨享的,三級緩存則是所有核心共享,將部分合適的數據放在三級緩存,其實更有利於多核心之間分享。

CLDEMOTE指令的支持范圍很廣,一個是Sapphire Rapids,也就是14nm Cooper Lake、10nm Ice Lake之後的再下一代數據中心至強,10nm工藝配新架構。

二個是Alder Lake,也就是Comet Lake、Rocket Lake之後的下下代桌面酷睿,也是10nm工藝,CPU架構預計為Willow Cove。

三個是Tremont架構核心,用於低功耗產品線,包括Atom凌動、奔騰、賽揚甚至是Lakefield這樣的混合封裝產品。

作者:上方文Q來源:快科技

Linux發行版Fedora開發人員討論提高系統基本要求:AVX2或成必需指令集

現代處理器中已經添加了很多擴展指令集,在很多應用中都會採用這些擴展指令集來提升性能。如我們常用的瀏覽器或視頻編碼等應用中都有用到。Linux發行版Fedora的開發者們現在也打起了擴展指令集的主意,他們正在討論在明年春季推出的Fedora

32的x86_64版本中啟用AVX2指令集,以提升性能。

最新的Ryzen 3000系列處理器已支持AVX2指令集

根據Phoronix的報導,Fedora的開發者正在討論提升系統的基本要求,以支持AVX2指令集。他們准備棄用不支持AVX指令集的處理器,同時系統將針對AVX2指令集進行優化來提升系統性能。

這對於Fedora發行版的用戶來說是一個喜憂參半的消息。Fedora發行版一直以來都是新技術的擁護者,這對於使用英特爾Haswall及以後處理器及最新的Rryzen

3000系列處理器的用戶來說是一個好消息,但對於使用較早處理器的用戶來講就很遺憾了,如此激進的更新會使得用戶無法使用最新的系統。

除了AVX2指令集外,Fedora的開發者們還打算支持FMA積和熔加等指令集,這也使得第一代和第二代Ryzen處理器能夠得到較好的支持。

在目前的郵件列表中有關AVX2指令集的爭論有很多,但如果Fedora工作組能夠為其軟體包做AVX2適配的話,這是一個非常具有指導意義的事情。大型軟體提升基本要求還是非常困難的,如常用的瀏覽器Chrome及Firefox也是在幾年前宣布從那以後的版本只支持SSE2指令的處理器。所以Fedora工作組這個舉動這會使眾多開源軟體加入新指令集的適配工作,讓更多的用戶體驗到這些指令集帶來的優勢,讓這些指令集不只在一部分軟體中使用。 ...

魔獸爭霸《CastleFight城堡戰爭》城堡指令集~~新手建主必備

<p火山地形

<p-nt-ntb-nc-skip-ni-balance-slb-fow180-rr2-envlava-lm

<p冰川地形

<p-nt-ntb-nc-skip-ni-balance-slb-fow180-rr2-envice-lm

<p具體解釋:

<p-AFK 暫離模式

<p-re 取消暫離模式

<p-m 鏡像模式

<p-r 隨即模式

<p-p 自選模式

<p-draw 平局要求。所有玩家輸入,此回合將重開

<p-armor 攻防表

<p-stats 當前形勢

<p-income 顯示收入

<p-boons 開啟信息提示

<p-noboons 關閉信息提示

<p-na 無炮火

<p-uo 純部隊

<p-nai 無空軍

<p-nafk 無暫離

<p-ns 無特殊

<p-ir 唯一模式

<p-ntb 無財寶箱

<p-nb 無獎勵金

<p-nc 無金幣

<p-cc 瘋狂金幣

<p-nt 無稅率

<p-ht 高稅率

<p-ni...