Tag: 4nm

AMD Zen5c架構巨變 三星4nm斜刺里殺出 與台積電3nm共舞

AMD將從明年起全年導入Zen5、Zen5c架構,包括桌面上的Granite Rapids、筆記本上的、伺服器上的Turin。

LinkIn上的AMD員工信息顯示,Zen5c架構的代號為“Promethus”,也就是普羅米修斯,古希臘神話中泰坦族的神明之一,父親是地母蓋亞與烏拉諾斯的兒子伊阿珀托斯,母親是名望女神克呂墨涅,曾與智慧女神雅典娜共同創造了人類。

更重要的是,Zen5c的代工工藝將同時包含台積電3nm、三星4nm(4LPP),這意味著AMD將採用雙代工模式,但具體如何分工暫不清楚。

媒體指出,AMD可能會讓三星試產或代工特定的IO晶片,但不太可能將重要的IP晶片交給三星。

三星為其Exynos手機處理器引入了AMD RDNA系列GPU架構授權,先後發布了RDNA架構的Exynos 2200、RDNA3架構的Exynos 2400,後續據說還有RDNA4架構的Exynos 2500。

雖然這些表現一般,但是三星和AMD的關系迅速升溫,拿下一部分代工也在意料之中,只是三星的工藝一直不讓人放心,AMD肯定有所保留。

畢竟過去這幾年,AMD一直依賴台積電,後者穩定、強大的工藝也是AMD取得今日成功的關鍵。

回顧一下歷代Zen架構代號:

Zen 2 (7nm) – Valhalla(英靈殿)

Zen 3 (7nm) – Cerberus(刻耳柏洛斯,古希臘神話地獄三頭犬)

Zen 4 (4/5nm) – Persephone(珀耳塞福涅,古希臘神話冥後)

Zen 4c(4/5nm) - Dionysus(狄俄尼索斯,古希臘神話酒神)

Zen 5 (3/4nm) –...

三星:我們將擊敗台積電 率先為美國奉上4nm

台積電、三星這兩年紛紛加大投資力度,在世界各地興建新的先進晶圓廠,尤其是美國,三星更是信心膨脹。

三星聯系CEO慶桂顯(Kyung Kye-hyun)在一次演講中表示,三星對於在美國德克薩斯州的新廠十分看好,計劃在2024年底投入量產,可生產一系列4nm級別工藝的晶圓,包括SF4E、SF4、SF4P、SF4X、SF4A。

台積電在美國亞利桑那州的Fab 21,同樣規劃了4nm工藝產線,但量產時間已經跳票到了2025年。

台積電聲稱是美國工人不熟練,耽誤了進度,但美國工人和工會堅決否認。

如果一切順利,三星無疑將給台積電予以相當的壓力,也會沖擊Intel——後者計劃2024年做好20A、18A工藝的投產准備。

根據集邦咨詢的統計,2023年第二季度全球代工市場上,台積電以56.4%的份額遙遙領先,不過環比丟掉了3.8個百分點,三星則收獲1.8個百分點來到了11.7%。

另外,格芯6.7%、聯電6.6%、中芯國際5.6%、華虹3.0%、高塔半導體1.3%,都略有增長或維持穩定。

來源:快科技

4nm Zen4+最強核顯還得等 AMD銳龍7040HS筆記本跳票到4月

年初,AMD一口氣發布了,其中基於老架構的銳龍7035H/U、銳龍7030U、銳龍7020U都已經陸續有產品上市,Zen4架構的銳龍7045HX、銳龍7040H/HS/U卻有點慢。

尤其是在13代酷睿HX、H系列筆記本已經滿天飛的情況下,AMD更讓人等得心焦。

銳龍7045HX高端遊戲本最初承諾2月上市,但是現在才開始上架,ROG魔霸7 Plus系列首發,其中標準版使用銳龍9 7845HX,超能版使用銳龍9 7945HX。

銳龍7040HS筆記本最初的計劃是3月上市,不過據媒體報導,AMD官方確認,第一批基於銳龍7040HS系列的筆記本將在4月份上市。

至於推遲原因,AMD解釋說是平台需要進一步做好准備,並確保最佳的用戶體驗。

銳龍7040HS系列可以說是整個新家族中最為先進的,擁有4nm工藝、Zen4 CPU架構、RDNA3 GPU架構,並首次在x86處理器中集成AI引擎,基於XDNA適應性架構,此外還支持USB4高速接口。

尤其是核顯部分,新一代Radeon 780M集成了多達12個CU單元(768個流處理器),頻率一度最高達3GHz,後來降到2.8GHz。

但是即便如此,,泄露跑分顯示已經基本和移動版GTX 1650 Ti在同一檔次,配置和優化到位甚至能逼近RTX 2050。

如今新平台被推遲,猜測可能就是為了繼續做好新架構尤其是新核顯的優化適配工作。

同時,銳龍7040系列還有中國市場特供的銳龍7040H系列,規格一致,功耗更加開放,以及一直未官宣的銳龍7040U系列,已經泄露的泄露的有、。

來源:快科技

沉寂兩年 AMD桌面APU歸來了 升級4nm Zen4架構、AM5接口

AMD的桌面APU有段時間沒更新了,雖說這一代Zen4銳龍破天荒地集成了GPU單元,一定程度上搶了APU飯碗,但那顆集顯不過是亮機級別。

根據一份最新爆料,AMD正在准備三種架構的桌面APU新品。

其中最讓人期待的莫過於Zen4架構、AM5接口的型號,某種程度上和4nm Phoenix(移動版銳龍7040)共享設計。

有趣的是,Zen3和Zen3+居然也要被包裝成AM5接口,被抬升到桌面平台,後者原型就是6nm Rembrandt移動APU。

三套APU均會支持DDR5記憶體,但PCIe通道數不同(PCIe 5.0均被砍掉),集成的GPU定位也各有高低。同時,外圍支持方面,僅4nm Zen4會有原生USB4。

考慮到銳龍5000G(代號Cezanne塞尚)已經是2021年的產品了,AMD的確是時候做出更新。

來源:快科技

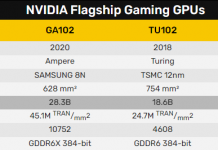

NVIDIA 4nm RTX40顯卡將有750億電晶體 2.65倍於8nm RTX30

NVIDIA RTX 40系列就要來了,不出意外會用上台積電N4 4nm工藝,在技術上可比三星N8 8nm強太多了。

權威博主kopite7kimi曝出最新猛料,RTX 40系列的大核心AD102,要用於RTX 4090、RTX 4090 Ti的,將會集成多達750億個電晶體!

這幾乎要媲美加速計算用的GH100核心了,後者也是台積電4nm工藝,集成多達800億個電晶體,AD102隻差區區50億個。

另外,RTX 30系列大核心GA102集成了283億個電晶體,AD102是它的多達2.65倍,是近年來增幅最大的一次。

再往前,12nm TU102 186億個,12nm GV100 211億個,16nm GP102 120億個,它們的密度都是2500萬個/平方毫米,GA102大幅增加到了4510萬個/平方毫米。

AD102核心集成18432個CUDA核心,相比GA102增加約71%,顯存規格基本不變,不知道這麼多電晶體都用在了哪里。難道有秘密武器?

現在的懸念就看AD102核心的面積有多大、集成度有多高了。

GA102

來源:快科技

5nm假冒4nm?三星、台積電撒了彌天大謊?

許多人偶爾會謊報自己的年齡或體重,這可能並不是什麼大問題。但是,如果企業出現了類似的謊報行為,則可視為虛假廣告,是在欺騙用戶。

據芯智訊收到的一份據稱半導體研究機構TechInsights的報告(我們沒有購買TechInsights的會員,因此無法進一步查證),現在的半導體市場就出現了這種“謊報”的行為,兩家領先的代工廠都放任客戶聲稱他們採用了4nm工藝,而實際使用的卻仍是5nm技術。這種情況讓雙方均形象受損,尤其是代工廠。

這背後,也意味著電晶體微縮技術發展的放緩。

報告稱,這個問題最初始於三星。

在與台積電下一個節點的長期競爭中,三星在交付5nm晶片的一年後,宣布將於2021年底交付生產4nm晶片。

如圖1所示,台積電計劃在5nm和4nm節點之間用兩年時間,在2022年第2季度交付4nm。

為了避免給三星“耀武揚威”的機會,台積電決定將其N4(4nm)節點的進度“拉快”兩個季度,以恰巧趕上競爭對手。

首個使用台積電N4工藝的晶片是聯發科的天璣9000系列。

△圖1:經修訂的製程工藝路線圖。台積電聲稱已在2021年末交付了4nm節點,只是當時誤標為5nm技術而已。

台積電可以突然從其通常嚴格而耗時的生產認證周期中足足擠出六個月的時間,對於這一點,我們本就應該感到懷疑。

當TechInsights分析天璣9000並發現關鍵工藝尺寸與台積電早期N5產品完全相同時,情況就不妙了。顯然,台積電聲稱的4nm產品是虛假的,正如聯發科技聲稱擁有4nm處理器一樣。

與此同時,三星的智慧型手機部門正准備推出Galaxy S22,該機型部分搭載了三星自有的Exynos 2200處理器,宣稱採用4nm技術製造,但高通的驍龍8 Gen 1(出現在一些S22型號內)採用的是5nm技術製造。為避免客戶對一種處理器(較於另一種處理器)在製程工藝上領先的渴望,兩家公司決定將8 Gen 1作為4nm晶片推出。

因為三星生產這兩種產品,所以它創造了一種稱為4LPX的新工藝,像N4一樣,但只為一種產品服務。

TechInsights在分析了驍龍晶片後,發現三星4LPX工藝在物理上與其5LPE工藝並沒有什麼不同。

但頗為諷刺的是,唯一使用真正4nm技術的產品比假冒的4nm產品表現更差。因為,三星在將其4LPE工藝投入生產方面過於冒進,導致Exynos 2200高缺陷率和低能效——特別是在其新的圖形引擎中。

由於Exynos晶片供應有限,三星電子在大多數Galaxy S22型號採用了高通驍龍8 Gen1處理器。

這些生產困境進一步促使高通轉向採用台積電N4P工藝代工其新一代的旗艦處理器驍龍8+ Gen 1。

TechInsights認為,台積電N4P才是真正的4nm技術。驍龍8+ Gen 1是首個公開的台積電N4P工藝產品,預計蘋果A16也將會使用N4P代工。

這兩種晶片都已經投產,蘋果A16並將在9月份左右應用於新一代的iPhone 14系列手機。

台積電通常會給蘋果一到兩個季度的獨家使用權來使用其最新的製造技術。看到高通出現在首批客戶名單上令人驚訝,尤其是考慮到其基於驍龍的智慧型手機與蘋果的iPhones直接全面競爭。

台積電顯然願意打破蘋果的獨家地位,以便從三星手里奪取一項主要設計。(高通在許多其他產品上有選擇台積電代工,但過去幾款旗艦處理器都是基於三星產品製造的。)

真相很難面對

為什麼代工廠突然虛報其電晶體進展情況?這比承認進展遇阻要容易得多。

假冒的4nm工藝和“真正”4nm工藝之間的區別僅僅在於5%的光學微縮(10%的面積縮減)。即使是這小小的進步也打破了三星的產量模型,台積電也是花了兩年時間才完成。

這兩家頭部的代工廠預計明年將實現3nm的大規模量產,而盡管他們在4nm工藝方面奮力掙扎,卻未能激發出多少信心。

考慮到節點之間的間隔時間較長,代工廠可能會在等待下一個節點的同時提高速度、功率或產量(最終達到相同的效果)。

例如,雖然三星的4LPX與5LPE工藝具有相同的尺寸,但前者可能會提供一些其他優勢來證明其有資格獲得新名稱,只是在電晶體密度沒有任何提高的情況下,名稱應採用5LPX,以表明該工藝仍然屬於5nm節點的范疇。

大多數人用5nm或4nm的簡寫來代替完整的工藝名稱,所以數字還是很重要的。

盡管偽造新節點可以讓代工廠擺脫短期困境,但這對他們來說是有害的。

吹捧一個假冒的4nm里程碑並放任客戶大肆宣傳,會稀釋代工廠品牌的價值。

如果4nm不是真正的4nm,那麼節點名稱還有意義嗎?如果可以重新命名一個較舊的工藝,為什麼消費者要為4nm技術承擔額外的成本呢?

一段時間以來,代工廠沒有在節點數量和電晶體密度之間保持嚴格的相關性,但至少當他們在名稱中採用一個更小的nm數字時,就表明其已取得了一些密度方面的進步。

公然將一個5nm工藝重新標記為4nm,則抹殺了節點編號的最後一絲意義。

所以,當某個代工廠宣稱其已達到下一個新水平的時候,直到拆解確認前,請切勿輕信。

同樣的道理也適用於那些吹噓自己實現新製造技術的晶片供應商。隨著摩爾定律磕磕絆絆走到盡頭,最後留給我們的唯有謊言、該死的謊言以及那些毫無意義的節點名。

關於製程工藝節點的數字遊戲早在多年前就已經開始。原本半導體產業界一直遵循著每一個大的代際的製程節點更新,都是以前一代製程的0.7倍對新製程節點命名,同時每一個大的代際升級,其電晶體密度將是上一代的兩倍。

比如Intel90nm、65nm、45nm、32nm、22nm這樣的命名,基本是遵循每兩年升級一代,電晶體數量翻一倍的規則。

但是自2011年下半年Intel發布了22nm之後,近2年半之後,即2014年上半年,Intel的14nm工藝才發布(二季度末才量產)。而在14nm向10nm提升的過程中,Intel在工藝上遭遇了挑戰,其Tick-Tock策略(即一年提升工藝,一年提升架構)甚至停擺。

雖然2014年Intel就推出了14nm工藝,之後僅一年不到的時間,三星也搶先台積電推出了自家的14nm工藝,當時台積電宣布量產的是16nm工藝。這也使得三星順利奪下了蘋果A9處理器的訂單。

但實際上,這只不過是三星的為爭奪市場而採取的製程數字上的營銷策略。之後的事實也證明,當時三星14nm工藝的性能甚至不如台積電的16nm工藝,這也是為什麼蘋果在A9之後又全面轉向了由台積電獨家代工。

即便台積電並沒有像三星那樣激進的玩“製程工藝數字的虛假遊戲”,但是台積電也絕不是旁觀者!因為台積電和三星對於工藝節點的命名,都不是像Intel那樣嚴格按照最初的命名規則來命名。

根據此前Intel公布的數據顯示,其2014年推出的14nm製程所能達到的電晶體密度已經與三年後(2017年)台積電、三星所推出的10nm的電晶體密度相當。

Intel的10nm製程工藝雖然比三星、台積電的10nm工藝推出時間略晚,但是它的電晶體密度卻達到了後者的兩倍。

此外,Intel 10nm的鰭片間距、柵極間距、最小金屬間距、邏輯單元高度等指標均領先於台積電和三星的10nm。

但是,對於大多數商用客戶及消費者來說,並不會去深究各家製程工藝的實質差別,通常都會認為製程工藝節點的數字越小,就代表著越先進。這也使得三星、台積電在“製程節點命名的遊戲”上越玩越嗨,並且憑此也贏得了市場的領先!

相比之下,“守舊”的Intel卻像個“祥林嫂”,一直在那說“我的是10nm相當於競品的7nm”,“我的電晶體密度更高”,“競品在工藝節點數字上的領先,並不是真正的領先”!但是,在消費者看來,Intel在工藝節點數字上的落後是“真的落後了”。

為了徹底扭轉這一局面,在Intel新CEO基辛格加入之後,很快就選擇了“打不過就加入”的策略,也開始玩起了“製程節點命名的遊戲”,徹底打破了堅守了數十年的命名規則,直接採用“Intel X”的命名方式,來與台積電的製程工藝節點一一對應。比如原本的Intel10nm工藝被重新命名為了Intel 7,對應台積電的7nm工藝。

雖然現在大家都在玩“製程節點命名的遊戲”,但是基本上都是針對競爭對手,對於自家的產品,仍一直都是遵循製程工藝節點數字越小,越先進的命名規則。

如果TechInsights的分析無誤的話,那麼三星、台積電跟客戶一起“編造製造工藝的謊言”,拿“5nm”來冒充“4nm”無疑是太過分了。這也將使得製程工藝節點的命名,完全失去了應有的意義。

來源:快科技

驍龍8都被坑 三星終於搞定4nm良率:加速追趕台積電

在先進工藝上,三星跟台積電一度是臥龍鳳雛,然而台積電在4nm節點穩多了,三星的4nm良率就出問題,之前傳聞只有35%,導致高通的驍龍8處理器都跟著被坑,驍龍8+換到台積電4nm之後功耗降低了30%。

此前三星否認過良率過低的問題,表示5nm工藝已經進入成熟階段,還在擴大服務,4nm工藝雖然良率提升過程出現了延遲,但已經進入了預定的良率曲線,未來的3nm工藝還在准備設立一條新的研發生產線。

現在又是2個月過去了,三星改善4nm良率似乎是真的,韓國媒體報導三星已經決定增加5萬億韓元的投資,約合人民幣258億元以提升4nm產能,月產能將增加1.5萬片-2萬片晶圓,希望從台積電手中搶奪更多的訂單。

三星之所以敢於增加投資,主要是4nm良率大改,雖然官方沒公布數據,但傳聞已經提升到了60%,也就是10片晶圓中有6片是符合要求的,這個良率雖然還不是最好的,但相比之前傳聞的35%已經是天差地別,至少能保證產能了。

三星最近兩個月雖然量產了3nm GAA工藝,但是該工藝是不可能完全滿足市場需求的,所以4nm工藝未來幾年還會是重點,提高良率、增加產能依然有空間。

來源:快科技

等等黨勝利 AMD Zen 4架構的新一代遊戲機來了

除了任天堂,AMD的晶片方案已經被索尼、微軟以及Valve的遊戲選用。

爆料達人MLID給出消息稱,AMD正在開發一款全新的遊戲機晶片,從浮出水面的規格來看,目標似乎是下一代Steam Deck。

新U處理器部分採用Zen 4架構,4核8線程設計,GPU部分則升級到RDNA3,這樣來看的話就是AMD 4nm移動APU產品,代號「Phoenix Point」。

目前已經開售的Steam Deck掌機採用的是AMD定製Van Gogh家族低功耗APU,CPU架構是Zen 2,GPU是RDNA2,晶片紙面性能大致等價銳龍3 Pro 4450U+MX450,可流暢運行最新的3A大作。

按照AMD的說法,RDNA3每瓦性能比RDNA2高出50%以上。

來源:快科技

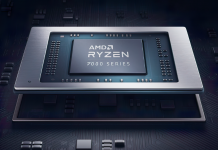

AMD首顆4nm Zen 4銳龍APU處理器現身 RDNA3 GPU完美了

隨著Zen 4銳龍7000處理器原生集成GPU,至少在桌面市場,未來的APU大機率會沉寂一段時間。不過,移動端則正好相反。

事實上,根據AMD發布的路線圖,在筆記本平台,Zen 4和Zen 5 APU都有著明確規劃,分別代號Pheonix Point、Strix Point,其中Pheonix Point明確會是4nm工藝。

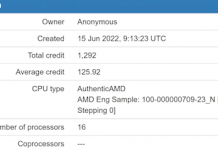

經查,在MilkyWay@Home頁面出現了疑似AMD Zen4 APU的身影,OPN部件號100-000000709-23_N,對應Family 25 Model 112 Stepping 0,此前從未見過。

其它方面,識別出來8核16線程配置。

當然,需要指出的是,Zen 4對應的筆記本APU產品其實不只是Pheonix Point,還有Dragon Range,兩者的區別在於前者用於輕薄本,後者則是遊戲本,顯然它們的性能、頻率、核心配置、TDP等將來會有明顯區別。

關於Zen4 APU,其它值得一提的特性還有,集成RDNA3 GPU,還有AIE單元也就是人工智慧加速模塊。

至少就GPU而言,Zen4 APU的看點更大,畢竟桌面銳龍7000隻有可憐的2CU單元,而且還是RDNA2。

來源:快科技

性能猛增35% Intel公開」4nm「 EUV工藝性能:CPU頻率沖擊6GHz?

根據Intel的晶片工藝路線圖,到2025年之前他們要在短短4年內掌握5代CPU工藝,其中有2代還是首次進入埃米級工藝,今年下半年將要量產Intel 4工藝,也就是對標友商的」4nm「工藝,也是Intel首款使用EUV光刻機的工藝。

目前台積電、三星已經量產了4nm工藝,不過Intel自家的」4nm「工藝還是有不少特色的,特別是在性能方面,其他兩家主要生產低功耗晶片,Intel則是要生產高性能處理器,包括桌面及伺服器級別的。

Intel的這個」4nm「工藝比目前的Intel (也就是沒改名前的第二代10nm工藝)工藝每瓦性能提升20%,如果是對比之前的初代10nm工藝,那麼性能提升超過35%。

其他方面,Intel 」4nm「工藝的電晶體密度相比Intel 7工藝提升100%,HP高性能庫密度可達1.6億電晶體/mm2,高於台積電5nm工藝的1.3億電晶體/mm2,接近台積電未來的3nm工藝的2.08億電晶體/mm2水平了。

目前Intel 7工藝量產的12代酷睿及下半年的13代酷睿頻率可以做到5.5GHz了,假設性能也只是提升20%,那極限頻率應該可以突破6GHz了,史無前例的水平,不知道Intel會不會這麼做。

Intel 4工藝會在明年的14代酷睿Meteor Lake上首發,後者也會是Intel酷睿系列中首個大量使用3D Foveros混合封裝的處理器,主要有三個部分封裝在一起,一是計算模塊,二是GPU模塊,多達96-192個計算單元,三是SoC-LP,應該是包含記憶體控制器、PCIe控制器等輸入輸出部分。

來源:快科技

逆襲AMD的節奏 NVIDIA豪橫:RTX 40系顯卡升級台積電4nm

RTX 30系顯卡停留在老邁的「8nm」工藝,說白了就是10nm改良版。雖然產品力依然夠強勁,但不免落友商「口實」。

對於NV來說,肯定不是買不起這樣的工藝,更在乎的是產能和良率能不能達標。看起來,台積電的4nm得到老黃歡心了。

爆料人MILD指出,Lovelace的確是4nm工藝。所謂Lovelace就是RTX 40系顯卡核心代號Ada Lovelace,歷史上是詩人拜倫的女兒。

由於AMD RX 7000系列顯卡預計會是5nm工藝,看起來NVIDIA要在名義上占點便宜。

另外,爆料稱,4nm針對NVIDIA的產品做了定製優化,估計和天璣9000用的那套略有不同。事實上,去年12月台積電曾官宣N4X製程,說是專門為高性能運算開發,可實現5nm家族的最高性能與最大頻率。

指標方面,N4X的性能比N5提升15%。對比N4P,在1.2V下性能也提升了4%。不過,N4X當時說是2023年上半年才能試產,從這個角度來看,有點跟不上。

來源:快科技

重大突破 清華大學首次實現亞1nm柵極電晶體:等效0.34nm

,集成電路學院任天令教授團隊在小尺寸電晶體研究方面取得重大突破,首次實現了具有亞1納米柵極長度的電晶體,並具有良好的電學性能。

據清華大學介紹,目前主流工業界電晶體的柵極尺寸在12nm以上,日本中在2012年實現了等效3nm的平面無結型矽基電晶體,2016年美國實現了物理柵長為1nm的平面硫化鉬電晶體,而清華大學目前實現等效的物理柵長為0.34nm。

圖1 亞1納米柵長電晶體結構示意圖

官網介紹,為進一步突破1納米以下柵長電晶體的瓶頸,本研究團隊巧妙利用石墨烯薄膜超薄的單原子層厚度和優異的導電性能作為柵極,通過石墨烯側向電場來控制垂直的MoS2溝道的開關,從而實現等效的物理柵長為0.34nm。

圖2 隨著摩爾定律的發展,電晶體柵長逐步微縮,本工作實現了亞1納米柵長的電晶體

通過在石墨烯表面沉積金屬鋁並自然氧化的方式,完成了對石墨烯垂直方向電場的屏蔽。再使用原子層沉積的二氧化鉿作為柵極介質、化學氣相沉積的單層二維二硫化鉬薄膜作為溝道。具體器件結構、工藝流程、完成實物圖如下所示:

圖3 亞1納米柵長電晶體器件工藝流程,示意圖,表徵圖以及實物圖

研究發現,由於單層二維二硫化鉬薄膜相較於體矽材料具有更大的有效電子質量和更低的介電常數,在超窄亞1納米物理柵長控制下,電晶體能有效的開啟、關閉,其關態電流在pA量級,開關比可達105,亞閾值擺幅約117mV/dec。大量、多組實驗測試數據結果也驗證了該結構下的大規模應用潛力。

基於工藝計算機輔助設計(TCAD)的仿真結果進一步表明了石墨烯邊緣電場對垂直二硫化鉬溝道的有效調控,預測了在同時縮短溝道長度條件下,電晶體的電學性能情況。

這項工作推動了摩爾定律進一步發展到亞1納米級別,同時為二維薄膜在未來集成電路的應用提供了參考依據。

圖4 統計目前工業界和學術界電晶體柵極長度微縮的發展情況,本工作率先達到了亞1納米

上述相關成果以「具有亞1納米柵極長度的垂直硫化鉬電晶體」(Vertical MoS2 transistors with sub-1-nm gate lengths)為題,於3月10日在線發表在國際頂級學術期刊《自然》(Nature)上。

來源:快科技

三星5/4/3nm工藝拉胯:竟有人偽造良品率

相比於台積電,三星的製造工藝一直差幾個檔次,其代工的NVIDIA RTX 30系列顯卡、高通驍龍8系列處理器,甚至是自家的Exynos 2200手機晶片,無論性能還是能效頗受詬病。

據DigiTimes報導,三星電子現在陷入了一樁丑聞,部分在職員工、前員工涉嫌偽造和虛報5nm、4nm、3nm工藝製程的良品率。

據悉,三星在批准5nm、4nm工藝的量產計劃後,無論是三星自己,還是第三方晶片代工客戶,都發現良品率明顯低於預期。

為此,三星已經開始對負責代工業務的三星設備解決方案(Samsung Device Solutions)事業部進行初步調查,包括相關投資是否使用到位。

不過三星強調,該問題影響並不嚴重,具體結果將在調查完成後公布。

就在日前,還有消息稱,台積電3nm工藝的良品率也存在問題,不得不多次修改路線圖。

據稱,蘋果、高通、Intel、AMD等都是台積電3nm工藝的客戶,其中高通將拋棄三星代工,全面轉向台積電,Intel則是首次引入台積電代工服務。

來源:快科技

台積電宣布推出N4X製程 5nm終極增強版:性能提升15%

據台積電官網,公司今日(12月16日)宣布推出N4X製程,號稱將代表5nm家族所具備的最高性能與最大頻率。

後綴「X」系台積電先進位程首次使用的後綴,代表Extreme,寓意為高性能運算專門開發,實際上這也是台積電第一個專門服務高性能運算的製程技術。

N4X在台積電定義中應該是4nm,不過台積電還算老實,使用的是5nm家族的說法,也就是承認它實際上是5nm強化版。

微觀結構方面,台積電N4X優化了支撐高驅動電流及最大頻率的元件設計和結構、對後段金屬製程優化、支持極限負載下傳送大功率的超高密度金屬電容等。

指標方面,N4X的性能比N5提升15%。對比N4P,在1.2V下性能也提升了4%。

據台積電介紹,N4X可以支持高於1.2V的驅動電壓,從而輸出更高性能。N4X與N5設計套件一致,配合3DFabric封裝技術還能擁有更好表現。

據悉,N4X將於2023上半年進入試產。

遺憾的是,台積電並未披露N4X的主要客戶,理論上說AMD、Intel、高通、IBM等都有可能,畢竟除了伺服器CPU、GPU,前兩者還有FPGA產品可以上馬。

來源:快科技

台積電宣布N4P高性能工藝:4nm?其實又是5nm

台積電今天宣布了一個新的製程工藝節點「N4P」——看起來是4nm,但其實是5nm的又一個版本,確切地說是N5、N5P、N4之後的第四個版本、第三個升級版,注重高性能。

台積電稱,N4P工藝相比最初的N5工藝可提升11%的性能,或者提升22%的能效、6%的電晶體密度,而對比N4可將性能提升6.6%。

此外,N4P工藝會重復使用多層遮罩,因此可大大降低工藝復雜度,加快晶圓生產速度。

台積電稱,N4P工藝是為客戶5nm工藝平台產品升級准備的,不但可以最大化挖掘投資價值,還可以更快、更高效地升級N5工藝產品。

台積電表示,第一款基於N4P工藝的產品預計2022年下半年流片。

台積電此前披露,N3 3nm工藝將在今年內風險性試產,2022年下半年大規模量產,2023年第一季度獲得實際收入,N3E 2024年量產,

來源:快科技

驍龍 898 和天璣 2000 樣片參數曝光:都是 4nm、 三叢集

隨著時間的推移 ,2021 年馬上就要進入尾聲,而對於數碼領域,尤其是手機類別來說卻意義重大,因為各家的旗艦晶片疊代版就要來了。

前段時間,蘋果已經率先通過 iPhone 13 等產品展示了最新的 A15 自研晶片,依然是強無敵的性能,日前Google同樣發布了首款自研手機晶片 Tensor, 重點放在了 AI 等方面,性能有些拉垮。 不過,以上兩款晶片基本都是自家獨享的晶片,而真正備受關注的還是高通和聯發科旗下的旗艦產品——驍龍 898、 天璣 2000。按照此前消息,驍龍 898 將會在 12 月中旬正式亮相,而天璣 2000 將會在明年初登場,兩者上市時間非常相近,同時參數上也非常類似。

今天上午,知名爆料博主@數碼閒聊站曝光了這兩者的樣片參數,具體如下:

驍龍 898: 三星...

10nm終於成功 Intel的14nm七年後不癢了

Intel今天發布了2021年Q2季度財報,營收超過預期、PC業務大漲的同時還有技術上的好消息,現在的10nm工藝成本降低了45%,並且產量也超過了14nm工藝,用了7年的14nm有望退居二線了。

Intel在2014年的Broadwell處理器首發14nm工藝,按照之前2年升級一次的節奏,本應該在2016年升級10nm(最初應該是2015年,因為14nm也跳票一年),然而10nm工藝難產,14nm就一直擔當主力到今年,7年之癢了。

10nm工藝遲遲無法量產的問題在於成本高,根源則是良率低,因為在10nm工藝上Intel用了很多新技術,包括SAQP四重曝光、鈷局部互連、有源柵極上接觸(COAG)等等,導致良率上不去,晶片成本降不下來,不能大規模量產。

Intel在2019年才搞定了10nm工藝的量產,推出了Ice Lake處理器,2020年推出了Tiger Lake處理器,升級到了第二代的10nm SF工藝,現在的成本已經降低了45%,意味著良率有了很大的提升,生產不是問題。

得益於此,Intel的10nm工藝產能也超過了14nm工藝,成為Intel新一代主力,今年底會推出10nm工藝的Alder Lake處理器,這次桌面版也會同步升級,這也意味著10nm工藝產能的勝利。

來源:遊民星空

消息稱台積電將為Intel專建晶圓廠 8000人伺候4nm工藝升級

Intel今年1月份會公布一件大事,那就是有關芯片工藝外包的選擇問題,這件事傳聞已久,台積電、三星都有可能成為Intel的合作夥伴。

在外包這個問題上,Intel之前公布了三個原則——Intel的目標是尋找對產品競爭力最佳的解決方案,不論是內部還是外部,要全面評估成本、良率及生產彈性等問題。

那Intel會選擇哪種代工方案呢?外媒日前報道了一種選擇,台積電給Intel提供了4nm工藝代工,不過初始階段會採用5nm工藝做測試——台積電的4nm工藝是基於5nm改進的,二者設計上是兼容的。

據悉台積電的4nm工藝今年Q4季度就會試產,2022年大規模量產。

考慮到Intel的需求,一旦選擇了台積電代工,那麼產能會很龐大,台積電目前在寶山建設一座新的晶圓廠,未來可容納8000多名工程師,一旦需要的話,這個工廠就可以專為Intel服務。

從Intel CEO司睿博之前的表態來看,2022年是關鍵一年,因為屆時Intel的處理器不論工藝還是架構都會有很大的變化,從十二代酷睿Alder Lake開始,Intel會引入大小核設計,未來Intel的CPU製造會有代工及自產兩種路線,不同工藝+不同IP核心的小芯片組合可以靈活適應Intel的需求,畢竟大核心、高性能工藝是不可能扔掉的。

作者:憲瑞來源:快科技

台積電宣布4nm工藝 5nm加強版、2023年量產

台積電、三星這幾年在新工藝方面非常激進,但相比於Intel的「老老實實「,14nm再怎麼優化加強也叫14nm,這兩家就有點跳躍了,某代工藝強化一下就是新一代。

台積電CEO劉德音在今天的股東大會上宣布,台積電將會推出4nm工藝「N4」,是其最先進5nm工藝「N5P」的進一步加強版,預計2023年投入量產。

台積電顯然在重復6nm工藝N6的老套路,它就是最強7nm工藝N7+的升級版,好處是在性能、功耗繼續優化的同時,設計上彼此兼容,客戶可以輕松遷移,以較低的成本獲得更好的芯片,還有新工藝的光環加持。

台積電這種套路是從16nm開始的,當時還嚴格遵從技術標準,但是三星類似的工藝叫做14nm,從紙面上看台積電就落後了,於是把16nm加強升級一下,推出了12nm,從此就一發不可收拾……

根據規劃,台積電將在今年第四季度量產初代5nm,同時已完成3nm工藝的設計工作,預計2021年上半年投入試產,還在加快推進2nm工藝。

作者:上方文Q來源:快科技

三星的6nm、5nm、4nm工藝都是7nm改良 3nm棄用FinFET

7nm工藝的產品已經遍地開花,Intel的10nm處理器也終於在市場登陸,不過,對於晶圓巨頭們來說,製程之戰卻越發膠着。

在日前一場技術交流活動中,三星重新修訂了未來節點工藝的細節。

三星稱,EUV後,他們將在3nm節點首發GAA MCFET(多橋通道FET)工藝。由於FinFET的限制,預計在5nm節點之後會被取代。

實際上,5nm在三星手中,也僅僅是7nm LPP的改良,可視為導入第二代EUV的一代。7nm LPP向後有三個迭代版本,分別是6nm LPP、5nm LPE和4nm LPE。

相較於年初的路線圖,三星6LPP只是簡單地引入SDB,從而提供了1.18倍的密度改進。另一個改變是刪除4LPP節點,在路線圖上只留下4LPE。最後,三星將3 GAAE和3 GAAP更名為3 GAE和3 GAP。

關於工藝核心指標,5nm LPE雖然沿用7nm LPP的晶體管和SRAM,但性能增強了11%,UHD下的密度會接近130 MTr/mm²,終於第一次超過了Intel 10nm和台積電7nm。

在4nm LPE上(2021年推出),三星可以做到137 MTr/mm²的密度,接近台積電5nm。

作者:萬南來源:快科技