Tag: CXL

三星宣布與Red Hat合作,引領CXL記憶體生態系統的擴展

三星宣布,與開源軟體供應商Red Hat合作,在實際用戶環境中成功驗證了Compute Express Link(CXL)內存的操作。三星稱這在業界裡尚屬首次,將引領其CXL內存生態系統的擴展。

由於生成式人工智慧(AI)、自動駕駛和內存資料庫(In-Memory Database,IMDB)等新興領域的數據吞吐量和內存需求呈指數級增長,對具有更大內存帶寬和容量的系統的需求也在增加。CXL作為一種開放性的互聯協議,擁有更高的帶寬,能夠讓CPU與GPU、FPGA或其他加速器之間實現高速高效的互聯,滿足現今高性能異構計算的要求,並且提供更高的帶寬及更好的內存一致性。作為下一代接口,與主DRAM一起使用的時候,可以擴大帶寬和容量,滿足計算市場高速數據處理的需求。

在最新的開發中,三星針對Red Hat Enterprise Linux(RHEL)9.3做了CXL內存的優化工作,並驗證了在Red Hat的KVM和Podman環境下的內存識別、讀寫操作。這讓數據中心客戶可以輕松使用三星CXL內存,無需對現有硬體進行額外調整。三星和Red Hat還在合作編寫「RHEL 9.3 CXL內存啟用指南」,以幫助用戶在該作業系統上使用三星的CXL內存,並在各種用戶環境中構建高性能計算系統。

三星和Red Hat的合作始於2022年5月,雙方簽署了關於下一代存儲器合作的諒解備忘錄(MOU),並將通過三星存儲器研究中心(SMRC)繼續開發CXL開源和參考模型。目前雙方合作的范圍涵蓋一系列存儲和內存產品,包括NVMe SSD、CXL內存、計算內存/存儲和結構。 ...

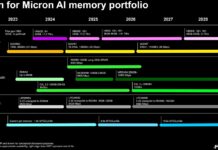

美光分享未來五年的路線圖:HBM4、CXL 2.0和LPCAMM2都在其中

近日,美光推出了基於單顆32Gb晶片的128GB DDR5-8000 RDIMM內存模塊。據TomsHardware報導,美光還公布了未來五年的產品路線圖,分享了對高性能、高容量存儲技術的展望,其中包括了一些過去未曾公開討論的技術。

美光希望未來幾年繼續在HBM和GDDR類內存上努力,此前已推出業界首款帶寬超過1.2 TB/s、引腳速度超過9.2 GB/s、8層垂直堆疊的24GB容量HBM3 Gen2,對應的應該就是路線圖上顯示的HBM3E。美光該款HBM3E將於2024年初到來,預計會在英偉達面向AI和HPC推出的新一代GPU上首次亮相。美光還在准備12層垂直堆疊的單品36GB HBM3E晶片,將會在2025年推出。

更大變化的將是HBM4,計劃在2026年發布,內存堆棧將採用2048位接口,帶寬超過1.5 TB/s。美光打算在2026年至2027年之間,推出容量在36GB至48GB、12/16層垂直堆疊的產品。到了2028年還會有HBM4E,頻率將進一步提升,容量將增加至48GB到64GB,帶寬增加至2 TB/s以上。

下一個GDDR版本,也就是GDDR7將會在2024年末到來,每個數據I/O接口的速率達到了32 Gbps,容量為16Gb至24Gb。預計到2026年末,單個晶片的容量會超過24Gb,速率也會提升至36 Gbps。

美光預計在2025年提供128GB至256GB的MCR DIMM內存模塊,數據傳輸速率為8800 MT/s,然後在2026年或2027年提供容量超過256GB的MCR DIMM內存模塊,數據傳輸速率會攀升至12800 MT/s。同時美光准備推出支持CXL 2.0的內存模塊,容量在128GB至256GB,帶寬將達到36 GB/s,接下來還有支持CXL 3.x的內存模塊,容量超過256GB,帶寬超過72 GB/s。

對於低功耗應用,業界將繼續使用LPDDR內存。美光速率為8533 MT/s或9600 MT/s的LPDDR5X將繼續使用一段時間,然後從2025年開始提供基於LPDDR設計的LPCAMM2內存,速率為8533 MT/s,容量在16GB至128GB,到了2026年中旬還會有速率為9600 MT/s、容量超過192GB的產品。 ...

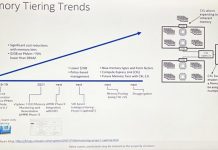

三星和SK海力士將加速CXL技術開發:繼HBM之後的「新藍海」

CXL作為一種開放性的互聯協議,能夠讓CPU與GPU、FPGA或其他加速器之間實現高速高效的互聯,滿足現今高性能異構計算的要求,並且提供更高的帶寬及更好的內存一致性。其建立在PCIe 5.0標準的物理和電氣接口上,目前最新規范已來到Compute EXpress Link(CXL)3.0。

據Business Korea報導,近日有市場調查機構的報告顯示,全球CXL市場規模在2028年將達到150億美元,雖然目前只有不到10%的CPU與CXL標准兼容,但預計到2027年所有CPU都被設計為支持CXL接口。預計2028年全球CXL市場的80%收入來自於DRAM,也就是說占了150億美元中的120億美元。

爭奪CXL市場的核心自然就是DRAM,三星和SK海力士是全球第一和第二大存儲器廠商,自然不會錯過CXL這片「新藍海」,目前都在積極開發CXL技術,以提高伺服器DRAM銷量。CXL內存模塊理論上在伺服器中可以實現「無限」的DRAM擴展,而且還能統一不同信息處理設備直接的通信協議,簡化了數據處理、減少了數據瓶頸、提高了能源效率,解決了現有計算機標准里DRAM的物理可擴展性問題。

近年來,人工智慧(AI)、高性能計算(HPC)和PC一直在推動高性能DRAM產品的研發,三星和SK海力士都認為,CXL是繼HBM之後引領存儲器市場的新技術,都打算加大投入,加速CXL技術開發,以搶占先機。 ...

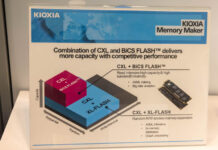

鎧俠展示CXL記憶體擴展模塊:分別基於BiCS 3D NAND和第二代XL-Flash

近日在美國聖克拉拉舉行的2023快閃記憶體峰會(Flash Memory Summit 2023)上,作為世界上最主要的NAND快閃記憶體製造商之一的鎧俠(Kioxia),介紹了其基於Compute Express Link(CXL)和第二代XL-Flash或BiCS 3D NAND的解決方案。

CXL技術允許構建各種設備來處理大量的工作負載,從擴展內存子系統的容量和性能到提供超快速的持久存儲。據ServeTheHome報導,鎧俠提供了兩種CXL產品:一種是基於CXL+XL-Flash快閃記憶體的產品,用於以性能和可靠性為中心的應用,比如資料庫和人工智慧推理等;另外一種是基於CXL+BiCS FLASH的產品,用於大數據和人工智慧訓練等。兩種存儲設備都採用了特助的控制器,對各自的任務做了針對性的優化。

鎧俠在去年推出了第二代XL-FLASH存儲級內存解決方案,這是一種基於其BiCS FLASH 3D快閃記憶體技術的存儲級內存(SCM)解決方案。與第一代採用SLC NAND不同,第二代改用了MLC NAND,提供了更高的讀寫性能及更低的延遲,保證了比主流3D TLC NAND有更高的性能,並有效降低了成本。鎧俠表示,當CXL與第二代XL-FLASH結合後,不但實現了更高的容量,同時更具成本效益。

這次鎧俠展示了1.3TB的CXL 1.1/CXL 2.0 BiCS 3D NAND設備樣品,外形為E1.S和E3.S規格,採用了PCIe 5.0 x4接口。鎧俠沒有透露具體的性能參數,可能是由於開發還沒完成。雖然使用基於CXL協議的PCIe接口加上低延遲的3D TLC NAND似乎是一個合理的方案,但性能不如採用第二代XL-FLASH的產品。

對於旗下CXL內存擴展模塊的發布計劃,鎧俠一直守口如瓶。從展示的情況來看,基於CXL+BiCS...

美光推出CZ120記憶體擴展模塊:支持CXL 2.0,容量128/256GB

美光宣布,推出CZ120內存擴展模塊,已經向合作夥伴和客戶提供了相關的樣品。其基於Compute Express Link(CXL)2.0Type 3標准打造,容量為128GB和256GB,採用了PCIe 5.0 x8接口,外形為E3.S 2T規格,內部搭載了Microchip的SMC 2000微控制器,使用的DRAM晶片採用了1α工藝節點進行生產。

CZ120內存擴展模塊提供了高達36GB/s的帶寬,相比於一般相同容量的DDR5-4800 RDIMM(帶寬為38.4GB/s)只是稍慢一些。目前AMD第四代EPYC伺服器處理器(代號Genoa)支持12通道DDR5-4800內存子系統,提供高達460.8GB/s的帶寬,而英特爾第四代Xeon伺服器處理器(代號Sapphire Rapids)支持8通道DDR5-4800內存子系統,提供高達307.2GB/s的帶寬。一般情況下,這些處理器都具有足夠的帶寬,但某些工作負載需要更大容量的內存和更高的帶寬,比如資料庫軟體,這時候CZ120內存擴展模塊就能發揮作用了。

據美光的介紹,如果在一台配備12條64GB DDR5內存的系統上增加四個256GB的CZ120內存擴展模塊,可以使伺服器處理器的內存讀寫帶寬提高24%,而且多出的內存容量可以讓其每天多處理96%的資料庫查詢。

美光表示,一直使用英特爾和AMD的平台開發和測試CZ120內存擴展模塊,希望通過其產品創新與CXL生態系統的合作,讓新標准更快地被接受,以滿足數據中心及其內存密集型工作負載不斷增長的需求。美光暫時還沒有透露CZ120內存擴展模塊的具體定價,以及出貨計劃,估計要等各方完成驗證和認證工作後才能進行,應該要等到2024年。 ...

三星開發出業界首款支持CXL 2.0的CXL記憶體模塊,計劃在今年晚些時候量產

三星宣布,以2022年5月業界首款基於Compute Express Link(CXL)1.1的CXL DRAM為基礎,推出了業界首款支持CXL 2.0的128GB CXLDRAM,預計將加速下一代存儲解決方案的商用化。

這次支持CXL 2.0的CXL記憶體模塊採用了PCIe 5.0 x8接口,提供了35GB/s的帶寬。三星計劃在今年晚些時候開始生產支持CXL 2.0的CXL記憶體模塊,並准備推出各種不同容量的衍生產品,以滿足未來計算應用的需求。

三星表示,其一直處於CXL技術的最前沿,致力於通過與全行業的數據中心、伺服器和晶片組公司合作,進一步擴展CXL生態系統。此次三星與英特爾合作,在至強伺服器平台上取得的里程碑式進步,雙方的共同投資將促進CXL產品在整個行業內的應用和發展。

CXL聯盟在2020年年末推出了CXL 2.0規范,其建立在PCIe 5.0標準的物理和電氣接口上,主要增加了記憶體池的支持,以最大限度地提高記憶體利用率,並且提供了對持久性記憶體的標準化管理,允許與DDR同時運行,從而可以釋放DDR用於其他用途。

CXL作為一種開放性的互聯協議,擁有更高的帶寬,能夠讓CPU與GPU、FPGA或其他加速器之間實現高速高效的互聯,滿足現今高性能異構計算的要求,並且提供更高的帶寬及更好的記憶體一致性。作為下一代接口,與主DRAM一起使用的時候,可以擴大帶寬和容量,預計將在人工智慧(AI)和機器學習(ML)等核心技術的高速數據處理需求迅速增加的下一代計算市場掀起波瀾。 ...

瀾起科技PCIe 5.0/CXL 2.0 Retimer晶片量產,提供穩定可靠的互連解決方案

瀾起科技宣布,其PCIe 5.0/CXL 2.0 Retimer晶片成功實現量產。這是對現有PCIe 4.0 Retimer產品的升級,為業界提供穩定可靠的高帶寬、低延遲PCIe 5.0/CXL 2.0互連解決方案。

據瀾起科技介紹,該款PCIe 5.0/CXL 2.0 Retimer晶片採用了先進的信號調理技術,以提升信號的完整性,增加高速信號的有效傳輸距離。該晶片符合PCI-SIG和CXL行業組織的相關技術規范,採用業界主流封裝,傳輸速率高達32 GT/s,在業界率先支持低於5 ns的超低傳輸時延。晶片支持SRIS和Retimer級聯等復雜系統拓撲,是應對下一代伺服器、企業存儲、AI加速系統中PCIe/CXL信號完整性挑戰的理想解決方案。

瀾起科技已經與主要合作夥伴展開緊密協作,完成了互操作測試,為新晶片在雲計算和數據中心的規模部署奠定了堅實基礎。其合作夥伴分布在多個領域,包括CPU、交換晶片、固態硬碟、GPU和網卡等。瀾起科技已針對AI伺服器等多種典型應用場景,提供基於PCIe 5.0/CXL 2.0 Retimer晶片的參考設計方案、評估板及配套軟體等完善的技術支持服務,可幫助客戶快速完成導入設計並縮短新產品上市周期。

目前瀾起科技還在推進PCIe 6.0 Retimer晶片的研發工作,以緊跟互連技術的前沿。 ...

SK海力士宣布DDR5和CXL解決方案已通過AMD驗證,可支持EPYC 9004系列

近日AMD在美國加利福尼亞州舉行了名為「Together We Advance Data Centers」的主題活動,正式發布了基於Zen 4架構、代號Genoa的第四代EPYC伺服器處理器。第四代EPYC伺服器處理器使用了全新的SP5插座,提供了創新的技術和功能,包括DDR5和CXL 1.1+等。

SK海力士宣布,已經與AMD展開了密切的合作,為EPYC 9004系列伺服器處理器提供了完全兼容的DDR5和CXL解決方案,並得到了AMD的驗證。此外,SK海力士還與AMD在第四代EPYC伺服器處理器參考架構上測試PCIe 5.0連接的穩定性,以便未來提供高性能的PCIe 5.0NVMe解決方案,以響應當今AI和ML應用市場的需求。

SK海力士提供的1y nm、1a nm 16 Gb DDR5 DRAM模塊,以及1a nm 24Gb DDR5 DRAM模塊,可在第四代EPYC伺服器處理器上實現4800 Mbps的支持,相比現有的DDR4產品多提供50%的記憶體帶寬。SK海力士還提供了CXL存儲器,這是一個容量為96GB的產品,基於1a nm 24Gb DDR5...

AMD計劃將CXL技術引入消費級CPU,或在未來三到五年內

近日AMD在一場網絡研討會上,出人意料地透露了其新計劃:在未來三到五年里,將Compute EXpress Link(CXL)技術引入消費級CPU。這意味著會將持久記憶體技術帶到記憶體總線上,以進一步提高性能。利用CXL記憶體模塊和系統記憶體共享大型記憶體池,可獲得更高的性能、更低的延遲和記憶體擴展功能。

與英特爾過往的傲騰(Optane)技術不同,CXL通過開放協議已獲得行業的廣泛支持。其建立在PCIe標準的物理和電氣接口上,不但能夠讓CPU與GPU、FPGA或其他加速器之間實現高速高效的互聯,滿足現今高性能異構計算的要求,而且可以支持多種類型的記憶體。CXL聯盟是在2019年成立的,英特爾和AMD都是其中的成員,而目前CXL規范已到了3.0版本。

據TomsHardware報導,在AMD的這場網絡研討會里,涵蓋了多個主題,包括AM5平台、DDR5記憶體、以及PCIe 5.0 SSD等。在提問環節中,AMD回答「為什麼存儲設備沒有連接到記憶體總線」的時候,其儲存和記憶體高級經理LeahSchoeb表示,接下來的三到五年中,首先會在伺服器領域看到持久記憶體技術的加入,然後會到消費領域,AMD將確保系統記憶體與其他存儲設備可以通過CXL協議在同一總線上進行通信。

群聯電子相關負責人也對這個話題做了補充,稱這是另一個生態系統類型的項目,需要大家共同努力才能做到這一點,這些合作在過去幾年里推動了PC的發展,雙方暫時在該領域宣布任何事情。不過第一款支持CXL的CPU很快就會到來,AMD代號Genoa的EPYC和英特爾的Sapphire Rapids處理器都圍繞PCIe 5.0接口構建的規范進行了早期修訂。 ...

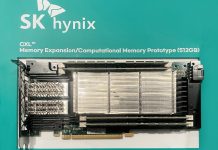

SK海力士推出CMS模塊,首款具有計算功能的CXL存儲器解決方案

SK海力士在兩個月前宣布,已開發出首款基於DDR5 DRAM的CXL存儲器樣品,計劃於2023年投入量產。現在SK海力士更進一步,宣布成功開發了業界首款搭載計算功能的CXL存儲器解決方案CMS(CMS),在一個512GB的CXL記憶體模塊中集成了計算功能。

近日在美國聖何塞舉行的OCP(Open Compute Project)全球峰會上,SK海力士首次公開了CMS及其軟硬體平台,向客戶展示了下一代高性能計算解決方案以及其價值。預計CMS模塊將安裝在下一代伺服器平台上,以提高系統性能和能源效率。

基於PCIe的CXL作為一種開放性互聯協議,擁有更高的帶寬,能夠讓CPU與GPU、FPGA或其他加速器之間實現高速高效的互聯,滿足現今高性能異構計算的要求,並且提供更高的帶寬及更好的記憶體一致性。SK海力士在CXL協議基礎上,融合了可擴展高容量記憶體和計算功能,推出了CMS模塊。

SK海力士的CMS模塊使用了四條128GB的傳統記憶體,搭配了一個片上系統,提供了大數據分析等應用常用的機器學習和數據過濾計算功能。其具備PCIe 4.0接口,支持CXL.mem和CXL.io協議,另外還有兩個網絡連接器,用於連接到其他節點。暫時還不確定CMS模塊的功耗,上面配有一個8Pin外接供電接口,可提供150W的功率。

SK海力士計劃在11月初韓國舉行的SK技術峰會上,進行相關的演示,未來還會積極開展CXL存儲器相關的研發和合作,為客戶提供不同的附加值。 ...

JEDEC與CXL聯盟簽署諒解備忘錄,以推進持久記憶體技術發展

JEDEC宣布,已經與CXL聯盟簽署諒解備忘錄(MOU),正式確定兩個組織之間的合作。

根據協議的內容,雙方將組建一個聯合工作組,加強互相間的信息交流,以幫助各自組織制定的標準可以相互增強。如果要加入到JEDEC和CXL聯盟的聯合工作組,必須是兩個組織的成員級別,這可以與各自的智慧財產權政策做綁定。

CXL聯盟主席Siamak Tavallaei表示:

「JEDEC和CXL 聯盟之間的諒解備忘錄將建立一個持續溝通的框架,以協調兩個組織之間的未來。聯合工作組將就外形尺寸、管理、安全以及DRAM和其他記憶體技術相關的解決方案展開合作。」

JEDEC董事會主席Mian Quddus表示:

「在數十家行業領先公司的支持下,此次合作將幫助兩個組織優化各自標準的開發,並將支持JEDEC創建針對CXL連接的記憶體模塊和組件的標準。」

近期CXL聯盟推出了Compute EXpress Link(CXL)3.0規范,在前代技術基礎上做了進一步擴展,以提高擴展性並通過先進的交互功能、高效的點對點通信、以及跨越多個計算領域的細粒度資源共享優化系統級數據流。幾乎同一時間,OpenCAPI聯盟宣布,將會把OpenCAPI和OMI規范以及OpenCAPI聯盟的資產轉讓給CXL聯盟。

去年末,Gen-Z聯盟宣布將其所有技術規格和資產轉讓給CXL聯盟。加上此次CXL聯盟與JEDEC加強合作,意味著CXL聯盟不但一統I/O互連標準,而且未來很可能會進一步擴大應用的范圍。 ...

三星公布下一代記憶體和存儲技術,確認業界首款UFS 4.0快閃記憶體已量產

三星在2022全球快閃記憶體峰會(Flash Memory Summit,FMS)上,推出了一系列下一代記憶體和存儲技術。在題為「Memory Innovations Navigating the Big Data Era」的主題演講中,三星重點介紹了推動大數據市場進步的四個技術領域,分別為數據移動、數據存儲、數據處理和數據管理,並展示了針對每一個領域的解決方案。

首先,三星宣布將推出下一代「PB級別」的存儲,新的解決方案將允許單個伺服器單元打包超過1 PB的存儲空間,使得相同占地面積內,以最少的伺服器數量大幅度增加存儲容量,高伺服器利用率也有助於降低功耗。

其次,三星推出了「Memory-Semantic SSD」,結合了存儲和DRAM優勢,利用Compute Express Link(CXL)互連技術和內置的DRAM緩存,Memory-Semantic SSD在AI和ML應用程式中可以將隨機讀取和延遲的表現提高20倍,通過針對性的優化,非常適合越來越多需要快速處理的較小數據集。

接著三星介紹了其遙測技術,可以從客戶SSD內的關鍵組件收集可讀的元數據,以提前檢測和預防任何潛在的問題。三星表示,隨著SSD在數據中心更廣泛地採用,通過高級技術手段進行更可靠、更高效的管理變得愈加重要。

最後,三星宣布今年5月份推出的業界首款UFS 4.0快閃記憶體解決方案計劃在本月進入量產階段。作為全球主要的手機零部件供應商,三星相信UFS 4.0快閃記憶體很快會出現在各個品牌的新一代旗艦手機上,之後還會用於汽車、AR和VR等應用場景。三星還透露兩款企業級SSD已進入量產階段,分別是PM1743和PM1653,前者是業界首款PCIe 5.0 SSD,後者是首款24G SAS SSD。

此外,三星還強調了其SmartSSD與CXL DRAM產品線,旨在避免當前記憶體和存儲架構中的瓶頸。 ...

CXL將一統I/O互連標準,OpenCAPI聯盟宣布向其轉移相關技術和資產

對於不少存儲廠商來說,近日舉行的2022全球快閃記憶體峰會是一個展示新技術、新產品、討論新I/O互連標準的好機會。近年來,半導體行業在計算方面發生了較為大的變化,特定應用程式的硬體加速變得更加普遍,新的記憶體/快閃記憶體技術影響著技術的發展。

OpenCAPI聯盟宣布,已經與CXL聯盟達成協議,若經各方批准,將會把OpenCAPI和OMI規范以及OpenCAPI聯盟的資產轉讓給CXL聯盟。去年末,Gen-Z聯盟宣布將其所有技術規格和資產轉讓給CXL聯盟,加上此次OpenCAPI聯盟相同的舉動,意味著CXL聯盟將一統I/O互連標準。

在2016年,為了滿足對開放架構的需求,IBM和Xilinx等公司成立了OpenCAPI聯盟(OCC),旨在為處理器、記憶體擴展和加速器提供行業支持的緩存一致性互連。其基於IBM現有的Coherent Accelerator Processor Interface(CAPI)技術,並將其向外開放。在過去數年間,OpenCAPI的應用有限,較為引人注目的是IBM的Power 9處理器系列。

CXL聯盟的啟動時間要比OpenCAPI聯盟更晚一些,2019年英特爾聯合阿里巴巴、戴爾EMC、Facebook、Google、HPE、華為和微軟共同成立,隨後AMD和Arm也先後加入。全新的互聯協議Compute EXpress Link(CXL)是一種開放性的互聯協議,能夠讓CPU與GPU、FPGA或其他加速器之間實現高速高效的互聯,滿足現今高性能異構計算的要求,並且提供更高的帶寬及更好的記憶體一致性,目前最新的是CXL 3.0規范。 ...

CXL聯盟發布Compute Express Link 3.0:速率翻倍、提高擴展性並優化管理

CXL聯盟宣布,推出Compute EXpress Link(CXL)3.0規范,在前代技術基礎上做了進一步擴展,以提高擴展性並通過先進的交互功能、高效的點對點通信、以及跨越多個計算領域的細粒度資源共享優化系統級數據流。

CXL作為一種開放性的互聯協議,能夠讓CPU與GPU、FPGA或其他加速器之間實現高速高效的互聯,滿足現今高性能異構計算的要求,並且提供更高的帶寬及更好的記憶體一致性。

在CXL 3.0規范中,引入了結構功能和管理、改進的記憶體池、增強的一致性以及對等通信;數據傳輸速率翻倍提升至64 GT/s,且與CXL 2.0相比並沒有增加延遲;同時向後兼容CXL 2.0、CXL 1.1和CXL 1.0版規范。

CXL聯盟則是在2019年啟動,英特爾聯合阿里巴巴、戴爾EMC、Facebook、Google、HPE、華為和微軟共同成立,隨後AMD和Arm也先後加入。去年末,Gen-Z聯盟確認將其所有技術規格和資產轉讓給CXL聯盟,將CXL協議作為唯一的行業標準繼續推進。

在成立之初,CXL聯盟就已經發布了CXL 1.0規范,隨後又發布了改進的CXL 1.1規范。2020年末宣布了新的CXL 2.0規范,建立在PCIe 5.0標準的物理和電氣接口上,主要增加了記憶體池的支持,以最大限度地提高記憶體利用率,並且提供了對持久性記憶體的標準化管理,允許與DDR同時運行,從而可以釋放DDR用於其他用途。 ...

SK海力士宣布已開發出DDR5 DRAM CXL存儲器,將進一步擴大CXL生態系統

SK海力士宣布,已開發出首款基於DDR5 DRAM的CXL存儲器樣品,將加快搶占下一代記憶體解決方案市場的步伐,計劃於2023年投入量產。此次SK海力士的CXL存儲器採用了EDSFFE3.S規格的外形,支持PCIe 5.0 x8通道,配備了CXL控制器,使用了DDR5標準DRAM。

基於PCIe的CXL作為一種開放性互聯協議,擁有更高的帶寬,能夠讓CPU與GPU、FPGA或其他加速器之間實現高速高效的互聯,滿足現今高性能異構計算的要求,並且提供更高的帶寬及更好的記憶體一致性。SK海力士從CXL聯盟成立之初就積極參與其中,主導了CXL存儲器的發展。

SK海力士表示,該DDR5 DRAM CXL存儲器是一款96GB產品,採用了最新技術節點1anm DDR5 24Gb DRAM,通過靈活的帶寬配置和經濟高效的容量來進行擴展,從而更具有經濟性的優勢,以滿足客戶的需求。

為了進一步擴大CXL存儲器生態系統,SK海力士開發出專用的HMSDK(Heterogeneous Memory Software Development Kit,異構存儲器軟體開發套件),計劃於今年第四季度,作為開放原始碼發布,並配備可適用於多種驅動環境中的系統性能提升功能和監控功能,這將有助於用戶更有效地使用SK海力士的CXL存儲器。

SK海力士目前已准備了驗證使用的樣品,並計劃在今年8月初在全球快閃記憶體峰會(Flash Memory Summit,FMS)、9月底在英特爾技術創新峰會(Intel Innovation)、以及10月的開源計算項目全球峰會(Open Compute Project,OCP)上依次展示實物產品。 ...

三星推出業界首款512GB CXL記憶體模塊,並計劃升級SMDK

三星宣布,已開發出業界首款512GB Compute Express Link(CXL)DRAM,朝著CXL的商業化邁出了重要一步,這不但實現極高的記憶體容量,而且能讓系統中延遲降低。自2021年5月份,三星推出業界首個FPGA的CXL DRAM原型以來,一直與數據中心、企業伺服器和晶片組公司密切合作,以開發經過改進的、可定製的CXL設備。

據三星介紹,這次的新型CXL記憶體模塊是第一款採用512GB DDR5記憶體的產品,搭載了專用的控制器,支持PCIe 5.0接口,採用了EDSFF尺寸。其容量是之前版本的四倍,而系統延遲只有五分之一,非常適合下一代需要大容量存儲的企業伺服器和數據中心。

三星還計劃推出用於CXL(Compute Express Link)記憶體模塊的可擴展記憶體開發套件(SMDK)的升級版本,以促使更多廠商將CXL記憶體模塊部署到現有及未來的IT系統中。這是一套開源軟體解決方案,旨在為CXL記憶體模塊的平台提供相關的開發支持工作。三星的SMDK和CXL記憶體模塊能夠在異構記憶體系統中無縫協同工作,軟體工具包由庫(一組預先構建的可重用代碼)和應用程式編程接口(API)組成,開發人員可以輕松地將CXL記憶體模塊集成到系統,而無需修改現有應用環境,或為此做特殊的優化來滿足系統需求。

CXL作為一種開放性的互聯協議,擁有更高的帶寬,能夠讓CPU與GPU、FPGA或其他加速器之間實現高速高效的互聯,滿足現今高性能異構計算的要求,並且提供更高的帶寬及更好的記憶體一致性。 ...

瀾起科技發布全球首款CXL記憶體擴展控制器晶片,並試產DDR5第二代RCD晶片

瀾起科技宣布,推出全球首款CXL(Compute Express Link)記憶體擴展控制器晶片(MXC)。其專為記憶體AIC擴展卡、背板及EDSFF記憶體模組而設計,可大幅擴展記憶體容量和帶寬,以滿足高性能計算、人工智慧等數據密集型應用的需求。

據瀾起科技介紹,這款CXL記憶體擴展控制器晶片屬於CXL協議所定義的第三種設備類型,支持JEDEC DDR4和DDR5標準,同時也符合CXL 2.0規范,支持PCIe 5.0。該款晶片可以為CPU及基於CXL協議的設備提供高帶寬、低延遲的高速互連解決方案,從而實現CPU與各CXL設備之間的記憶體共享。不但能夠大幅度提高系統性能,還可以降低軟體堆棧復雜性和數據中心總體擁有成本(TCO)。

此外,瀾起科技還宣布在業界內率先試產DDR5第二代寄存時鍾驅動器晶片(RCD),型號為M88DR5RCD02,支持5600 MT/s的數據傳輸速率。RCD是一種緩沖器,位於記憶體控制器和DRAM IC之間,可重新分配模塊內的命令/地址信號,以提高信號完整性並將更多記憶體設備連接到一個DRAM通道。

瀾起科技表示,M88DR5RCD02符合最新的JEDEC第二代DDR5寄存時鍾驅動器(RCD02)標準,相比其支持4800 MT/s數據傳輸速率的第一代RCD晶片M88DR5RCD01,最高支持速率提高了16.67%。其支持1.1V VDD和1.0V VDDIO電壓及多種節電模式,另外還包含了CA、CS和DFE訓練模式及雙頻支持等高級功能。 ...

英特爾即將推出第三代Optane產品,未來會把重點放在CXL

此前有報導指,英特爾位於新墨西哥州的研發中心正在開發第四代Optane產品。3D XPoint曾經被認為是一項創新性的高密度非易失性存儲器技術,不過在市場上一直沒有真正發揮其潛力,據稱英特爾的傲騰業務在過往幾年的虧損也相當嚴重。

據Blocks & Files報導,英特爾副總裁Kristie Mann表示第三代Optane產品即將到來,同時正在研究基於CXL規范的下一代產品。英特爾的團隊展示了新的Optane用例,不過並沒有提供確切的時間,未來數周內可能會有更多的消息。

雖然英特爾將推出搭載3D XPoint快閃記憶體晶片的第三代Optane產品,但英特爾已經將重點放在了未來基於CXL規范的產品上。Compute EXpress Link(CXL)是一種開放性的互聯協議,能夠讓CPU與GPU、FPGA或其他加速器之間實現高速高效的互聯,滿足現今高性能異構計算的要求,並且提供更高的帶寬及更好的記憶體一致性。

目前新的CXL 2.0規范建立在PCIe Gen5標準的物理和電氣接口上,增加了記憶體池的支持,以最大限度地提高記憶體利用率,並且提供了對持久性記憶體的標準化管理,允許與DDR同時運行,從而可以釋放DDR用於其他用途,同時向後兼容CXL 1.1和CXL 1.0版規范。三星去年推出了業界首款CXL記憶體模塊,採用了新的EDSFF外形尺寸,該產品極大擴展了伺服器系統的記憶體容量和帶寬。可以預見,未來英特爾應該會推出類似的產品。 ...

Gen-Z聯盟將向CXL聯盟轉讓其技術,以進一步推進互連架構的發展

Gen-Z聯盟成立於2016年,參與者包括了AMD、Arm、惠普企業(HPE)、IBM、鎂光、三星、海力士、希捷、西部數據等20個廠商,旨在開發一個針對數據中心和伺服器的全新開放系統互聯(總線),使得存儲元件的管理抽象化,附以現有的記憶體管理模式進行讀寫訪問操作,數據之間的交互更加高效、延遲更低。

CXL聯盟則是在2019年啟動,英特爾聯合阿里巴巴、戴爾EMC、Facebook、Google、HPE、華為和微軟共同成立,隨後AMD和Arm也先後加入。全新的互聯協議Compute EXpress Link(CXL)是一種開放性的互聯協議,能夠讓CPU與GPU、FPGA或其他加速器之間實現高速高效的互聯,滿足現今高性能異構計算的要求,並且提供更高的帶寬及更好的記憶體一致性。

在2020年4月份,CXL聯盟和Gen-Z聯盟簽署了一份諒解備忘錄,為兩者所定義的協議提供了機會。其採取的是聯合工作組的形式,鼓勵兩個組織之間的創新,以提高整個行業的水平,確保了兩種技術的相互操作性。據VideoCardz報導,CXL聯盟和Gen-Z聯盟雙方已確定兩個聯盟之間的協同作用,近日簽署了一份意向書,如果最終得到各方同意,會將Gen-Z的所有技術規格和資產轉讓給CXL聯盟。

這意味著,兩個聯盟過去多年在相關接口協議上的努力,最終會集中在CXL聯盟之下,並將CXL協議作為唯一的行業標準繼續推進。當然,這有利於簡化技術框架,將資源集中在一個組織,可以消除重復工作帶來的浪費,更好地推動下一代互連架構的技術發展。 ...

三星推出業界首個用於CXL記憶體模塊的可擴展記憶體開發套件,並會全面開源

三星宣布推出業界首個用於CXL(Compute Express Link)記憶體模塊的可擴展記憶體開發套件(SMDK),這是一套開源軟體解決方案,旨在為CXL記憶體模塊的平台提供相關的開發支持工作。三星表示,提供易於集成的軟體開發工具,可以讓數據中心系統開發人員更容易地使用CXL記憶體模塊,以用在人工智慧(AI)、機器學習(ML)以及邊緣計算等領域。

早在今年5月份,三星就發布了業界首款CXL記憶體模塊,這是基於Compute Express Link標準的新型存儲產品。該模塊集成了DDR5記憶體,採用了EDSFF尺寸,將記憶體容量擴展至TB級,減少由記憶體緩存引起的系統延遲,極大擴展了伺服器系統的記憶體容量和帶寬。

三星的SMDK和CXL記憶體模塊能夠在異構記憶體系統中無縫協同工作,軟體工具包由庫(一組預先構建的可重用代碼)和應用程式編程接口(API)組成。利用這款可擴展記憶體開發套件,開發人員可以輕松地將CXL記憶體模塊集成到系統,而無需修改現有應用環境,或為此做特殊的優化來滿足系統需求。SMDK支持記憶體虛擬化,允許系統設計人員有效管理共享記憶體架構中的擴展記憶體池。利用專有的智能分層引擎,SMDK可以識別和配置最適合每個用例的記憶體類型、容量和帶寬。

三星表示,SMDK將在明年上半年內開源,並會繼續增強,讓其得到更廣泛的使用。 ...

三星發布業界首款CXL記憶體模塊,已在英特爾下一代伺服器平台上成功通過驗證

三星發布了業界首款CXL記憶體模塊,這是基於Compute Express Link標準的新型存儲產品。

三星表示,該模塊集成了DDR5記憶體,採用了EDSFF尺寸,可以極大擴展伺服器系統的記憶體容量和帶寬。新模塊可以將記憶體容量擴展至TB級,減少由記憶體緩存引起的系統延遲,並允許伺服器系統加速器AI,機器學習和高性能計算工作負載。

同時,三星還採用了多種控制器和軟體技術,例如記憶體映射、接口轉換和錯誤管理,這將使CPU或GPU能夠識別CXL記憶體模塊並將其用作主記憶體。這款新型存儲產品已在英特爾下一代伺服器平台上成功通過驗證,目前正在與世界各地的數據中心和雲提供商合作,以更好地滿足需求。

在2019年,英特爾聯合眾廠商推出了針對數據中心,高性能計算,AI等領域的全新的Compute EXpress Link互聯協議,並宣布與阿里巴巴、戴爾EMC、Facebook、Google、HPE、華為和微軟聯合共同成立CXL聯盟,隨後AMD和Arm也先後加入。

在成立之初,就已經發布了CXL 1.0版規范,隨後又發布了改進的CXL 1.1版規范。在2020年末,又宣布新的CXL 2.0規范,建立在PCIe Gen5標準的物理和電氣接口上,主要增加了記憶體池的支持,以最大限度地提高記憶體利用率,並且提供了對持久性記憶體的標準化管理,允許與DDR同時運行,從而可以釋放DDR用於其他用途,同時向後兼容CXL 1.1和CXL 1.0版規范。

CXL作為一種開放性的互聯協議,擁有更高的帶寬,能夠讓CPU與GPU、FPGA或其他加速器之間實現高速高效的互聯,滿足現今高性能異構計算的要求,並且提供更高的帶寬及更好的記憶體一致性。 ...

海力士提議整合CPU及記憶體,另提出CXL記憶體解決方案

在國際可靠性物理研討會上,海力士CEO李錫熙提出了整合CPU以及記憶體的想法。目前記憶體標準正在准從DDR4過渡到DDR5上,後者相比前者可以帶來不少的性能增幅。不過,無論DDR記憶體有多快,與HBM相比在速度上還是要落後不少。這點也是李錫熙認為CPU以及記憶體應該要合並整合的基礎。

他在研討會上發表了對於一套「融合存儲以及邏輯」、更快的存儲標準的願景。

「高帶寬記憶體的速度提升是通過增加CPU及記憶體之間的通道而來的,而在CPU以及記憶體共同處於同一模塊的近記憶體處理(Processing Near Memory,簡稱PNM)中,速度提升會更多。如果更進一步的話,在記憶體內處理(Processing In Memory,簡稱PIM)中,當CPU以及記憶體都處於單一包裹(package)上的時候,速度可以獲得更大加的提升。而最終,CPU以及記憶體整合在同一晶片中的記憶體內計算(Computing in Memory,簡稱CIM)可以讓記憶體速度提升更加多。」

圖片來源:三星

海力士目前是全球第二大存儲生產商,不過他們並沒有開發及生產任何諸如CPU的晶片,因此CEO李錫熙呼籲半導體巨頭之間互相合作,形成一個可以維持CPU及記憶體集成的生態圈。

「只有在消費者、供貨商、學術界以及政府之間形成合作及共享的開放創新性的戰略合作關系,我們才可以塑造一個追求經濟及社會價值的新時代。」

另外,李錫熙也提出了一種名為Compute Express Link(CXL)的新標準,它可以與現有的PCIe總線互補。CXL記憶體可以快速且高效地在CPU以及圖形/計算加速器,或者智能網絡界面中移動數據。

「CXL記憶體不僅可以擴展帶寬以及容量,還可以實現持久性記憶體的價值,是一種可以縮小記憶體性能以及行業要求之間差距的解決方案。」

來源:超能網

ARM加入CXL高速互聯總線聯盟:拓展未來可以互聯的對象

前幾天,ARM正式加入CXL高速互聯總線聯盟,為了讓客戶使用到新的CPU與其他設備間的互聯協議,並且可以向CXL聯盟做出自己的貢獻。考慮到ARM晶片的應用范圍,此舉影響將非常深遠。

CXL聯盟是由Intel成立的,其主推的CXL(Compute EXpress Link)互聯協議是基於PCIe 5.0之上的一個新的規范,可以讓CPU與其他諸如GPU、FPGA以及另外的加速設備更好地連接在一起,帶來更高的帶寬以及更好的記憶體一致性。同時可以簡化相關硬體的設計難度,降低整套系統的成本。

CXL聯盟的參與者有Intel、AMD、Google、Facebook以及華為、微軟等科技界主要領頭公司,而ARM是少數幾家沒有加入CXL的科技領頭公司,不過它事實上早就已經參與進CXL的工作中了,並提供了自己的技術和推廣資源去支持這項新技術。在正式加入聯盟之後,ARM可以為其客戶提供一個完整的、針對CXL的軟體框架,盡管他們並沒有任何關於給即將推出的AMBA PCIe Gen 5物理層添加適當邏輯的計劃。

ARM同時也是PCI-SIG和Gen-Z的聯盟的董事會成員。此外,他們還有自家用於封裝內部晶片間互聯的CCIX總線。有了對於CXL的支持,ARM將允許其客戶構建擁有低延遲的緩存一致性和記憶體同步的CPU或者加速器。

ARM表示,支持緩存完全一致性的CCIX總線將被用作異構片上系統的內部晶片間互聯總線。同時,因為封裝內晶片間的通信並不是CXL協議的工作范疇,所以這兩者並不會形成競爭關系。也就是說,ARM可以在一片SoC內部使用CCIX總線,而這片SoC對外連接其他設備時可以使用CXL協議。 ...

Intel推出CXL總線協議:為數據中心,高性能計算打造

Intel在昨天聯合眾廠商一起推出了針對數據中心,高性能計算,AI等領域的全新的互聯協議Compute EXpress

Link(CXL),並正式發佈了CXL

1.0規范。這個協議擁有更高的帶寬,能夠讓CPU與GPU,FPGA或其他加速器之間實現高效,高速的互聯,能夠帶來更低的帶寬和更好的記憶體一致性。而該技術是建立在完善的PCIe

5.0的物理和電氣實現上的,不用通過專門設計的接口,簡化了服務器硬件的設計難度,降低了整體系統的成本。

Intel宣佈與阿里巴巴、戴爾EMC、臉譜、Google、HPE、華為、微軟聯合共同成立一個聯盟,來開發這個協議,用於消除CPU與加速器等計算密集型工作負載的瓶頸。而此次Intel扮演的角色與其在USB和PCIe開發中的角色一樣,

與聯盟成員共享技術成果,並共同持續開發。

與早前向USB推廣組織貢獻雷電3接口協議不同的是,這次Intel選擇自己成立聯盟並與聯盟成員共同開發。同時值得注意的是,這次宣佈CXL的時間點恰巧在NVIDIA宣佈正式收購以色列Mallanox公司之後。而Mallanox公司的業務就是為數據中心提供如infiniband這樣的高速傳輸協議。

此次Intel並沒有公佈更詳細的技術細節。而Intel聲稱將在今年上半年為聯盟成員提供第一代規范。此次CXL聯盟成員為服務器硬件製造商商,主流的雲計算提供商,網絡設備製造商,都為行業內的頂尖企業。而這次Intel為聯盟成員開放CXL協議鞏固自己在數據中心領域的地位。

來源:超能網