Tag: JEDEC

單條輕松128GB 還超薄 CAMM2正式成為筆記本記憶體標准

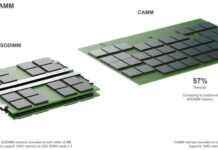

快科技12月11日消息,JEDEC組織官方宣布,Intel、戴爾等聯合提出的CAMM筆記本內存形態,已經被正式吸納為行業標准,命名為“CAMM2”,從而和DDR5、HBM3、GDDR6等技術並列。

CAMM全稱為“”,相比傳統的SO-DIMM內存,厚度變薄了57%,單條容量最高可達128GB,而頻率已經做到6400MHz。

它還有一個好處,那就是單條就能組成雙通道。

只不過,它的面積增大了不少,也貴得多。

CAMM2內存目前支持DDR5、LPDDR5/5X兩種版本,後者甚至可以做成獨立內存而不一定非要集成在主板上,但現階段還是以DDR5為主。

成為行業標准有助於推動CAMM2的普及,但暫時只有戴爾一家在做,其他PC、內存廠商均未表態。

來源:快科技

由戴爾發起,新的筆記本記憶體標準即將到來

SODIMM這個記憶體標準已經在筆記本上用了很多年了,只要你的筆記本是可以更換記憶體的話,就一定能看到它。而它將會在未來被一個新的標準所取代。

援引Liliputing和PCWorld的消息,JEDEC理事會成員,同時也是戴爾高級傑出工程師的Tom Schell稱,JEDEC正准備用CAMM替換掉已經用了25年的SODIMM標準。他們已經投票決定讓CAMM 0.5作為SODIMM的潛在替代品。JEDEC的目標是在今年的晚些時候推出更新的CAMM 1.0標準,並在明年推出CAMM記憶體的筆記本。

CAMM是由戴爾在2022年4月研發的,全稱為Compression Attached Memory Module(壓縮附加記憶體模塊)。跟SODIMM相比,雖然CAMM占據的面積更大,但是它比SODIMM薄了57%。其次,CAMM能提供更高的記憶體頻率和容量。SODIMM難以支持超過6400MT/s的記憶體速度,而這對於CAMM來說並非難事。CAMM還支持單條128GB記憶體。

另外,CAMM除了能為未來的遊戲本和工作站這些筆記本帶來更高的性能外,它還能搭載LPDDR記憶體,更薄的體型意味著它能被安裝在輕薄本中。考慮到目前絕大多數的輕薄本都是直接把記憶體焊在主板上,CAMM的推出可能讓輕薄本的可升級性得到提高。

當然,目前CAMM的標準還在討論制定中,再考慮到各家廠商的跟進情況,也許CAMM的普及還是需要一段相當長時間的。不過作為CAMM的研發者和推進者,也許戴爾會是採用CAMM記憶體最積極的那一個。 ...

JEDEC與CXL聯盟簽署諒解備忘錄,以推進持久記憶體技術發展

JEDEC宣布,已經與CXL聯盟簽署諒解備忘錄(MOU),正式確定兩個組織之間的合作。

根據協議的內容,雙方將組建一個聯合工作組,加強互相間的信息交流,以幫助各自組織制定的標準可以相互增強。如果要加入到JEDEC和CXL聯盟的聯合工作組,必須是兩個組織的成員級別,這可以與各自的智慧財產權政策做綁定。

CXL聯盟主席Siamak Tavallaei表示:

「JEDEC和CXL 聯盟之間的諒解備忘錄將建立一個持續溝通的框架,以協調兩個組織之間的未來。聯合工作組將就外形尺寸、管理、安全以及DRAM和其他記憶體技術相關的解決方案展開合作。」

JEDEC董事會主席Mian Quddus表示:

「在數十家行業領先公司的支持下,此次合作將幫助兩個組織優化各自標準的開發,並將支持JEDEC創建針對CXL連接的記憶體模塊和組件的標準。」

近期CXL聯盟推出了Compute EXpress Link(CXL)3.0規范,在前代技術基礎上做了進一步擴展,以提高擴展性並通過先進的交互功能、高效的點對點通信、以及跨越多個計算領域的細粒度資源共享優化系統級數據流。幾乎同一時間,OpenCAPI聯盟宣布,將會把OpenCAPI和OMI規范以及OpenCAPI聯盟的資產轉讓給CXL聯盟。

去年末,Gen-Z聯盟宣布將其所有技術規格和資產轉讓給CXL聯盟。加上此次CXL聯盟與JEDEC加強合作,意味著CXL聯盟不但一統I/O互連標準,而且未來很可能會進一步擴大應用的范圍。 ...

JEDEC發布HBM3記憶體標準:帶寬819GB/s、每個堆棧最高64GB容量

今天JEDEC發布了HBM3高帶寬記憶體標準,相比現有的HBM2和HBM2e標準有大幅的提升。這個新的HBM記憶體標準版本為JESD238 HBM3,目前相關技術文檔已經可以從JEDEC下載。

JEDEC表示,HBM3是一種創新的方法,是更高帶寬、更低功耗和單位面積容量的解決方案,對於高數據處理速率要求的應用場景來說至關重要,比如圖形處理和高性能計算的伺服器。新一代HBM3記憶體主要屬性包括:

將經過驗證的HBM2架構擴展到更高的帶寬,將HBM2的每引腳數據速率提高一倍,並定義高達6.4 Gb/s的數據傳輸速率,相當於819GB/s。

將獨立通道的數量從HBM2的8個增加到16個,每個通道有兩個偽通道,HBM3實際上支持32個通道。

支持4層、8層和12層TSV堆棧,並為未來擴展至16層TSV堆棧做好准備。

支持單層8Gb到32Gb的存儲密度,意味著容量從4GB(4層8Gb)到64GB(16層32Gb),預計第一代HBM3設備將基於單層16Gb。

為了滿足市場對高級平台RAS(可靠性、可用性、可維護性)的需求,HBM3引入了片上糾錯技術(ECC),以及實時錯誤報告和透明度。

通過在主機接口上使用低擺幅(0.4V)信號和較低 (1.1V)工作電壓來提高能效。

技術營銷總監兼JEDEC HBM小組委員會主席Barry Wagner表示,憑借HBM3記憶體更強的性能和可靠性,將對需要海量記憶體帶寬和容量的新應用提供有力的支持。此外,美光、SK海力士和Synopsys等企業的負責人也對HBM3記憶體標準的發布感到高興。

在去年10月份,SK海力士已宣布成功開發出了HBM3記憶體,成為全球首家開發出新一代HBM記憶體的公司。SK海力士提供了兩種容量,一個是12層矽通孔技術垂直堆疊的24GB,另一個則是8層堆疊的16GB,均提供819 GB/s的帶寬,前者的晶片高度也僅為30微米。 ...

JEDEC發布LPDDR5X記憶體標準,速率提高至8533Mbps

JEDEC固態存儲協會在2019年初正式發布了JESD209-5標準Low Power Double Data Rate 5即LPDDR5的標準,速率為6400MT/s,相比第一版LPDDR4的3200MT/s速率,直接翻了一倍,即便與LPDDR4X的4266MT/s速率相比也快了50%,這將明顯提升包括智慧型手機、平板電腦和超輕薄型電腦等應用場景的記憶體效率。

LPDDR5為了提升性能重新設計了架構,轉向16Banks可編程和多時鍾架構,並引入了Data-Copy和Write-X兩個新的指令,另外考慮到汽車與相關市場的需求,LPDDR5還引入了鏈路ECC糾錯功能。LPDDR5的電壓和LPDDR4X一樣是1.1V,信號電壓250mV,不過閒置狀態下電流將降低40%,可大幅降低功耗。

今天JEDEC固態存儲協會正式公布了JESD209-5B標準即LPDDR5X的標準,由JEDEC的JC-42.6低功耗存儲器小組委員會開發,這是對LPDDR5的可選擴展,專注於提高性能、功耗和靈活性,旨在提高包括5G通信性能、汽車高解析度增強現實/虛擬現實和使用AI的邊緣計算等應用場景的記憶體性能。

此最新版的主要更新包括了:1、速率提高到了8533MT/s。2、通過TX/RX均衡改善信號完整性。3、通過新的自適應刷新管理提高可靠性。4、LPDDR5X作為可選擴展,旨在提供更高的帶寬和簡化的架構。

美光、三星和Synopsys都參與了LPDDR5X的標準制定工作,各方都希望新標準可以為下一代智慧型手機、筆記本電腦和其他移動計算設備鋪平道路,打開5G和AI應用的大門,為遊戲、攝影和流媒體等記憶體密集型應用提供更好的用戶體驗。 ...