Tag: PLC

Solidigm展示全球首款PLC SSD,將率先用於數據中心

其實Intel早在2019年就宣布過他們在研究PLC快閃記憶體,而且還是用浮柵型結構,而接手Intel快閃記憶體業務的Solidigm也會繼承了他們的所有技術。近日,在全球快閃記憶體峰會的主題演講結束之際,Solidigm公司客戶端存儲事業部高級副總裁兼總經理Sanjay

Talreja在現場展示了全球首款正在研發的PLC SSD。

與QLC快閃記憶體相比,PLC快閃記憶體每個存儲單元存儲數據從4位增加到了5位,而它的電壓狀態會從2的4次方增加到2的5次方也就是32種,沿用浮柵型結構相對電荷捕獲型在讀取抗干擾、數據保持期上有著更好的表現,有著更長的讀取窗口,而且隨著存儲密度的增加,浮柵型對增加密度更加容易。此外,由於PLC能夠在製造QLC的設備上進行生產,因此,能夠將技術路線快速演進至PLC上。

採用PLC快閃記憶體的SSD和QLC的相比在相同的空間內,存儲的數據量能夠增加25%,可以用來解決固態存儲未來的成本、空間和能耗等問題,這一NAND密度的提升也將幫助Solidigm在多個重點領域增強其領導地位,例如:

AI、機器學習和大數據分析等現代工作負載所帶來的數據密集型需求。5G基礎設施建設所需的更快速、更密集的存儲。替換機械硬碟,目前仍有超過85%的數據中心的數據保存在HDD中。

Sanjay Talreja表示:"我們很高興能在今天向大家展示業界首塊正在研發的PLC

SSD,這既是Solidigm作為一家新公司的一個重要里程碑,也是一個對未來存儲技術的發展具有廣泛影響力的重要時刻。與客戶一同成長,並為客戶提供更加高效、更具性價比的SSD,對於AI、機器學習和大數據等主要增長領域都具有極其重要的意義。"

目前,Solidigm已經看到諸多超大規模雲服務供應商、數據中心OEM,以及存儲創新者對PLC技術持有濃厚的早期市場興趣,PLC

SSD將率先用於數據中心的解決方案中,具體時間待定。 ...

西數認為PLC快閃記憶體的SSD在2025年後才會出現,主控是最大問題

西數、東芝還有Intel都早在2019年就披露了PLC快閃記憶體技術的開發狀況,目前Intel和鎧俠都對PLC快閃記憶體首次亮相越來越有信心,新的快閃記憶體可以進一步降低SSD的價格,但西數近日則表示使用PLC快閃記憶體的SSD不太可能在2025年之前出現。

根據tomshardware的報導,西數任務使用PLC快閃記憶體只有在SSD主控變得更為先進的這個十年的後半段的某個適合才變得可行,也就是2025年之後,當然這只是他們的看法,其他快閃記憶體供應商則任務未來幾年3D

PLC SSD就可以進入市場和HDD競爭。

每種新快閃記憶體投入市場都會降低SSD的價格,但相對的耐用性和性能都會大幅下降,QLC快閃記憶體已經出現在市場上多年了,但它並沒有迅速的取代TLC快閃記憶體,過渡時間要比TLC取代MLC長得多,就是因為這兩個原因,耐久度問題可以通過用更大的容量來解決,但性能的問題就得慢慢等待更先進的主控與改良過的快閃記憶體才行。

PLC快閃記憶體與QLC快閃記憶體相比每單元可存儲數據從4位增加到5位,相對的電平數量從16個增加到32個,可以從中獲得25%的容量加成,但為了獲得這加成需要付出的更多,需要性能更強的ECC,需要更強大的磨損平衡算法,這就需要性能更強的SSD主控。

目前3D TLC SSD使用的主控已經提供了很高的性能與耐用性,他們使用了120bit/1KB甚至340bit/2KB LDPC

ECC算法,這些算法其實已經很復雜了,此外它還需要提供靜態、動態磨損均衡算法,EAID ECC等以進一步提高SSD的耐用性。

而3D QLC SSD的主控,需要支持2KB甚至4KB的LDPC ECC、以及更為復雜的磨損均衡算法,此外還需要更為優秀的SLC

Cache算法來提高SSD的性能。

至於3D PLC

SSD的話,需要的只會更多,目前SSD主控使用的Cortex-R8內核可能會不堪重負,需要升級至最新的Cortex-R82內核,性能可以提升21%~23%,但第一款採用Cortex-R82內核的SSD主控可能要2023年甚至2024年才會出現,而且是面向高端產品的控制器,然而3D

PLC剛進入市場時肯定是走廉價路線的,所以3D PLC快閃記憶體不可能這麼快進入市場。 ...

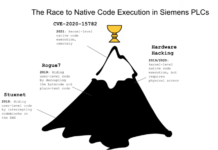

西門子PLC系統再曝嚴重漏洞 攻擊者可繞過保護並執行遠程代碼

上周五,西門子發布了一個更新,以修復近日曝出的又一個可編程邏輯控制器(PLC)的嚴重漏洞。受影響的 PLC 型號包括了 SIMATIC S7-1200 和 S7-1500,兩者都可能被惡意行為者用來遠程訪問受保護的記憶體區域,以實現不受限制和難以被發現的代碼執行。

(來自:Claroty)

通過對用於在微處理器中執行 PLC 指令的 MC7 / MC7+ 字節碼語言進行逆向工程,Claroty 證實了西門子 PLC 中存在的這個記憶體保護繞過漏洞(CVE-2020-15782)。

該漏洞的 CVSS 嚴重性評分為 8.1,慶幸的是目前尚無證據表明其已在野外被利用。西門子在警報(PDF)中提到,未經身份驗證的遠程攻擊者可通過網絡訪問 102 號 TCP 埠。

在將任意數據或代碼寫入受保護的記憶體區域、或讀取敏感區域的數據之後,黑客就能夠對設備發起進一步的攻擊。

Claroty...

Intel正在研究3D PLC快閃記憶體,堅持浮柵型結構不動搖

雖然現在QLC快閃記憶體還沒大規模普及,市場上採用QLC快閃記憶體的SSD數量稀少,然而快閃記憶體廠就已經在籌備下一代的PLC快閃記憶體,上個月東芝已經在國際快閃記憶體峰會展示過自己的PLC計劃,現在輪到Intel了。

Intel在今天上午在韓國首爾舉行的一場存儲會議上宣布的,他們表示未來的PLC快閃記憶體依然會採用浮柵型結構,其他廠家在3D快閃記憶體時代都轉向使用的電荷捕獲型,因為他們認為後者可以有效提升快閃記憶體耐久度,不過Intel認為浮柵型結構在讀取抗干擾、數據保持期上有著更好的表現,有著更長的讀取窗口,而且隨著存儲密度的增加,浮柵型對增加密度更加容易。

PLC快閃記憶體每個存儲單元會存儲5位數據,而它的電壓狀態會從2的4次方增加到2的5次方也就是32種,如果真如Intel所說那樣浮柵型結構在抗干擾上有優勢的話,它確實更適合用來製作PLC。Intel並沒有告訴大家什麼時候能看到PLC快閃記憶體,其他廠商其實也一樣,估計至少兩年內大家都可能看不到成品。 ...

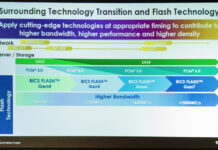

東芝存儲展示快閃記憶體生產未來路線圖:PLC快閃記憶體在規劃中

東芝存儲最近在國際存儲峰會上舉行了一次發布會,展示了未來他們的快閃記憶體生產路線圖。其中重點講解了自家的多層堆疊快閃記憶體顆粒規劃以及QLC之後的PLC顆粒的情況。

圖片來自於Tom's Hardware,下同

BiCS快閃記憶體是東芝存儲對於自家的3D多層堆疊式快閃記憶體顆粒的正式稱呼,目前已經發展到了第4代,也就是96層堆疊的3D快閃記憶體。在接下去的每一代BiCS中,東芝都會對應一種新的PCIe標準,比如BiCS 5會對應PCIe 4.0,BiCS 6會對應PCIe 5.0等,但沒有提供具體的時間表,並且在快閃記憶體帶寬上面,每一代BiCS都會有所進步,從目前的800MT/s一直到未來第6代的1600MT/s,計劃中的第7代將超過2000MT/s。

同時東芝已經在准備QLC的下一代,也就是每單元存儲5bit數據的顆粒生產了,我們知道,25是32,也就是每單元會出現32種電壓狀態,相比起TLC的8種、QLC的16種來說,PLC(Penta-level cell)的技術難度更高了。不過東芝稱他們的PLC已經通過了驗證,達到了可以使用的級別了。

而且現在QLC還沒得到大規模應用的有幾個原因,其中最為致命的就是它的速度還是太慢了,目前民用級市場上的大部分QLC產品都配置了SLC Cache,在緩存寫完之後這些產品的持續寫入速度甚至還不如一塊機械硬碟,這在很多人看來都是不可接受的事情,而PLC初期只會比QLC更慢。

東芝還宣布了一項新的工藝技術,它可以將原本的一個單元切割成兩半,同時保留原有的3D快閃記憶體工藝。在這種新工藝技術之下,東芝可以做到更大的die密度,並且在所有形式、全代數的BiCS快閃記憶體上都可以使用。 ...