PCIe 4.0還在普及階段,PCIe 5.0尚未到來,PCIe 6.0標準規范還沒完成,廠商們就已經迫不及待出方案了。

Synopsys(新思科技)宣布,推出全球首個完整的PCIe 6.0 IP方案,包括控制器、PHY物理層、驗證IP,可供PCIe 6.0 SoC設計早期開發之用。

它基於Synopsys廣受好評的DesignWare IP PCIe 5.0方案,完整支持PCIe 6.0標準特性,包括64GT/ PAM-4信號調制、FLIT模式、L0p低功耗模式等等,可滿足HPC高性能計算、AI、存儲SoC等應用領域對於延遲、帶寬、能效的各種需求。

為了實現吞吐量的最大化、延遲的最小化,Synopsys PCIe 6.0控制器採用了「MultiStream」(多流)架構,性能可達單流架構的最高2倍,並且還有1024-bit寬度架構,可以在關閉1GHz時序的同時,達到64GT/ x16的高帶寬,還優化了多數據源、多虛擬通道環境。

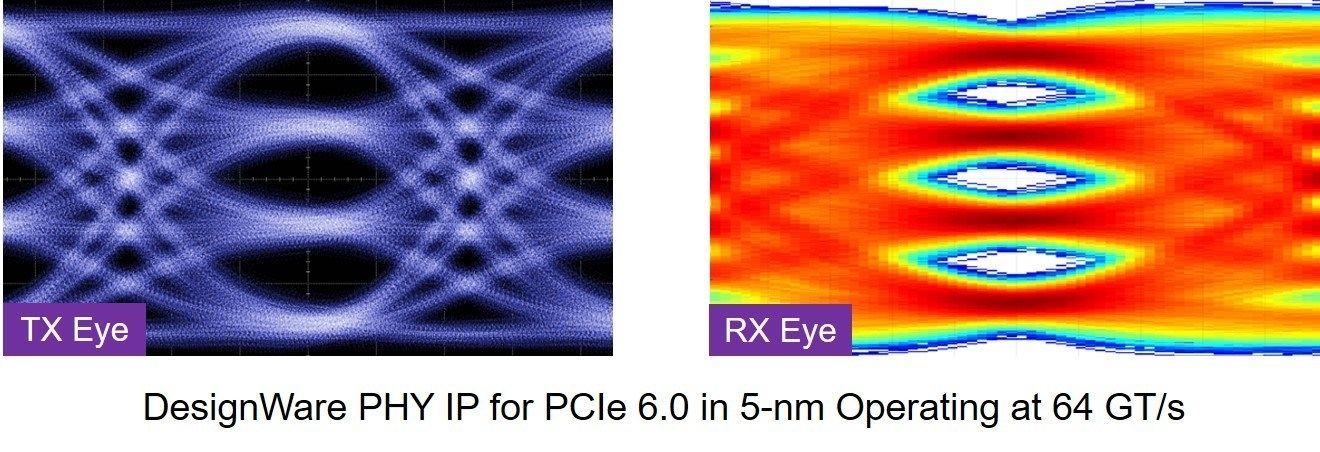

此外,新方案使用了獨特的自適應DSP算法,支持早期SoC開發,優化模擬和數字均衡,無論何種通道下都能獲得最佳能效,並且基於專利診斷功能,可確保幾乎零宕機時間。

值得一提的是,PHY物理層還使用了先進的5nm工藝,搭配獨特的模擬和DSP技術,可將功耗降低20%。

Synopsys PCIe 6.0 IP方案中的驗證IP現已可用,控制器、PHY物理層計劃在今年第三季度提供早期試用。

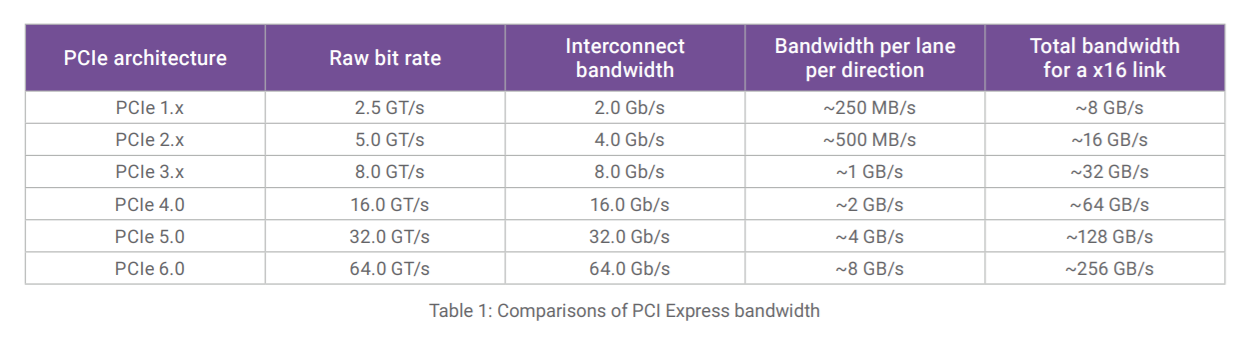

PCIe 6.0標準規范目前還在制定中,,按照傳統繼續讓I/O帶寬翻番達到64GT/,應用到實際中,PCIe 6.0 x1單向實際帶寬8GB/,PCIe 6.0 x16單向帶寬128GB/、雙向帶寬256GB/。

PCIe 6.0將延續PCIe 3.0時代引入的128b/130b編碼方式,但加入全新的脈沖幅度調制PAM4,取代PCIe 5.0 NRZ,可以在單個通道、同樣時間內封包更多數據,以及低延遲前向糾錯(FEC)和相關機制,以改進帶寬效率。

來源:快科技