Tag: 台積電4N

前台積電研發專家:中國半導體產業將自成體系 但難與全球生態競爭

3月22日,前台積電研發處處長楊光磊表示,中國面對美國對於半導體產業的出口管制必須自主發展,但是需多少時間才能完全自主還不清楚,可能需要幾十年才能自成體系。

近年來,在官方支持及內部需求的推動之下,中國半導體產業發展迅速。

即便是在美國聯合日本、荷蘭持續通過限制半導體設備出口來阻礙中國半導體產業發展進程,中國半導體產業的發展也仍未止步。

雖然目前台灣半導體製造業在前後段都占據了關鍵位置,美國、日本、歐洲在前段製造設備,以及後段封裝測試和材料領域有優勢,不過仍需要緊密合作才能滿足半導體市場的需求。

但是,中國大陸憑借官方支持以及自身龐大的市場內需的驅動之下,經過多年的發展,已經建立起了幾乎覆蓋整個半導體產業的供應鏈體系,雖然在不少環節依然比較薄弱,特別是在半導體設備方面。

楊光磊此前就曾表示,現在中國大陸半導體一大進步也表現在半導體設備上,過去沒有人願意做,現在已經有了一定規模,一定技術能力。並且預測未來幾年,中國大陸的成熟製程很有可能將依靠成本優勢橫掃世界。

在最新的演講當中,楊光磊進一步指出,中國大陸半導體產業在美國的限制之下必須自主發展,未來將會自成體系,但是可能需要幾十年才能完成。

即使能夠自成體系,但封閉系統下的發展,將會與外部世界合作的規模大不相同,且難以與外部的全球合作的生態系統競爭。不過,如果外部全球各國不能合作,就另當別論。

從整個半導體產業的發展看,楊光磊認為,台灣的成功也只是歸功於對的時間、對的地點和用對人,加上獨創的晶圓代工產業符合當地的文化。

未來,台積電憑借人工智慧發展機遇,加上全世界科技創新應用沒有改變晶圓廠基本需求,仍將占據領導地位。但是,將來的挑戰將是地緣政治壓力與風險使全球供應鏈重組,以及人才短缺與新世代文化差距等。

反觀日本半導體產業從1980年代全盛時期走下坡之後,呈落後狀況,但半導體材料地位依舊領先,還有半導體設備表現也強勁。現在,在政府全力支持下,日本半導體製造有望重回領先。但日本半導體製造布局,質量與成本競爭,也有人才短缺與數字轉型問題,都是接下來的挑戰。

在楊光磊看來,台灣與日本各有優勢,也須面對風險,雙方互補有機會更進一步。台灣半導體製造領先,日本在設備與材料領域舉足輕重,雙方合作則有加乘效應。

過去,聯電與富士通在20~90nm有合作,力積電現在則與日本SBI控股簽署了備忘錄合作28~55nm,台積電與SONY半導體、EDNSO合資的日本熊本晶圓廠JASM在12~28nm合作,都是很好的案例。

不過,雖然雙方合作有優勢,但也會存在競爭,比如積極發力尖端製程的Rapidus將會與台積電存在潛在競爭,加上兩地的文化差異,都是雙方半導體產業攜手須注意的問題。

對於各地半導體產業發展來說,人才可謂是非常的關鍵,除了需要想辦法吸引外部人才之外,自身人才的培養更是發展的核心動力。但是人才培育並非一蹴而就。

楊光磊此前就曾表示,人才的培養,政府只能扮演輔助角色,比起人的數量,應該更注重人才質量,對半導體人才教育也要有不同思維。

資料顯示,楊光磊此前曾在台積電服務20年時間,曾經參與台積電0.18、0.13 微米以及後來65納米等製程研發工作,2018年自台積電研發基礎工程處長的職位離職之後,於2019年7月出任中國中芯國際擔任獨立董事。直到2021年11月11日,楊光磊才辭任中芯國際獨立非執行董事及薪酬委員會成員職務。

來源:快科技

台積電創始人:美國復制台積電沒可能 半導體不是花錢就能獨立

快科技11月20日消息,台積電創辦人張忠謀公開表示,美國半導體行業想要獨立基本不可能。

張忠謀表示,美國要重新建立像台積電Capacity(規模)簡直是不可能的事情,至少在短期內不可能。

談及美國晶片法案,張忠謀說,吸引台積電赴美設廠投資金額為520億美元,當中390億美元為美國政府補貼,但這是多年補貼的合計總額。

而台積電每年平均投資300億美元,甚至更多,“這是否能解讀為美國吸引投資金額相對小”。

張忠謀稱,無論是美國晶片法案或其他法案,“我覺得都是蠻浪費的”。

“如果美國認為可以靠花錢進入世界上最復雜的晶片製造市場,那就太天真了。他稱,半導體晶片製造極其復雜,需要大量的勞動力,並講究組裝質量。”張忠謀說道。

來源:快科技

獲美國對華設備供應無限期豁免 台積電:只是28nm

10月14日消息,據悉,台積電已獲得美國的豁免延期,可以向該公司在中國大陸的工廠供應美國晶片設備。

隨後,台積電證實已獲准於南京持續運營,同時也正在申請在中國大陸運營的無限期豁免。台積電預計將獲得美國許可,無限期向其中國大陸工廠供應美國晶片設備。

“我們預計會通過VEU流程獲得永久授權。”台積電表示。該公司指出,他們之前並不需要申請VEU地位。台積電還在另外一份聲明中稱,公司已經獲得美國的批准,可在申請VEU地位的同時繼續運營南京工廠。

按照台積電的說法,目前正在擴充南京廠設備,以製造28納米晶片,目前被批準的也是這個及其以上製程的工藝,14nm、7nm等沒有在批準的名單中(其實想想都知道的嘛)。

來源:快科技

台積電:堅持本土戰略 我們絕不能將最尖端技術移至美國等海外

快科技8月9日消息,在接受媒體采訪時,台積電董事長劉德音重申,將將堅持本土戰略,不能將最尖端技術移至海外。

在劉德音看來,台積電已開始全球擴張,在美國和日本分別有兩家和一家工廠在建,後續德國也要新建一家工廠。

為了吸引台積電並將其生產設施引入美國,美國政府最初的努力促成了《晶片與科學法案》的出台,該法案旨在擴大美國半導體行業。

隨後,台積電已在亞利桑那州投資400億美元,建設兩家工廠,生產比其最先進晶片落後一兩代的晶片。

美國的想法雖然很美好,但顯示卻異常困難。台積電亞利桑那州工廠進展緩慢,台積電已部署了數百名本土技術人員來加快這一進程。

上個月,台積電將預期的啟動日期推遲了一年,至2025年,因此面臨著高昂的成本和管理挑戰。台積電與美國工人之間因文化差異而出現了內部矛盾。

盡管如此,劉德音也表示,他們將台積電最核心的技術和人才留在本土,這是該公司應對美國這一呼籲的戰略之一。

來源:快科技

台積電創始人張忠謀:美國公司將失去業務 中國將找到反擊的方法

8月5日消息,近日紐約時報采訪了台積電創始人張忠謀,並刊發了一篇題為《The Chip Titan Whose Life’s Work Is at the Center of a Tech Cold War》的文章。

在這篇文章當中,介紹了張忠謀在德州儀器等企業工作歷程中,形成開創晶圓代工模式想法的關鍵因素,創立台積電相關歷程,以及與蘋果和英偉達的合作。最後,張忠謀還談到了對於美國對華半導體限制的看法,他認為最終“美國公司將失去業務,中國將找到反擊的方法!”

原文由芯智訊編譯並經相關補充如下:

在一間俯瞰台北和台灣首都周圍叢林覆蓋的山脈的木板辦公室里,張忠謀(Morris Chang)拿出了一本印有彩色圖案的舊書。它的標題是“超大規模集成電路系統導論”,這是一本描述計算機晶片設計復雜性的研究生級教科書。92歲的張先生滿懷敬意地舉起了它。

“我想告訴你這本書的出版日期,1980年,”他說。他補充道,時機很重要,因為這是他面臨的難題中“最早的一塊”——不僅改變了他的職業生涯,也改變了全球電子行業的進程。

張忠謀從教科書中獲得的見解看似簡單:充當計算機“大腦”的微晶片可以在一個地方設計,但可以在其他地方製造。這個概念違背了當時半導體行業的標准做法——即廠商們自己設計並製造。

因此,在54歲的時候,當許多人開始更多地考慮退休時,張忠謀反而走上了一條道路——將自己的見解變成現實。這位工程師離開了美國,搬到了台灣,在那裡他創立了台積電(TSMC)。該公司雖然不設計晶片,但已成為世界上最大的尖端微處理器製造商,其客戶包括蘋果和英偉達等全球頂尖的晶片客戶。

如今,這家因張忠謀一個想法而存在的公司已經是一家價值5000億美元的巨頭,它製造的先進晶片被廣泛的應用到了智慧型手機、汽車、超級計算機和戰鬥機當中。其飛機庫大小的晶片工廠,即晶圓廠,是如此關鍵,以至於美國、日本和歐洲都向台積電示好,要求其在自己的國家建造這些工廠。在過去的十年裡,中國大陸也投資了數千億美元來重現台積電的所作所為。

張忠謀原本“不太可能”的創業之旅,成功幫助台灣成為了全球半導體的中心,調整了電子行業的運作方式,並最終描繪了一個新的地緣政治現實,在這個現實中,全球經濟增長的關鍵在於台灣這個小島上。

這讓張忠謀和他創建的台積電成為了全球關注的焦點。在他職業生涯的末期,作為一個更喜歡呆在幕後的人反思了他所建立的東西,以及不再被關注意味著什麼。

“這並沒有讓我感覺特別好,”張忠謀說,他於2018年退休,但仍出現在台積電的活動中。“我寧願相對默默無聞。”

最近,張忠謀在辦公室進行了三個小時的討論,他明確表示自己是美國人——他於1962年獲得美國公民身份——當時他創立的公司正處於美中技術冷戰的中心。即使科技領導層的競爭加劇,他也沒有給中國太多半導體霸權的機會。

“我們控制了所有的瓶頸,”張忠謀說,他指的是美國及其晶片製造盟友,如荷蘭、日本、韓國和台灣。“如果我們想扼殺他們,中國真的無能為力。”(“China can’t really do anything if we want to...

16nm後 台積電也開放7nm課程、技術:加快研究

台積電啟動了大學FinFET計劃,旨在為該行業培養未來的晶片設計人才,並推動7nm晶片研究。

據悉,大學生、教師和學術研究人員的教育訪問以16納米工藝設計套件(PDK)為中心,但台積電還在7納米提供多項目晶圓(MPW)服務。

教學設計資料以台積電N16製程為基礎,包含教程設計案例、培訓資料和教學視頻,帶領學生從傳統的平面電晶體結構進入FinFET設計。

對於研究項目,台積電為通過MPW製造的測試晶片提供N16和N7工藝設計輔助材料。其中包括邏輯、模擬和射頻(RF)方面的研究設計。

台積電業務發展高級副總裁Kevin Zhang博士說“通過台積電大學FinFET計劃提供我們的16納nm和7nm技術,我們為研究人員和學生開辟了一個全新的舞台,讓他們探索他們的想法,激發他們對令人興奮和快速發展的半導體領域的好奇心和熱情,”。

來源:快科技

台積電對外開放16nm FinFET技術:推動全球半導體發展

台積電突然對外公布了16nm FinFET技術,是不是有點意外?

據悉,宣布推出大學FinFET專案,目的在於培育未來半導體晶片設計人才並推動全球學術創新。

此專案開放大學院校師生與學術研究人員使用業界最成功的鰭式場效應電晶體(FinFET)技術之製程設計套件 (PDK),將其晶片設計學習經驗提升至先進的 16nm FinFET 技術。

按照官方的描述來看,這次開放的技術,是以台積電N16製程為主的教學用設計套件,包括教育設計案例、訓練資料、以及教學影片,引領學生從傳統平面式電晶體結構進入到鰭式場效應電晶體結構。

針對具有影響力的研究項目,包括應用於邏輯、類比與射頻的研究設計,台積電提供N16和N7製程設計相關套件,支持通過MPW服務生產的測試晶片。

據悉,台積電設計生態系統服務夥伴已准備就緒和參與大學FinFET專案的學者建立聯系。

來源:快科技

RTX 40顯卡從三星8nm升級台積電5nm後:黃仁勛感到失望

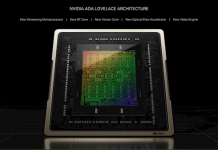

這一代RTX 40系顯卡採用了全新的Ada lovelace架構GPU核心,同時工藝製程升級到了台積電4N 5nm工藝。

和同期的AMD Radeon顯卡相比,NVIDIA這幾年在工藝上有點“不思進取”,先是12nm後是8nm,現在才到5nm,且還不是更優勢的4nm。

沒想到,NVIDIA CEO黃仁勛顯得比玩家們更失望。

編輯Dave Altavilla在RTX 40系顯卡的媒體溝通會上提到,從三星8N到台積電4N,這一升級令人印象深刻,那麼新的工藝給Ada架構帶來了哪些增益呢?

老黃的回答有些出人意料,從三星8N到台積電4N,微縮層面的提升大約在15%左右,但非常不幸的是,成本增幅超過了15%。

黃仁勛還表示,大概從7nm開始,摩爾定律的曲線就開始放緩,雖然還沒到止步不前的直線,但實際上已經失效。

老黃繼續指出,隨著工藝技術逼近物理極限,生產的復雜性也急劇增加,在Fab(晶圓廠)完成所有步驟的時間已經膨脹到4個月之久。老黃坦言,這也不是台積電有意拖延或者想要榨取利潤,而是真的需要這麼多步驟,設備也更貴了。

來源:快科技

台積電4N 5nm威武 4080 12GB電晶體竟遠超3090Ti 卻小了一半

NVIDIA Ada Lovelace RTX 40系列採用了特殊的台積電4N工藝,NVIDIA定製版本,

事實上,台積電5nm家族版本非常豐富,包括標準版N5、性能增強版N5P、N4、N4P、N4X、NVIDIA 4N。

雖然命名上很有迷惑性,但是台積電4N工藝在規格上還是不錯的,遠勝RTX 30系列的三星N8 8nm。

AnandTech獲悉了RTX 40系列首發三個核心的確切面積、電晶體數量,如下:

- RTX 4090 AD102:608平方毫米、763億電晶體、1.255億/平方毫米

- RTX 4080 16GB AD103:378.6平方毫米、459億電晶體、1.211億/平方毫米

- RTX 4080 12GB AD104:294.5平方毫米、358億電晶體、1.211億/平方毫米

三個核心在單位平方毫米上集成的電晶體都超過了1.2億個,AD103、AD104還完全一樣,遠遠超過了台積電8nm工藝RTX 3090/Ti GA102核心的4510萬個。

更驚人的是,AD104作為一個小核心,電晶體數量比GA102大核心還要多足足75億個,但面積還不到後者的一半,縮小了多達53%!

另外,Ada架構達到增加了ROP光柵單元的數量,三個核心分別92個、112個、80個,可大大改善傳統光柵遊戲性能。

二級緩存也分別增加到96MB、64MB、48MB,有望明顯提升帶寬。

來源:快科技

RTX 40顯卡的「4N」工藝是什麼鬼?原來定製台積電5nm

之前傳聞顯示,RTX 40系列將採用台積電4nm製造工藝,而在正式發布的時候,官方標注為“4N”,和台積電說的“N4”正好反過來。這是什麼鬼?

我們的第一反應,是這屬於定製版的台積電4nm,結果只猜對了一半。

根據快科技了解,4N工藝確實是NVIDIA與台積電定製的,但並非4nm,而是5nm,所以完整說法應該是台積電4N 5nm工藝。

這也再次證明,台積電的4nm、5nm工藝並無本質區別,前者主要是提高了電晶體集成度。當然了,總要比RTX 30系列的三星N8 8nm強太多了。

按照黃仁勛的說法,憑借新的架構和工藝,RTX 40系列的能效是RTX 30系列的兩倍。

數據顯示,Ada Lovelace架構的大核心AD102集成了763億個電晶體,核心面積608.4平方毫米,密度為1.255億個/平方毫米,內置18176個CUDA核心、142個第三代光追核心、568個第四代張量核心。

相比之下,三星8nm Ampere GA102核心是283億個電晶體、628平方毫米,密度為4510萬個/平方毫米。

換言之,台積電4N的集成密度是三星N8的足足2.8倍!

(還是有廠商誤寫作4nm)

來源:快科技