Tag: CFET

下一代CFET電晶體密度翻倍:英特爾、台積電和三星展示各自方案

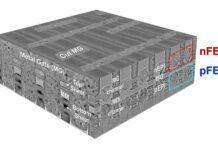

在上周的IEEE IEDM會議上,英特爾、台積電(TSMC)和三星展示了各自的CFET電晶體方案。堆疊式CFET架構電晶體是將n和p兩種MOS器件相互堆疊在一起,未來將取代GAA(Gate-All-Round),成為新一代電晶體設計,以實現密度翻倍。

英特爾是首個展示CFET方案的晶圓代工廠,早在2020年就公開了首個早期版本。這次英特爾介紹了CFET製造的最簡單電路之一,即反相器的幾項改進。CMOS反相器將相同的輸入電壓發送到堆棧中兩個設備的柵,並產生一個邏輯上與輸入相反的輸出,而且反相器在一個鰭上完成。英特爾同時還將電晶體使用的納米片數量從2個增加到3個,垂直間隙也從50nm減小到30nm。

目前5nm製程節點的柵極間距為50nm,不過這是使用單側互連的簡單FinFET。三星展示的CFET方案里,柵極間距為45/48nm,比起英特爾的60nm要更小。盡管三星的CFET原型里45nm柵極間距版本性能有所下降,但研究人員認為通過對製造過程的優化可以解決這個問題。三星成功之處是能夠電氣隔離堆疊的n和p兩種MOS器件的源和漏,關鍵步驟是使用一種涉及濕化學品的新型干刻蝕來替代濕法刻蝕。另外與英特爾單個電晶體使用3個納米片不同,三星是成對電晶體使用單個納米片。

台積電與三星一樣,設法將柵極間距控制在48nm,其CFET方案的特點包括一種在頂部和底部電晶體之間形成介電層的新方法,以保持間距。納米片通常由矽和矽鍺的交替層形成,台積電嘗試使用矽鍺專用刻蝕方法,在釋放矽納米線之前於兩個電晶體之間構建隔離層。

據了解,CFET技術轉化為商業大規模使用大概還需要7到10年的時間,在此之前仍然有許多前期准備工作要完成。 ...

英特爾和台積電披露下一代CFET電晶體進展,未來將取代GAA技術

據eeNewEurope報導,英特爾和台積電(TSMC)即將在IEDM 2023上公布下一代CFET電晶體的進展情況。未來堆疊式CFET架構將取代GAA(Gate-All-Round),成為新一代電晶體設計。

CFET電晶體將n和p兩種MOS器件相互堆疊在一起,需要使用高精度和高功率的High-NA EUV光刻機來製造。其概念最初由IMEC研究所於2018年提出,雖然早期探索研究主要集中在學術界,不過英特爾和台積電已經冒險進入該領域,積極展開下一代電晶體架構的研究。

目前英特爾已建立了一個單片式3D CFET,將三條n-FET納米片分布覆蓋在三條p-FET納米片之上,並保持30nm的垂直間隙。英特爾將報告取名為「採用電源通孔和直接背面組件觸點60nm閘極間距的堆棧式CMOS逆變器演示」,描述了在60nm閘極間距上使用CFET的功能逆變器測試電路。該設計還採用垂直分層雙電源漏外延和雙金屬閘極堆棧,並結合了英特爾的PowerVia背面供電技術。

台積電將討論其實際操作CFET的方法,這是為製造邏輯晶片而量身定製的,具有48nm柵極間距。台積電的設計強調了層狀n型納米片電晶體置於p型電晶體之上,使其具有跨越六個數量級的開/關電流比。台積電已經證明了其設計的耐用性,90%以上的電晶體成功經受住了測試。不過台積電也承認,要充分利用CFET技術的能力,還有更多的功能需要吸收,目前正在進行的工作是實現這一目標的關鍵一步。

CFET技術為電晶體設計帶來了明顯的轉變,其允許垂直堆棧兩個電晶體安裝在一個電晶體的面積內,可進一步提升晶片上電晶體的密度。這種設計不僅為提高空間使用提供解決方案,而且還促進了更精簡的CMOS邏輯電路布局,有利於提高設計效率。CFET的既有結構可以減少寄生效應,從而為提高性能和功率效率創造了可能。此外,還能與背面供電等新技術相結合,可簡化製程技術的復雜性。 ...

台積電介紹其CFET電晶體技術:已進入實驗室,距離量產仍很遙遠

近日英特爾在比利時安特衛普舉行的ITF World 2023上,概述了幾個關鍵領域的最新發展,其中之一便是英特爾未來將採用的堆疊式CFET電晶體架構。作為現階段半導體製造技術的龍頭,台積電(TSMC)也在2023歐洲技術研討會活動中,介紹了其未來的GAAFET及CFET電晶體技術。

據AnanadTech報導,台積電透露其CFET電晶體已經進入到實驗室,正在進行性能、效率和密度的測試,與GAAFET相比,這幾方面都會更有優勢。不過CFET需要一些額外的製造步驟,才能使晶片按預期工作。CFET電晶體將n和p兩種MOS器件相互堆疊在一起,需要使用高精度和高功率的High-NA EUV光刻機來製造。

台積電正在研究各種電晶體設計類型,這些研究項目需要很長時間,而CFET技術可能是未來最有可能的候選之一,不過現階段不能說已經超越Nanosheet,而且CFET電晶體需要將新材料整合到製造過程中,從而導致對應的製程節點需要更大的投資。唯一肯定的是,台積電在2nm工藝起會引入GAAFET電晶體技術。

台積電使用FinFET電晶體已經有十年了,期間經歷了五代工藝,正常來說GAAFET電晶體應該也會使用幾代產品,至於CFET電晶體距離大規模量產仍然很遙遠。 ...

英特爾介紹新的堆疊式CFET電晶體架構:下一代GAA技術

近日在比利時安特衛普舉行的ITF World 2023上,英特爾技術開發總經理Ann Kelleher概述了英特爾在幾個關鍵領域的最新發展,其中之一便是英特爾未來將採用的堆疊式CFET電晶體架構。這是英特爾首次向公開介紹這種新型電晶體設計,不過沒有提及具體的量產日期或者時間表。

在2021年的「英特爾加速創新:製程工藝和封裝技術線上發布會」上,英特爾確認了其Intel 20A工藝上,將引入採用Gate All Around(GAA)設計的RibbonFET電晶體架構,以取代自2011年推出FinFET電晶體架構。新技術加快了電晶體開關速度,同時實現與多鰭結構相同的驅動電流,但占用的空間更小。據TomsHardware報導,Ann Kelleher稱RibbonFET將會在明年亮相。

英特爾還展示了下一代GAA設計的堆疊式CFET電晶體架構,允許堆疊8個納米片,是RibbonFET使用的4個納米片的兩倍,從而增加了電晶體密度。CFET電晶體將n和p兩種MOS器件相互堆疊在一起,以實現更高的密度。目前英特爾正在研究兩種類型的CFET,包括單片式和順序式,似乎未確定最後採用哪一種,或者是否還會有其他類型設計出現。

大概到2032年,電晶體將進化到5埃米,CFET電晶體架構的類型會發生變化不是什麼意外的事情。英特爾這次只是概述了其電晶體技術的大概發展路徑,並沒有做太多詳細的分享,以後應該會有更多細節信息公布。 ...