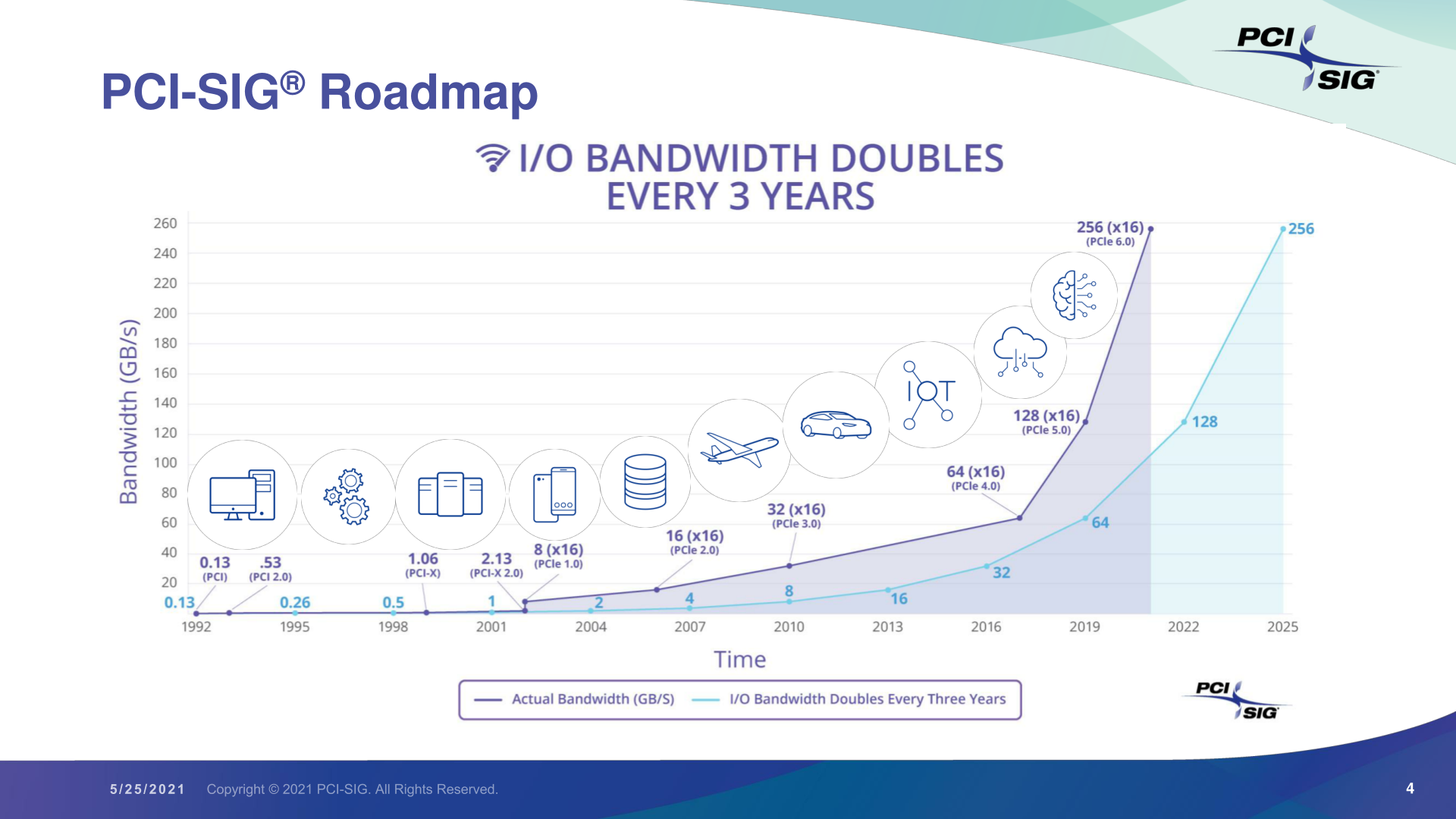

PCIe 4.0正在逐漸普及,PCIe 5.0即將在Intel Sapphire Rapids下代至強、Alder Lake下代酷睿上落地,PCIe 6.0也在有序推進之中。

PCI-SIG組織今天召開年度媒體會,通報了PCIe 6.0的最新進展,確認將在今年底如期發布最終正式版。

PCIe 6.0 0.7版草案在去年11月完成並發放給組織會員,PCI-SIG目前仍在搜集整理反饋,計劃在下個月發布0.71版草案,並入0.7版草案以來的所有新協議、電氣規格更新,但變化不會太大。

0.71版草案有30天的評估期,如果沒什麼問題的話就將轉入0.9版草案,也是正式版之前的最後一步。

PCI-SIG組織對於PCIe 6.0標準非常興奮,認為它堪比PCIe 2.0向PCIe 3.0的升級,後者是PCIe歷史上壽命最長的一代標準。

PCIe 6.0按照傳統繼續讓I/O帶寬翻番達到64GT/,應用到實際中,PCIe 6.0 x1單向實際帶寬8GB/,PCIe 6.0 x16單向帶寬128GB/、雙向帶寬256GB/。

如今廣泛使用的PCIe 4.0 x4 SSD,到時候只需要PCIe 6.0 x1就可以搞定。

PCIe 6.0將延續PCIe 3.0時代引入的128b/130b編碼方式,但加入全新的脈沖幅度調制PAM4,取代PCIe 5.0 NRZ,可以在單個通道、同樣時間內封包更多數據,以及低延遲前向糾錯(FEC)和相關機制,以改進帶寬效率。

很多人可能會疑問,PCIe 3.0的帶寬很多時候都用不完,PCIe 6.0有什麼用?顯然不是給消費級市場准備的,甚至不是一般的企業級、數據中心級應用,而是針對雲端、人工智慧、機器學習、邊緣計算等需要超高帶寬的領域,單個PCIe 6.0 x16就可以支持800G乙太網,還有各種加速器、FPGA、ASIC、存儲等等。

來源:快科技