Tag: Foveros

NVIDIA找上Intel代工:每月可產30萬顆AI晶片

快科技2月1日消息,NVIDIA AI GPU晶片持續火爆,占領全球絕大部分市場,但是台積電的晶片和封裝產能卻遭遇瓶頸,NVIDIA於是又找上了Intel,後者的IFS代工業務也迎來了大客戶。

據報導,NVIDIA、Intel之間的代工合作將從2月份開始,規模達每月5000塊晶圓。

如果全部切割成H100晶片,在理想情況下最多能得到30萬顆,可以大大緩解NVIDIA供應緊張的局面。

作為對比,台積電在2023年年中已經可以每月生產最多8000塊CoWoS晶圓,當時計劃在年底提高到每月1.1萬塊,2024年底繼續提高到每月2萬塊。

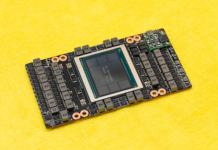

NVIDIA旗下的幾乎所有AI晶片,包括A100、A800、A30、H100、H800、GH200,全都依賴台積電CoWoS-S封裝技術,基於65nm的矽中介層。

與之最接近的就是Intel Foveros 3D封裝,基於22FFL工藝的中介層。

有趣的是,就在日前,Intel宣布已經在美國新墨西哥州Fab 9工廠實現了業界領先的半導體封裝解決方案的大規模生產,其中就包括Foveros封裝。

Intel沒有透露具體的產品,看起來很可能就是NVIDIA GPU。

來源:快科技

英特爾詳細介紹Intel 4製程工藝,稱Foveros封裝技術實現40年來重大架構變革

近日在英特爾馬來西亞科技巡展上,英特爾邏輯技術開發副總裁Bill Grimn詳細介紹了Intel 4製程工藝。根據IDM 2.0戰略,英特爾計劃在四年內實現五個製程節點,包括而Intel 4處於計劃中的第二個節點,將用於即將到來的Meteor Lake,也就是新一代面向移動平台的酷睿Ultra第1代處理器。

Intel 4將採用了EUV(極紫外)光刻技術,可使用超短波長的光,改善良品率和面積微縮,從而實現高能效,而且可應用EMIB和Foveros封裝技術,相比Intel 7可提供翻倍的電晶體密度,也為接下來的Intel 3奠定基礎。目前正在開發過程中的Intel 3將帶來密度更高的設計庫,增加驅動電流的電晶體並降低通孔電阻,其將更多地使用EUV光刻技術。

與Intel 7相比,Intel 4實現了兩倍的面積微縮,帶來了高性能邏輯庫,並引入了多個創新,包括引入EUV光刻技術,大幅簡化了互連架構的製程工藝,同時還支持微縮,使得Intel 4中的掩碼減少了20%,工藝步驟減少了5%;針對高性能計算應用進行了優化,可支持低電壓(<0.65V)和高電壓(高於1.1V)運行,相比Intel 7,Intel 4的ios功率性能提高了20%以上;另外高密度(金屬-絕緣體-金屬)電容器實現了卓越的供電性能。

Meteor Lake採用分離式模塊架構,由四個獨立的模塊組成,其中計算模塊首次採用Intel 4製程工藝打造,這也是首款內置神經網絡處理單元NPU的英特爾處理器。Meteor Lake的獨立模塊將通過Foveros先進封裝技術連接,利用高密度、高帶寬、低功耗互連,能夠把多種製程工藝製造的諸多模塊組合成大型分離式模塊架構組成的晶片復合體。

Foveros先進封裝具有諸多優勢,包括36u凸點間距,跡線寬度小於1微米;凸點密度提高近8倍;跡線長度小於2毫米;160GB/s/mm帶寬;功耗小於0.3 pJ/位。相比於Raptor Lake,Meteor Lake通過Foveros先進封裝使得低功耗晶片互連最大限度地減少分區開銷,同時小區塊提高了晶圓良率,初制晶圓更少,而且能夠為每個區塊選擇理想的矽工藝。

據英特爾封裝、組裝和測試技術開發高級總監Pat Stover介紹,英特爾通過包含五個步驟的工藝組裝Meteor Lake:

切割 -...

Intel四大先進封裝技術:既能蓋「四合院」 也能建「摩天樓」

隨著半導體製程工藝提升越來越困難,先進封裝技術的重要性則愈發凸顯,成為延續摩爾定律的關鍵。

Intel就一直在深入研究各種先進封裝技術,部分已經得到廣泛應用,比如EMIB、Foveros,部分已經准備就緒,比如Foveros Omni、Foveros Direct。

此前,

現在,Intel通過形象的動圖,詮釋了幾種封裝技術的原理和特點。

其實,處理器雖然封裝最開始的作用只是防水、防塵和散熱,但隨著製程技術逐漸逼近物理極限,為了滿足越來越高、越來越復雜的算力需求,同時提高能效比,追求可持續發展,先進封裝正變得越來越關鍵。

Intel的先進封裝技術,一方面能夠提升晶片互連密度,在單個封裝中集成更多功能單元,目標是到2030年在單個設備內集成1萬億個電晶體。

另一方面,它們可以滿足Intel自家產品、代工客戶產品的異構集成需求,讓不同供應商、不同工藝打造的芯粒(Chiplet)更好地協同工作,提高靈活性和性能,降低成本和功耗。

一、EMIB

意思是“嵌入式多晶片互連橋接”,原理就像蓋四合院,把不同的晶片放在同一塊平面上相互連接。

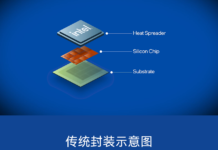

傳統的2.5D封裝是在晶片和基板間的矽中介層上進行布線,EMIB則是通過一個嵌入基板內部的單獨的晶片完成互連,可將晶片互連的凸點間距縮小到45微米,改善設計的簡易性,並降低成本。

二、Foveros

3D封裝技術,原理上也不復雜,就是在垂直層面上,一層一層地堆疊獨立的模塊,類似建摩天大樓一樣。

就像大廈需要貫通的管道用於供電供水,Foveros通過復雜的TSV矽穿孔技術,實現垂直層面的互連。

Foveros最早用於Lakefiled處理器,目前正在和EMIB聯手用於各類產品,最典型的就是Ponte Vecchio GPU加速器,使用了5種不同工藝、47個不同芯粒。

三、Foveros Omni

下一代封裝技術,可實現垂直層面上大晶片、小晶片組合的互連,並將凸點間距繼續縮小到25微米。

四、Foveros Direct

使用銅與銅的混合鍵合,取代會影響數據傳輸速度的焊接,把凸點間距繼續縮小到10微米以下,從而大幅提高晶片互連密度和帶寬,並降低電阻。

Foveros Direct還實現了功能單元的分區,使得模塊化設計配置靈活、可定製。

,Intel還展示了最新的混合鍵合(hybrid bonding),將互連間距繼續微縮到驚人的3微米,實現了准單片式的晶片。

也就是說,整合封裝後的互聯密度、帶寬都非常接近傳統的單片式晶片,不同芯粒之間連接更加緊密。

來源:快科技

史無前例的底層重構 Intel 14代酷睿Meteor Lake大變:性能提升21%

本周Intel披露了製程工藝的最新進展,其中Intel 4已經准備投入量產,下一代客戶端處理器Meteor Lake將首發。

不出意外的話,Meteor Lake流星湖就是第14代酷睿。

據媒體報導,Intel指出,其下一代PC處理器已經達到了一個技術里程碑。

這里面有兩層意思,其一是工藝疊代到Intel 4,雖然是之前的7nm EUV,但其實相當於友商的4nm。

按照Intel 6月份的說法,相較於13代酷睿的Inte 7,Intel 4可實現工藝層面21.5%的性能提升以及相同性能下多達40%的功耗減少。

其二就是架構設計前所未有的創新,14代酷睿Meteor Lake不再是一顆大晶片走天下,而是四顆Chiplet小晶片採用Foveros 3D封裝到一起。傳言除了CPU核採用Intel 4,核顯和I/O Die不排除找台積電3nm/4nm代工的可能。

值得一提的是,Intel還定於12月16日晚23點30分舉辦投資者會議,公布PC處理器新路線圖。

來源:快科技

曝14代酷睿將混搭工藝:Intel製造7nm CPU、台積電操刀3nm GPU

上周,有媒體在Intel位於美國的Fab42工廠拍到了14代酷睿Meteor Lake晶片的「果照」,讓人大呼驚喜。

此前公布的資料顯示,Meteor Lake基於Intel 4(7nm)工藝製造,採用Foveros封裝技術,集合計算、SoC-LP(I/O模塊)、GPU(96~192 EU)等三大單元。

在一份最新爆料中給出了這款處理器的新細節,比較出人意料的是,Meteor Lake實際上只有CPU部分是Intel製造,而GPU和SoC-LP實際上將交給台積電代工。

具體來說,GPU單元採用台積電3nm,SoC-LP(整合DDR5/LPDDR5、PCIe 5.0、USB4控制器等)則會基於台積電5nm或者4nm打造。

從Meteor Lake的架構來說,這並不讓人意外,Intel做出這樣的選擇,應該是基於技術指標、產能、成本等綜合考慮後的結果。

實際上,Meteor Lake並非新CEO帕特基辛格上任後台積電為Intel代工的首款重磅產品,明年一季度推出的Xe遊戲顯卡,就會採用台積電的6nm製造。

來源:快科技

Intel 7nm塵埃落定2023年降臨桌面處理器 3D混合架構

在今晨的「Intel Unleashed: Engineering the Future(Intel發力:以工程技術創未來)」活動中,Intel CEO帕特基辛格(Pat Gelsinger)宣布了IDM 2.0願景,簡單來說包括擴大內部製造能力、積極採用三方代工和對外提供代工服務三大部分。

對於普通消費者來說,一個值得關注的確認是,Intel表示EUV極紫外光刻已經引入其7nm工藝,預計今年二季度流片首款客戶端CPU。

這里的首款7nm客戶端CPU研發代號Meteor Lake,計劃2023年開始向客戶出貨,7nm數據中心處理器Granite Rapids也會在同年交付。

關於Meteor Lake,它還將使用Intel的Foveros設計技術,也就是基於裸片的3D封裝。它的意義在於,如果GPU、北橋等是台積電其它工藝代工,同樣可以和CPU核整合在一起。

就爆料的路線圖來看,Meteor Lake可能對應14代酷睿,在11代酷睿桌面Rocket Lake之後,Intel還有10nm的12代酷睿Alder Lake、10nm的13代酷睿Raptor Lake。

PS:按照ASML的說法,Intel的7nm EUV相當於台積電的5nm。

圖為爆料路線表,僅供參考作者:萬南來源:快科技

Intel 5核心性能首測 遠不如超低功耗Y系列

日前,Intel正式發布了,首次採用3D Foveros立體封裝,集成一個Sunny Cove大核心、四個Tremont小核心,類似ARM big.LITTLE理念,同時集成GPU核顯等模塊,PoP整合封裝記憶體,而整體體積只有12×12×1毫米,熱設計功耗僅為7W,待機功耗低至2.5mW。

那麼,這種五核心五線程處理器的實際性能到底如何?NoteBookCheck近日測試了一款配備i5-L16G7的三星Galaxy Book S,結果……挺糾結的。

i5-L16G7 CPU核心頻率1.7-3.0GHz,核顯部分集成64個單元,最高頻率500MHz。本次主要測試了CPU性能,跑的是不同版本的CineBench、GeekBench。

一大四小五個核心(沒有超線程)的設計,不僅對於Intel是第一次,對於Windows系統來說也很新鮮,在不同核心間分派適當的負載就異常關鍵。

Windows任務管理器中可以看到五個CPU核心,但沒有明確標注哪個是Sunny Cove、哪四個是Tremont,從負載看應該第五個是Sunny Cove。

CineBench渲染測試中,大核心並沒有用盡全力,只有偶爾全速運行,其他時間占用率都只有10%左右,而四個小核心很賣力,要麼持續100%運行,要麼間歇起伏,看起來核心調度並沒有最優化。

更糟糕的是,大核心的加速頻率根本達不到標稱的3.0GHz,最高只有2.4GHz,更進一步影響了性能,但不知道是Intel睿頻算法問題,還是三星筆記本設計問題。

結果就是,i5-L16G7的實際性能表現很糟糕,無論單核心還是多核心都遠不如之前的Y系列超低壓處理器,綜合只有八代超低壓酷睿i3-8100Y的大約三分之一,甚至不如奔騰5405U。

畢竟,雖然名義上是五核心,但真正需要性能的時候,要麼是四個孱弱的低功耗小核心,要麼只有一個相對高性能的大核心。

猜你喜歡的商品>>作者:上方文Q來源:快科技

Intel史上首款5核心揭秘 三個第1、待機功耗低至2.5mW

去年初的CES 2019大會上,Intel首次宣布了全新的3D Foveros立體封裝技術,以及首款基於該技術的處理器,代號Lakefield。

一年半過去了,這款別致的處理器終於正式發布了,官方稱之為「具備混合技術的酷睿處理器」(Intel Core processors with Intel Hybrid Technology)。

Intel Lakefield採用了Foveros立體封裝技術、混合CPU架構,可在最小的尺寸內提供卓越的性能、全面的Windows兼容性,能在超輕巧的創新設備外形下提供辦公和內容創作體驗。

它是第一款集成PoP整合封裝記憶體的酷睿處理器,第一款待機功耗低至2.5mW的酷睿處理器,也是第一款原生集成雙內部顯示流水線的Intel處理器,非常適合折疊屏、雙屏設備。

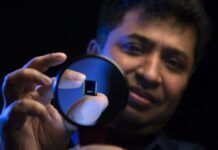

得益於立體封裝和超高集成度,整顆處理器的尺寸只有12×12×1毫米,還不如一枚普通硬幣大。

Lakefield內部可分為四層結構,其中頂層是PoP整合封裝的LPDDR4X記憶體,最大容量8GB,最高頻率4267MHz;第二層是P1274 10nm工藝製造的計算層,內部包括CPU核心、GPU核心、顯示引擎、緩存、記憶體控制器、圖像處理單元(IPU)等;第三層是P1222 22nm工藝製造的基底層,內部包括I/O輸入輸出單元、安全模塊、ISH、EClite等,成本低,漏電率低;最下方則是封裝層。

同時,它還可以外部擴展連接XMM 7560 4G基帶、PMIC電源管理單元、Wi-Fi 6 AX200無線網卡等等。

CPU核心包括一個Sunny Cove架構的大核心(Ice Lake家族同款),四個Tremont架構的小核心(Atom家族同款),分別負責前台、後台任務,並設計了專門的硬件調度機制,整合在操作系統內,並支持支持CPU和操作系統調度程序之間實時通信,從而在正確的內核上運行最合適的負載,優化性能和能效。

Intel宣稱,加入一個大核心後,相比四個小核心網絡性能可提升最多33%,能效則可提升最多17%。

值得注意的是,Tremont小核心天然不支持超線程,Sunny Cove大核心雖然支持,但這里並沒有開啟,所以整體式五核心五線程。

對比八代酷睿家族的超低功耗i7-8500Y(TDP 5W),Lakefield的封裝面積縮小多達56%,待機功耗降低多達91%,能效提升多達24%,單線程性能提升多達12%,圖形性能提升多達1.7倍,GPU AI性能提升可超過2倍。

Lakefield家族有兩款型號,均為五核心,其一為酷睿i5-L16G7,CPU部分基準頻率1.4GHz,全核睿頻最高1.8GHz,單核睿頻最高3.0GHz,UHD核顯部分集成64個執行單元,頻率500MHz,熱設計功耗為7W。

其二是酷睿i3-L13G4,CPU基準、全核睿頻、單核睿頻分別將至0.8GHz、1.3GHz、2.8GHz,核顯執行單元減少到48個,其他同上。

基於Intel Lakefield處理器的產品首批有三款,其中三星Galaxy Book S將從6月起在部分地區上市,聯想ThinkPad...

三星全球首發Intel Lakefield 5核心處理器 10nm+22nm混搭

三星今天正式發布了新款Galaxy Book S筆記本,這也是第一款搭載Intel Lakefield 3D Foveros封裝處理器的產品,但沒有透露具體型號和規格,而是稱之為「Intel Core processor with Intel Hybrid Technology」(Intel混合技術酷睿處理器)。

根據此前消息,三星使用的是一顆酷睿i5-L16G7,集成一個大核(Sunny Cove)、四個小核(Tremont)共五核心CPU,三級緩存4MB,主頻最高3.0GHz,同時集成第11代核顯UHD,64個執行單元,其中計算層使用10nm工藝,基底層則是22nm工藝。

三星Galaxy Book S身材輕盈,最薄處只有6.2毫米,最厚也不過11.8毫米,重量僅為950克,採用一塊13.3英寸1080p LCD觸摸屏,窄邊框設計,頂部攝像頭100萬像素,支持Windows Hello。

其他配置還有8GB LPDDR4X記憶體、256/512GB eUFS存儲、Giga+ Wi-Fi 6 2x2無線網卡(藍牙5.0)、4G LTE Cat.16(可選)、AKG四立體聲揚聲器(杜比Atoms)、指紋識別、兩個USB-C、一個3.5mm耳麥、一個microSD讀卡器(最大1TB)、42Whr電池(續航時間沒說)。

三星Galaxy...

Intel酷睿i5-L15G7處理器現身 10nm 3D封裝、5核x86混合架構

Intel去年對外介紹了名為Foveros的3D封裝技術,該技術將首次用於Lakefield家族處理器,也就是Intel版的「big.LITTLE」x86混合架構。

日前,有網友發現Userbenchmark上出現了一款名為Core i5-L15G7的Lakefield處理器,從名字來看,它的定位應該比之前的Core i5-L16G7略低。

識別出來的信息有5核5線程,基礎頻率1.4GHz,加速1.55GHz,遊戲跑分僅在41%的競品之上。

爆料人稱,Core i5-L15G7的加速頻率應該至少可以到2.9GHz左右,三緩4MB,最終成品仍在調試中。

不出意外的話,Core i5-L15G7的大核是10nm Sunny Cove(Ice Lake同代),四小核是Atom,它們連同GPU、記憶體、I/O等封裝在12平方毫米的空間內,用於筆記本、迷你機、網絡設備等極大地節約了體積。

作者:萬南來源:快科技

Intel放出Lakefield的高清大圖,快來看看這顆神奇的五核處理器

Intel的Lakefield是一個相當之有趣的處理器,它是一個五核心的x86處理器,並且里面封裝有兩種完全不同的架構的x86核心,甚至內部的製程工藝都是不同的,它是首款採用Intel

Foveros 3D封裝技術的產品,該系列處理器將會封入一個Sunny

Cove和四個Tremont作為計算核心,形成一大四小的配置,可以說是Intel方面的bit.LITTLE方案,Intel此前宣傳過它的體積只有12×12mm,厚度為1.00mm,尺寸相當之小,有多小呢?Intel現在放出了它的高清大圖,要拿放大鏡才能看清楚這塊晶片。

Lakefield SoC包含四個層,前兩層是由PoP封裝的DRAM記憶體所組成,由兩塊BGA

DRAM堆疊在一起,第三層則是由10nm工藝打造的CPU與GPU,最底層則是由22nm工藝打造的I/O與緩存層。

10nm工藝的計算晶片包含一個Sunny

Cove大核,該核心擁有自己的L2緩存,不過它核心外還有0.5MB的MLC中等級緩存,四個Tremont小核,它們共享1.5M

L2緩存,所有核心共享4MB的LLC緩存,記憶體控制器是4*16位的,支持LPDDR4,整合了Gen 11核顯,有64個EU單元,Gen

11.5顯示控制器還有新的IPU,支持DP 1.4。

位於底部的基底層作為SoC的緩存與I/O模塊,應該整合了PCI-E控制器並擁有PCH晶片的部分功能,為SoC提供豐富的I/O功能,由於SoC直接整合了記憶體模塊,所以可以讓移動設備的主板變得更為小巧,而且這塊處理器的TDP不會超過7W,無需採用主動散熱方案。

此前UserBenchmark資料庫上已經可以找到他的信息,名字叫Core i5-L16G7,是五核心五線程的,我還以為Sunny

Cove大核會支持超線程技術呢,結果沒有,它的基礎頻率為1.4GHz,平均加速頻率為1.75GHz,應該是被功耗所限制住了。其記憶體控制器的規格還是比較高的,從記錄來看是支持LPDDR4X-4266的。

這是Intel的公版解決方案,處理器旁邊那塊應該是BGA

SSD或者eMMC,處理器內部已經整合了所有的I/O控制器,應該無需搭配PCH使用,這款處理器的出現讓輕薄型PC的設計變得更加靈活,特別適合新興的雙屏或者可折疊類PC。

迄今為止Intel Lakefield處理器已經被三款產品所使用,分別是微軟的雙屏設備Surface Neo,三星的Galaxy Book

S,還有聯想的ThinkPad X1 Fold折疊屏電腦。 ...

Intel Lakefield處理器官方近照 3D 5核心的奧妙

去年初的CES 2019大展上,Intel正式揭曉了全新的3D Foveros立體封裝,首款產品代號Lakefield,已經獲得客戶和專業機構的認可,被視為Soc處理器未來的新方向之一。

Foveros 3D封裝改變了以往將不同IP模塊使用同一工藝、放置在同一2D平面上的做法,改為3D立體式堆棧,而且不同IP模塊可以靈活選擇最適合自己的工藝製程。

近日,半導體產業和分析機構The Linley Group授予Intel Foveros 3D封裝技術2019年分析師選擇獎之最佳技術獎,並給予極高評價:「這次評獎不僅是對於(Foveros)芯片設計和創新的高度認可,更是我們的分析師相信這會對(芯片)未來設計產生深遠影響。」

Lakefield在極小的封裝尺寸內取得了性能、能效的優化平衡,並具備最出色的連接性。它的面積僅有12×12毫米,厚度不過1毫米,其中混合式CPU架構融合了10nm工藝的四個Tremont高能效核心、一個Sunny Cove高性能核心,可以智能地在需要時提供最佳辦公性能,不需要的時候則可以節能延長續航時間,另外還有22nm工藝基底和其他記憶體、I/O模塊。

迄今為止,Lakefield已經贏得了三款產品設計,一是微軟去年10月宣布的雙屏設備Surface Neo,二是三星隨後推出的Galaxy Book S,三是聯想在CES 2020上拿出的ThinkPad X1 Fold。

同時,Intel也放出了Lakefield的最新照片,包括近距離芯面封裝圖、主板全圖:

作者:上方文Q來源:快科技

疑似Lakefield處理器曝光:命名規則類似Ice Lake-U/Y系列

Intel正在開發的Lakefield處理器採用的是自家全新的Foveros 3D封裝,預計在今年年末登場的Surface Neo將會使用該系列的處理器。根據Intel官方公布的信息,該系列處理器將會封入一個Sunny Cove和四個Tremont作為計算核心,形成一大四小的配置,可以說是Intel方面的bit.LITTLE方案。最近在UserBenchmark上面就出現了這麼一款五核心的處理器,型號為Core i5-L16G7,這可能也是Lakefield首次以有型號處理器形式出現的記錄。

從命名方式來看,Lakefield延續了Intel在Ice Lake-U/Y系列處理器上面使用的命名規則,不過有一定的改變,比如該系列處理器的首位字母可能將會使用"L"來代表這是Lakefield家族,其後兩位是代表規格的數字,最後則是之前見過的代表圖形核心等級的Gx,不過Lakefield的可能跟Ice Lake-U/Y上面的Gx不一樣,因為面向的平台不一樣,可能會在核顯規模上面進行了控制,但其架構還是直接套用的Gen 11。

從UserBenchmark讀取到的信息來看,Core i5-L16G7的基礎頻率為1.4GHz,平均加速頻率為1.75GHz,應該是被功耗所限制住了。其記憶體控制器的規格還是比較高的,從記錄來看是支持LPDDR4X-4266的。

目前已經有多款設備確定使用該系列處理器,其中多為可折疊的筆記本電腦,比如聯想的ThinkPad X1 Fold和X1 Fold,而這次UserBenchmark的記錄是來自於一款三星的筆記本,可能是Galaxy筆記本產品線的新品。我們也即將看到該系列處理器的真實表現,Intel首次使用Foveros封裝技術的產品的實際表現究竟會如何呢? ...

Lakefield將會在明年迎來Refresh版本:未來可能直接整合5G基帶

Lakefield是Intel新的大小核混合處理器,也是首個採用「混合架構」的x86處理器。它採用了Intel最新的Foveros封裝工藝,這是Intel獨家的3D堆疊封裝工藝,它在減小整個封裝尺寸的同時為Die之間的互聯提供了超高的帶寬。截至目前已經有兩款產品宣布將使用Lakefield處理器了,它們分別是三星的Galaxy Book S和微軟的Surface Neo,都將會在明年登場。不過Intel最近在IEDM 2019上面透露了Lakefield處理器可能將會在明年迎來Refresh版本。

在IEDM 2019上,Intel的工程師向AnandTech透露了Lakefield的Refresh版本將會在2020年末上市,並且他還稱現在第一代Lakefield處理器已經上市了,不過那是我們普通消費者拿不到的產品。而這個時間點正好和Surface Neo的發售時間相重合,很有可能我們在Surface Neo上面可以直接看到這款經過Refresh的混合處理器。

那麼它會"Refresh"些什麼東西呢?因為Foveros工藝擁有著非常高的靈活性,所以處理器上面的各個組成部分都有可能被小升級一下,比如說計算核心小升級或者是I/O部分小升級。而考慮到最近Intel宣布了和MTK在5G技術、產品上面進行合作,加上Foveros這項堆疊工藝,我們完全有可能會看到一款集成5G基帶的x86處理器,這也可能是"Refresh"的定義。

另外一款將採用Foveros封裝工藝的產品將是還沒正式發布的Xe GPU,它的HPC版本將會使用Foveros提升自己的計算規模,以更好地適應HPC的用途。近幾年Intel推出了不少領先的封裝技術,在後摩爾定律時代,當製程工藝無法再有效推動晶片規模增加時,更加優秀的封裝工藝就會派上更大的用處了,它可以幫助實現更大的計算規模。 ...

奇怪的五核設計,Intel Lakefield處理器現身3DMark資料庫

Lakefield是Intel首款採用「Foveros」的全新3D封裝技術打造的處理器的代號,它的結構就像一塊三明治,第一層是由PoP封裝的DRAM記憶體所組成,可由多塊BGA

DRAM堆疊在一起,第三層則是由10nm工藝打造的CPU與GPU,最底層則是由22nm工藝打造的I/O與緩存層。

Lakefield的計算核心內包括一個Sunny

Cove大核和四個Tremont小核,構成了類似於ARM的big.LITTLE架構形式,核顯則是和Ice Lake處理器一樣的Gen 11

GPU,擁有64組EU單元,現在@TUM_APISAK已經在3DMark的資料庫里面找到了這顆奇特的5核處理器,從截圖上可以看到它上面整合的是LPDDR4X記憶體,根據Intel給出的數據最高支持頻率4266MHz,比現在的Coffee

Lake處理器高多了。

至於它的性能嘛,鑒於它是一顆TDP 5W到7W的處理器,所以就別指望有多高了,它的圖形分數為11xx分,和使用UHD

620的Core

i5-8250U差不多,不過後者畢竟是顆15W的處理器,頻率應該高不少,CPU得分則是52xx,和奔騰金牌G5400差不多,畢竟只有一個大核,能有著水平已經不錯了。

Intel的計劃是在今年第四季度開始給廠家提供Lakefield的樣品的,從它出現在3DMark資料庫這事來看,這產品進度還是相當不錯的,設備製造廠應該可以才明年出拿出搭載Lakefield處理器的產品。 ...

Intel Lakefield SoC將直接整合記憶體,由Foveros 3D工藝打造

Intel在去年12月的「架構日」活動上公佈了名為「Foveros」的全新3D封裝技術,該技術首次引入了3D堆疊的優勢,可實現在邏輯芯片上堆疊邏輯芯片,當時Intel展出使用該技術製造的Hybrid

x86 CPU,也公佈了一些規格細節,但對此工藝並沒有說太多。

現在Intel在油管上放出了採用Foveros

3D封裝工藝所生產的Lakefield SoC的介紹視頻,從視頻上可以看出這個SoC至少包含四個層,前兩層是由PoP封裝的DRAM記憶體所組成,由兩塊BGA

DRAM堆疊在一起,第三層則是由10nm工藝打造的CPU與GPU,最底層則是由22nm工藝打造的I/O與緩存層。

10nm工藝的計算芯片包含一個Sunny

Cove大核,該核心擁有自己的L2緩存,不過它核心外還有0.5MB的MLC中等級緩存,四個Tremont小核,它們共享1.5M

L2緩存,所有核心共享4MB的LLC緩存,記憶體控製器是4*16位的,支持LPDDR4,整合了Gen 11核顯,有64個EU單元,Gen

11.5顯示控製器還有新的IPU,支持DP 1.4。

位於底部的基底層作為SoC的緩存與I/O模塊,應該整合了PCI-E控製器並擁有PCH芯片的部分功能,為SoC提供豐富的I/O功能,由於SoC直接整合了記憶體模塊,所以可以讓移動設備的主板變得更為小巧,而Lakefield

SoC本身也只有12*12mm那麼大,TDP不會高於7W,它的出現可以讓未來的移動設備變得更輕薄,並且有更強的續航能力。

但是目前還不知道這個Lakefield

SoC是否需要搭配PCH所使用,因為從上圖來看SoC下面那個大芯片看起來像是PCH芯片,當然目前無法確定那個到底是什麼。

來源:超能網