Tag: 工藝

2020年Intel TOP3技術創新 10nm工藝位列第二

2020年還有不到2周就過完了,年底又是一個回顧總結的季節了,Intel公司在這一年中有什麼技術創新呢?芯片業內人士給點評了一下,10nm SuperFin工藝位列第二。

推出這個評選的是推特用戶Witeken,他不僅經常爆料AMD/Intel最新信息,也是芯片行業的專業人士,評選的主要是芯片技術層面的,很專業。

根據他的選擇,2020年Intel第一大技術創新是Lakefield處理器上的Foveros 3D堆棧,這是一種新的3D封裝技術,可以把不通工藝的IP核心封裝在一起,Lakefield的5核心就是1個大4小,分別使用了10nm、22nm工藝的。

第二個創新是Tiger Lake上首發的10nm SuperFin工藝,這也是今年Intel在CPU工藝上最重要的一次進步,使用了全新的Super MIM器件,號稱實現了單節點內最大的性能提升,超過15%。

雖然很多人看工藝數字都覺得Intel的10nm SF工藝不如台積電7nm、5nm先進,但是別忘了,Intel在半導體技術上的根底還在,10nm工藝的創新確實不少,

第三大創新就是硅基光電子,帶寬是PCIe 6.0的6倍,這也是Intel布局未來半導體技術的一個重點領域,光電子技術也很領先,只是現在還沒大規模商業化。

其他還有3條新技術,分別涉及低溫工藝、A,MX指令集及Statix 10 NX FPGA芯片等,相比前面三條更加專業。

作者:憲瑞來源:快科技

西門子洗碗機,讓洗碗不再勞累:德國工藝,助力您的碗美生活

洗碗機,這一家電產品對於絕大多數國人家庭來說還是新興事物,目前國內家庭對於洗碗機的持有率僅有3%。然而隨著國內經濟的不斷發展以及人民追求生活水平質量的提高,洗碗機市場的需求大爆發是可以預見的,並且選購一台優秀的洗碗機著實能夠讓您的生活質量大幅提高,不僅讓您下班用餐之後免受洗碗勞累,還能使用到更加潔凈健康的餐具。在此,我推薦您使用西門子洗碗機SJ656X26JC,助力您實現「碗美生活」。

西門子這一品牌,相信大多數讀者都有所耳聞,它是目前世界頂級家電製造商之一,已經有170多年的歷史。在洗碗機領域更是深耕數十年,以德國公司一向的嚴謹研發生產洗碗機產品,其品質上乘、品控可靠,而今天小M推薦的這款西門子洗碗機SJ656X26JC更是其中的精品之作。

這款洗碗機精通多種實用功能,從清洗餐具到專業消毒,堪稱餐具管理專家。它對於餐具的清潔程度,更是手洗所無法比擬的。首先我們在手洗時哪怕洗的再乾淨,往往也都是表面功夫,洗潔精和溫水能夠有效地對抗油污,但是對於細菌卻收效甚微。而西門子洗碗機SJ656X26JC則是採用熱水+高壓的模式來實現油污細菌全清理,並且該機並沒有一個勁地採用超高溫,而是通過無數次的實驗證明了72℃的高溫能夠兼顧有效殺滅細菌和保護餐具,同時再加上32000Pa高壓噴水,國際頂尖食品工廠採用的巴氏消毒法也正是如此殺滅細菌的。

以高溫熱水加上高壓的模式為餐具消毒之後,餐具上自然不可避免地會留下水漬,而水分又是細菌繁殖的一大重要因素。即使西門子洗碗機對於細菌擁有99.99%的殺滅度,但是剩下0.01%的細菌又會高速繁殖。對此,西門子洗碗機SJ656X26JC在消毒之後,還會進行烘乾,將水分盡數蒸發。

在烘乾時,首先通過電量轉化熱能進行第一次烘乾,之後由於西門子洗碗機SJ656X26JC內部擁有獨特的晶蕾結構,會通過晶蕾發熱進行二次烘乾,徹底清除水分的同時做到避免水蒸氣外泄,這一設計可以說是獨具匠心。另外西門子洗碗機SJ656X26JC還擁有非常優秀的密封性——也就是說它可以兼職碗櫃職責,在消毒烘乾之後直接將餐具儲存,在下一餐時再拿出來,不僅方便,更節約了廚房空間。

西門子洗碗機已經得到了眾多國人家庭的青睞,除了為用戶節約時間,在殺滅細菌方面它也是一把好手。選擇西門子洗碗機SJ656X26JC,就是選擇了全新的碗美生活,馬上行動吧!

來源:kknews西門子洗碗機,讓洗碗不再勞累:德國工藝,助力您的碗美生活

10nm和AMD 7nm比是擠牙膏?Intel回應 數字命名技術帶來很多誤解

前不久,Intel發布了代號「Tiger Lake(老虎湖)「的第11代酷睿低功耗處理器,從里到外煥然一新,堪稱Intel近些年來最大的一次飛躍。

雖然依舊採用10nm工藝,但全新的SuperFin技術加持下,性能和響應速度都很很大提升,CPU性能提升20%,集成lris Xe核顯性能翻番,AI性能則提升了5倍之多,Wi-Fi 6無線網絡則為其提供3倍於Wi-Fi 5的速度。

Intel將其定義為「世界上最好的輕薄型筆記本處理器」。未來,將有150多款搭載11帶酷睿處理器的新輕薄本陸續上市。

近日,Intel中國零售銷售集團總經理唐炯接受新浪采訪時,除了11代酷睿本身,還談到了Intel與AMD之間的競爭關系。

相比AMD的7nm,Intel的10nm工藝是否有擠牙膏之嫌?面對這樣的問題,唐炯表示,用數字命名技術,實際上會帶來很多的誤解。在納米命名法上也是一樣,業界的大多數專家都認可,Intel的10nm工藝和台積電、三星的7nm工藝是大致相同的。

唐炯認為,數字命名法還有一個問題,數字它是一個單維度的,但是技術是多維度的。Intel有六大技術支柱,製程和封裝,架構的設計,互聯的技術,記憶體和存儲、安全、軟件,Intel最強的地方是把這麼多技術能夠快速整合在一起,來給用戶提供最合適的產品。

Intel第11帶酷睿的發布,大家都恨到一個非常大的進步,感覺把「牙膏」擠破的感覺,實際上也是把多種技術整合在一起,提供一個最好產品的很好的例子。

作者:朝暉來源:快科技

台積電透露2nm工進度 2023年風險試產 次年大規模投產

9月25日消息,據國外媒體報道,今年一季度順利量產5nm工藝的台積電,正在研發更先進的3nm和2nm芯片製程工藝,3nm工藝是計劃在明年風險試產,2022年下半年大規模投產。

3nm工藝投產之後,台積電下一步將投產的就將是2nm工藝,在2019年的年報中,台積電首次披露他們在研發2nm工藝。

在本周早些時候的報道中,外媒稱台積電2nm工藝的研發已取得重大進展,研發進入了高級階段,先於他們的計劃。

在量產時間方面,外媒在報道中指出,台積電對2nm工藝在2023年年底的風險試產良品率達到90%非常樂觀。

外媒根據目前的研發進展推測,台積電的2nm工藝將在2023年風險試產,2024年大規模投產。

台積電的2nm工藝若如外媒報道的那樣在2023年風險試產、隨後一年大規模投產,也就意味着他們仍將保持兩年投產一代新工藝的節奏。

台積電的7nm工藝是在2018年的4月份大規模投產的,5nm工藝在今年一季度投產,中間相隔約兩年;

5nm之後的3nm工藝,計劃在2021年風險試產、2022年下半年大規模投產,雖然距5nm工藝大規模投產的時間間隔超過兩年,但量產時間大概率會提前,屆時間隔預計也在兩年左右。

對於台積電的2nm工藝,外媒此前曾報道稱將會採用環繞柵極晶體管技術(GAA),不會繼續採用鰭式場效應晶體管技術。

2nm工藝在2023年開始風險試產,也就意味着台積電需要開始謀劃利用2nm工藝生產芯片的工廠。

對於工廠,外媒在上周的報道中曾提到,台積電負責營運組織的資深副總經理秦永沛,透露他們計劃在新竹建設2nm工藝的芯片生產工廠,建設工廠所需的土地已經獲得。

台積電董事長劉德音目前也透露,他們可能會擴展位於台中的晶圓十五廠,以增加2nm工藝的產能。

來源:快科技

中芯國際 N+1代工藝開始客戶導入、年底小批量試產

作為內地規模最大的晶圓代工廠,中芯國際的一舉一動都牽動人心。

近日有報道稱,在大規模量產14nm工藝後,中芯國際的N+1代工藝已經進入客戶導入階段,可望於2021年進入量產。

對此,中芯國際回應稱,該公司的第一代FinFET 14nm工藝已於2019年第四季度量產,第二代FinFET N+1工藝已經進入客戶導入階段,可望於2020年底小批量試產。

按照這樣的時間表推測,中芯國際N+1代工藝確實會在2021年規模量產。

N+1是中芯國際對其第二代先進工藝的代號,但從未明確具體數字節點,只是說相比於14nm性能提升20%、功耗降低57%、邏輯面積縮小63%、SoC面積縮小55%,之後的N+2工藝性能和成本都更高一些。

今年8月底的時候,中芯國際曾表示,N+1工藝進展順利,已經進入客戶產品驗證階段。

作者:上方文Q來源:快科技

歐美已開始研發1nm CPU技術 升級CFET晶體管?

在VLSI 2020上,IMEC發表了有關單片CFET的有趣論文,我有機會采訪了其中一位作者Airoura Hiroaki。在業界眾所周知,FinFET(FF)即將達到其定標壽命。

三星已經宣布,他們將在3nm的時候轉向水平納米片(Horizontal Nanosheets :HNS)。台積電(TSMC)保持3nm的FF,但預計將轉移到2nm的新架構。

假設英特爾當時仍在追求自己的技術,則預計英特爾將保留7nm的FF,然後再遷移至5nm的HNS。

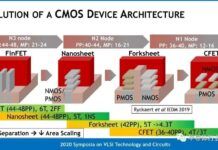

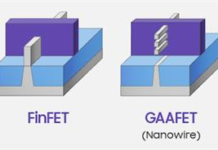

該行業最可能的路線圖是從FF到帶有或不帶有Forksheets的HNS,然後過渡到CFET(Complimentary FETs),請參見圖1。

Imec CMOS路線圖。

從以上技術藍圖來看,28納米使用了High-K/Metal Gate,16納米---14納米導入了FinFET,7納米---5納米採用了EUV曝光設備,此外,還將Co應用於Middle of Line(MOL)上。

MOL是一種將晶體管(FOEL)與多層配線(BEOL)連接在一起的孔(Via),雖然imec使用了Co,還有其他選擇項如Mo、Ru等。

此外,4納米---3納米中採用了具有Nanosheet結構的晶體管。

此次的VLSI座談會上,有關7納米、5納米、3納米的文章發布得比較多,然而,筆者卻發現將Gate All Around(GAA)的Nanosheet結構應用在這些節點上的情況是全球共通的認知。

同時從技術藍圖看,在2納米中,使用搭載了Buried Power Rail(BPR,在晶體管下埋入電源線的構造)的Forksheet晶體管;在1納米中,將會使用採用了BPR的Complementary FET(CFET)。

imec在其內部達成了以下共識:3納米之前採用Nanosheet、2納米採用Forksheet、1納米採用CFET。

也就是說,在此次VLSI座談會上,imec也是基於以上技術藍圖而做的發表。從上圖可以清晰地看出FinFET、Nanosheet、Forksheet、CFET的結構變化。

從FinFET到CFET,通過將Contact Poly Pitch(PP)做到最小、分離nMOS和pMOS,以達到縮小SRAM面積的效果。

Forksheet 和CFET通過堆疊nFET和pFET器件的CFET改善n到p的間距來縮小尺寸,見圖2。

CFET結構在當前的工作中,已經開發了「單片」(monolithic) CFET,方法是將單獨的硅片用於nFET和pFET,然後將它們粘合在一起,而按照順序(sequential),CFET則會將兩種類型的FET都製造在同一硅片上。

Imec聲稱單片技術比順序技術便宜,而順序技術要求SOI會增加襯底成本1%,見圖3。

單片CFET的成本優勢在1納米中,IMEC採用了將nMOS和pMOS縱向排列的CFET(如下圖8),雖然CFET的工藝流程非常復雜,但毫無疑問,極大地縮小了CMOS、SRAM的面積,達到了集成化。

問題是---是否做到了人們所期待的晶體管的特性,這是未來研發的關鍵。

我發現起始晶圓成本高出約1%,這有兩個原因,一是,我不相信順序CFET需要SOI,二是,SOI比標準晶圓貴了約1%。整體方法還將需要兩個起始晶圓,而不僅僅是一個。

我認為這種成本分析需要更多的調查。在單片方法中,nFET和pFET在分離的晶圓上製造,從而可以針對該器件優化每個器件的製造流程。每個晶片的處理流程如圖4所示。

圖4.單片CFET的工藝流程。

隨着我們朝N3方向發展,n到p的分離減少了寄生效應並提高了性能。同樣,通過從FF移至GAA)可以在所有四個側面而不是三個側面上提供一個柵極,從而改善了靜電控制。

這項工作中製造的單片CFET為下一代器件提供了順序CFET的替代方案,需要進一步研究。

來源:快科技

拿下驍龍875、RTX 30訂單 三星半導體狂追台積電

在全球晶圓代工製造行業,台積電可以說一家獨大,不僅份額超過50%,而且牢牢抓住了7nm、5nm先進工藝,三星雖然排名第二,但是差距甚大。

根據TrendForce的預測,020年第三季度全球前十大晶圓代工廠營收預測排名中,台積電穩居第一,市場份額達到53.9%。

三星排名第二,但份額只有17.4%,格芯(GlobalFoundries)第三,聯電第四,中芯國際排名第五,這三家跟台積電差距更大。

其他廠商遠低於台積電,主要原因在於先進製程上被台積電獨占,特別是當前最先進的7nm及5nm節點,唯一能跟台積電掰手腕的就是三星了。

蘋果、華為、聯發科、AMD等廠商基本上都是台積電的主力客戶,特別是蘋果、華為兩大移動芯片大戶。

三星在這方面一直進展不順,前幾年用14nm工藝代工了驍龍820處理器,但是之後的10nm、7nm訂單都敗給台積電。

下一代的驍龍875處理器上,三星倒是奪回一城,,訂單價值超過1萬億韓元,約合58億人民幣。

除了高通這個大客戶之外,三星還拿到了NVIDIA的高性能芯片,大家都知道RTX 30系列的GA102核心是三星8nm工藝,不出意外的話,未來的GA104/GA106等主流顯卡核心也是三星的訂單了。

與前兩年相比,三星在高端工藝上已經開始追趕台積電了,盡管目前的差距還很大,不過三星的野心也不可小覷,他們希望在2030年成為全球半導體製造行業的龍頭,要超過台積電。

作者:憲瑞來源:快科技

8000工程師上陣 台積電將新建研發中心 攻堅2nm工藝

在今天開幕的台積電技術論壇上,,還正式宣布建設新的研發中心,預計將有8000多名工程師投入到一條先進工藝生產線上,目的是攻克2nm工藝。

前不久台積電以36.5億新台幣的價格收購了同樣位於南科工業園的力特公司的偏振光廠房,要建設新的生產廠,不過台積電官方沒有明確這個工廠是為2nm研發中心准備的。

由於訂單大增,今年以來台積電已經投入上百億新台幣購買土地以便擴張產能。

目前不論三星還是台積電,半導體工藝已經做到了3nm級別,技術研發基本完成,剩下的就是建廠量產的問題了。

2nm工藝是3nm之後的一次重要迭代,與三星激進地選擇在3nm節點就導入GAA環繞柵極工藝不同,台積電更為保守,在2nm節點才導入GAA工藝,所以2nm節點對他們而言是一次重要的技術升級。

台積電此前提到2nm工藝技術研發順利,,成功找到切入GAA工藝的路徑。

不過目前來看,2nm工藝的研發其實遠沒有結束,台積電也只是剛剛開始,依然需要投入大量資源,這80000多名工程師就是必要條件之一,這也彰顯了台積電未來繼續保持工藝領先優勢的決心。

作者:憲瑞來源:快科技

7納米、14納米、28納米工藝市場價值對比 中芯國際比台積電差在哪里?

2020年8月11日,近日,中芯國際公布了截至2020年6月30日未經審計的第二季度財報。財報中顯示:

2020年第二季的銷售額為938.5百萬美元,相較於2020年第一季的904.9百萬美元增加3.7%,相較於2019年第二季的790.9百萬美元增加18.7%。

2020年第二季毛利為248.6百萬美元,較2020年第一季的233.6百萬美元增加6.4%,較2019年第二季的151.2百萬美元增加64.5%。

2020年第二季毛利率為26.5%,相比2020年第一季為25.8%,2019年第二季為19.1%。

從財報上看,中芯國際整體業績的表現還是很優秀的。

28納米工藝的「黃金線「

隨着半導體製造技術的進步,芯片製程越做越小,性能也在不斷提升。但並非所有芯片設計公司都會選擇最先進的半導體製造工藝。

根據《2019集成電路行業研究報告》中的數據顯示,先進製程(28nm及以下工藝)占據了48%的市場份額,而其它成熟工藝則占據了52%的市場份額。

如果將28nm工藝也視作「成熟工藝」的話,成熟工藝的市場份額就更大了。可以說,成熟工藝才是業界的主流。

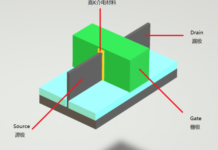

在談28納米工藝之前,先提一下FinFET。FinFET(Fin Field-Effect Transistor)中文名為鰭式場效應晶體管,是一種新的互補式金氧半導體晶體管。

FinFET的命名是根據晶體管的形狀與魚鰭的相似性,中芯國際的14nm工藝就使用了這種結構。

FinFET結構示意圖

FinFET結構的溝道區域是一個被柵極包裹的魚鰭狀半導體。從圖上源極到漏極方向上鰭的長度為溝道長度。

柵極採用了包裹式的結構,這樣增強了柵的控制能力,對溝道提供了更好的電學控制,從而降低了漏電流,抑制短溝道效應。

通俗點說,如果把電流想象成水流,那麼圖上的魚鰭狀半導體就是一根水管,源極和漏極就是水管的進水口和出水口,而中間的柵極則是水管閥門。

對於晶體管來說讓它導通電流比較簡單,如何讓它在關閉的時候還不漏電才是難點。所以FinFET結構就是把溝道區域做薄來抑制漏電,就像是把水管做薄之後,中間的閥門只要輕輕一夾就能把水管完全關閉。

傳統的半導體製造技術很難製造25納米以下的工藝,FinFET結構就是為了解決這個問題而產生的。

通常情況下製造25納米以下的工藝需要FinFET、FD-SOI或者其它更先進的技術。

使用FinFET可以讓芯片的性能變得更好,那麼對於沒有使用FinFET結構的28nm工藝和使用了FinFET的14nm工藝對比,是不是28nm工藝就不太好呢?

這要看評價角度了,評價一種半導體製造工藝的好壞並不能單單看性能、功耗。

數據來自《集成電路設計業的發展思路和政策建議》

根據《集成電路設計業的發展思路和政策建議》中的數據,14nm工藝開發成本遠遠超過28nm工藝。如果從成本角度看,使用了FinFET的14nm工藝在成本方面體現出了明顯的劣勢。

更何況不是所有的芯片都像CPU、GPU那樣需要極高的性能,很多芯片只是能夠實現特定的功能就可以了,由此看來28納米工藝是一款極具「性價比「的工藝。

如果一個芯片項目對於性能有一定要求但不是很高,並且需要控製成本。那麼對於這類芯片來說,28納米工藝目前是一個非常好的「妥協點」。

7納米工藝的「高端圈子「

以台積電7nm工藝為例,台積電的7nm工藝分為第一代7nm工藝(N7)、第二代7nm工藝(N7P)、7nm EUV(N7+)。

其中N7和N7P使用的是DUV光刻,但為了用DUV製作7nm工藝,它還使用了例如沉浸式光刻、多重曝光等技術。

而N7+則直接使用了EUV光刻。所以說這三種7nm工藝雖然在性能、功耗等方面表現優異,但成本都十分高昂。通常像華為、蘋果、AMD這樣的大廠才會使用。

數據來自台積電

可以從數據中看出手機芯片和高性能計算芯片(例如CPU、GPU)一直在台積電收入中占據了過半的比重。

電腦芯片對於性能有着較高的要求,所以電腦芯片設計廠商更傾向於使用「高端」工藝。

而對於手機芯片來說,除了性能,功耗也是十分重要的參數。特別是在當今電池技術發展緩慢的情況下,降低手機芯片的功耗可以大大提高手機的續航能力。

因此手機芯片廠商也十分願意追捧「高端「工藝。

夾縫中的中芯國際14納米工藝

對於中芯國際14nm工藝來說,向上有性能壓制的7nm工藝,向下又有性價比極高的28nm工藝,這種情況對於中芯國際的14nm工藝來說並不太友好。

數據來自中芯國際

在今年第一季度的財報中,中芯國際14nm工藝收入占比僅為1.3%,這種情況並不算太理想。

數據來自中芯國際

而在今年第二季度的財報中,中芯國際乾脆沒有公示14nm工藝的收入占比,僅公示了14/28nm的占比數據。

圖片截取自中芯國際官網

雖說過去確實有人將14nm工藝和28nm工藝都算作先進工藝,但在中芯國際官網上明確的將14nm工藝列為先進邏輯技術,而將28nm工藝列為成熟邏輯技術。

更何況中芯國際之前的財報都是將14nm工藝和28nm工藝占比分開統計,現在卻將一種「先進邏輯技術」和一種「成熟邏輯技術「強行放在一起統計,這種舉動顯然有些奇怪。

不免會讓人認為中芯國際有意隱藏14nm工藝占比數據,或者是讓14nm工藝的占比數據更好看一些。

從目前的數據看,中芯國際14nm工藝的占比在非常緩慢的爬升,而且會在未來相當長的一段時間內依舊保持一種較低的占比,短期內無法成為盈利支柱。

比起14nm,自家的28nm工藝收入占比更高,而且爬升速度更快,這種性價比更高的成熟工藝更容易盈利。

「遲到工藝」的窘境

數據來自各公司公開信息

從表格中可以看出,不少芯片製造廠商集中在2015年推出14nm工藝,業界標杆的台積電也是在2015年推出了水平與業界14nm工藝相似的16nm工藝。在那時候14/16nm工藝是業界頂級工藝,各大芯片設計廠商紛紛追捧。

數據來自台積電

以台積電的數據為例,其16nm工藝的收入占比在以很快的速度下滑,而7nm工藝的占比則在快速提升。由此可見14/16nm工藝的市場火熱程度已大不如前。

在2019年的時候中芯國際才推出14nm工藝,但此時業界頂級工藝已經開始向7nm工藝過渡。

來源:快科技

憑什麼碾壓Intel?台積電成功登頂的三大秘訣

過去十幾年間,台積電的耀眼光芒,讓半導體業界其他企業的進步,都顯得黯然失色。而在疫情肆虐和中美摩擦日益嚴峻的2020,台積電更是捷報頻頻。

2020年第二季度台積電淨利潤暴漲81%,創下六年來最大利潤記錄,同時二季度占全球代工市場份額的51.9%;根據企業追蹤機構CEO Score和韓聯社的分析數據,本周四台積電以總市值3063億美元榮登全球半導體企業榜首,三星其次,然後是NVIDIA和Intel,博通第五;再加上傳來其先進的3nm工藝製程也將於明年下半年量產的消息。正所謂「鯤之大,不知其幾千里也「。

「積土成山,風雨興焉;積水成淵,蛟龍生焉」。台積電能成為今天市值第一,占據代工半壁江山,造就一代半導體王國。這一路走來,台積電以技術取勝,也見證許多競爭對手的起落,其背後是多種因素使然,或因為張忠謀的帶領,或因為敏銳的市場嗅覺,或因為多年高強度的研發投入,或因為對先進封裝製程的追逐,總之,不能一言以蔽之。

不過需要關注的是,在半導體界,選擇和努力同樣重要,台積電前COO蔣尚義在退休時講了一句話:「當初做的一些決定,事前根本不知道是對是錯,很多決定都是因為執行得很好,才變成對的決定。「對於台積電來說,有三個節點的選擇對其如今的地位起了至關重要的作用。

比IBM早一年研究出0.13微米銅製程

台積電於1987年創立,最初的技術來自於飛利浦公司,最開始台積電從量產0.8微米芯片開始發展。原本是台積電仰望飛利浦的技術,但是後來台積電逐漸趕超。

發生如此重大反轉變化的關鍵是,台積電於2000年開始投入研發的0.13微米銅製程技術。而余振華是當年帶領台積電開發0.13微米銅製程的重要人物。

余振華在一次人物專訪中談到,大約1997年,台積電獲悉了IBM發表的銅製程技術,那是台積電第一次聽到銅製程,以前都是用鋁!銅的電阻系數比鋁還要低三倍,當電流流量大時,會產生電遷移 (electromigration)現象,而電阻系數低可以降低電遷移所導致的原子流失。對於半導體技術來說,阻抗低是一項優勢。但是之前銅製程的技術尚未成熟,只能先開發鋁製程。

余振華透露,台積電並不是一開始就決定要自行開發銅製程。當時,IBM 想要把這個技術賣給台積電,而台積電認為IBM技術不成熟,不如自己干。後來余振華帶領一組開發團隊到台南,前後待了一年半。而那時候聯電則向IBM買技術,兩家公司用不同方式競爭銅製程的未來。

當時余振華帶領着一支獨立的研發團隊,與IBM領頭的世界級研發大聯盟競爭,戰況極為激烈。「那時候我們在台南,每天早上開會前第一件事,就是先問對手有沒有消息,有沒有開記者會宣布做出來了。有沒有?有沒有?沒有,好,那開會。晚上開會前再問一次,有沒有?有 沒有?沒有,好,大家晚安。」余振華描述到,可以看出當時與對手競爭的焦灼心情。

銅製程的研發完全要靠自己,沒有借鑒。關鍵是,除了銅,還有Low-K Dielectric(低介電質絕緣),電容與電阻決定了技術。余振華描述銅是骨頭,Low K像肌肉一樣,這兩者都很重要。台積電是直接在生產線上開發,這要求很高,一步都不能錯,於是在無塵室里,其他人都穿白色無塵衣,但負責開發銅製程的人員是穿粉紅色無塵衣!因為當時台積電對銅製程不了解,怕製程中的污染擴散,因此擬定了非常嚴格的開發步驟。連在里面走路的路線都在地板上畫好,不能走偏。

嚴謹的開發過程,很快就讓台積電收獲了成果。當時台積電選了幾個客戶嘗試銅製程,獲得 非常好的成果。於是,余振華的頂頭上司蔣尚義,做了一個很大膽的決定,跳過0.15微米,直接量產0.13微米。

0.13微米是在2000年開始生產,當時遇到網絡泡沫,各家公司業績都直線落,但憑借 0.13 微米台積電不但支撐住了業績,還大幅提升了市占率。經此一役,台積電的技術,尤其是銅製程相關的技術,從此被肯定為第一流,遠遠的把其他公司甩在後頭。

台積電的銅製程已經走向市場,而IBM的技術卻仍未走出實驗室。十年後,IBM又倒貼15億美元,將代工業務轉給了格芯,徹底退出了代工領域。

銅製程是奠定台積電霸主地位的關鍵技術。那麼,在銅製程之後呢?

張忠謀回歸,押寶28nm大殺四方

2009年,金融危機的余韻還在繼續,台積電正處於內憂外患之際:內部,蔡力行實行了嚴酷的裁員潮,而且公司新產線良率也遲遲得不到改善,客戶甚至取消訂單;外部三星開始進軍芯片代工,並且來勢洶洶。於是已經78高齡退休的張忠謀重新回爐。

張忠謀看到了未來智能手機市場需求的潛力,他立即將2010年的資本支出增加了一倍,達到59億美元,主要集中在28nm製程上,這是當時最先進的晶圓製程。盡管大膽的投資策略震驚了業界,但也為台積電接下來幾年的快速增長奠定了基礎。

當時臨危受命的蔣尚義投入28nm製程的研發中,更為重要的是蔣尚義選擇了後閘級方案,而非三星正在研發的前閘級。這又是一次類似於0.13微米戰役的巨大獲勝,正確的判斷、嚴格的工藝,台積電良率大幅提升。終於,在2011年10月24日, 台積電宣布,其28nm工藝的量產和生產晶圓已經發貨給客戶。台積電領導晶圓代工部門實現28nm節點的批量生產。

28nm工藝節點的突破對台積電和業界來說都是一個巨大的節點!對台積電來說,28nm節點不但貢獻了巨大的營收,還鞏固了市場地位。當年一起競爭的28nm製程格羅方德、聯電等大廠,無不紛紛敗下陣來,無論是在資金和技術上都難以追趕,還相繼宣布退出先進製程競賽。

在2011年量產的當年28nm節點就貢獻了1.5億美元(約43億新台幣)的營收。2013年增長至60億美元(約1765億元新台幣)。到2014年,台積電營收突破7500億元新台幣,比2013年增加了28%,28nm營收占比超過3成,台積電在晶圓代工市場的市占率也從2009年的45%提高到了52%以上。台積電 2016 年28nm占據 60%以上的市場,且收入占比維持25%左右。

台積電自2013年很長一段時間以來,28nm工藝一直占據其收入的 20%以上比重,是前二大收入來源,且大部分時間是第一大製程業務。

台積電28nm節點占營收的百分比(圖源:西南證券)

另一方面,台積電的客戶也得以採用最先進的技術來滿足市場需求。五個台積電28nm客戶分別是Xilinx,Altera,NVIDIA,AMD和高通。

28nm滿足了Altera FPGA新技術,AMD的圖形IP借用台積電的28nm技術實現了圖形性能的下一個重大飛躍,NVIDIA提供出市場上最節能的GPU和最高性能的圖形處理器,高通在28nm節點上推出了第一個集成的智能手機處理器Snapdragon S4類處理器。

在行動裝置、高效能運算、汽車電子及物聯網四個快速成長的主要市場,台積電分別建立了四個不同的技術平台,而在這四個技術平台中都有28nm的身影,可以看出 28納米的地位之顯赫。

台積電的四大技術平台中都有28nm的身影(圖源:西南證券)

然而,此時的台積電將目光放在了更遠的大洋之外,那里有能支撐任何一個代工廠走向世界頂峰的超級客戶:蘋果。

進軍封裝領域,獨霸蘋果訂單

早年,蘋果iPhone處理器一直是三星的禁臠。但台積卻能從A11開始,接連獨拿兩代iPhone處理器訂單,讓業績與股價持續翻紅。關鍵就是台積電的全新封裝技術InFo,它減少手機30%的厚度,騰出寶貴的手機空間給電池或其他零件。

時間回到2011年的台積電第三季法說會上。當時,張忠謀毫無預兆的擲出一個震撼彈─台積電要進軍封裝領域。這一個炸彈一經擲出,硝煙一直彌漫到現在。從價格偏貴導致鮮有人問津的CoWoS開始,到首度用在iPhone 7與7Plus的InFO封裝技術。正是最不被人看好的整合連結與封裝部門,為台積電贏家通吃奠定了堅實的基礎。

要知道,晶圓廠向封裝領域進軍,這在業界看來,台積電根本不可能成功!

首先,在成本面上就難與傳統封測廠競爭,因為封裝廠也在不斷發展新技術,而台積電的人力成本遠高過封裝業,因此要求產品毛利要達到50%,但日月光、矽品只要20%就能做了。

另外,外資分析師也看衰,美商伯恩斯坦證券分析師Mark Li當時的研究報告寫着:「InFo會讓台積相對於Intel與三星更有競爭力嗎?不,我們不認為。」

為何會這麼認為呢?當時三星和Intel的扇出型晶圓級封裝的專利數分別名列全球第二、三,而剛入門的台積電連前十的門檻都沒摸到。這樣看來,業界看衰似乎都是合理的。

在默默無聞的那些年,我們不知道台積電經歷了什麼,有的說台積付出了昂貴的學費,5年間產線燒壞了幾千片昂貴的晶圓,也有的說良率一直上不去,眾說紛紜,具體實況我們不去考究了,畢竟其結果是美的。

2016年,CoWoS的新客戶開始如雨後春筍般出。NVIDIA推出了該公司第一款採用CoWoS封裝的繪圖芯片GP100;Google的AI芯片TPU 2.0,就是AlphaGo打敗世界棋王柯潔背後的那款新品;Intel與Facebook合作推出的Nervana類神經網路處理器。這些巨頭的AI芯片都採用台積電CoWoS封裝製造。

2018年台積電已完成搭載7nm邏輯IC及第二代高頻寬記憶體(HBM 2)的 CoWoS 封裝量產,並藉由高製造良率、更大硅中介層與封裝尺寸能力的增強、以及功能豐富的矽中介層,例如內含嵌入式電容器的矽中介層,使得台積電在...

外媒 三星跳過4nm工藝 是為在芯片技術競爭中擊敗台積電

7月3日消息,據國外媒體報道,昨日出現了三星修改芯片工藝路線圖,跳過4nm工藝,由5nm直接提升到3nm的消息。

在隨後的報道中,外媒稱三星此舉,意在獲得競爭優勢,在技術競爭中擊敗目前在芯片工藝方面走在行業前列的台積電。

台積電近幾年在芯片工藝方面走在行業前列,他們的7nm和5nm工藝都是率先量產,也獲得了大量的芯片代工訂單,從2016年起,更是連續為蘋果獨家代工A系列處理器。

三星曾經也是蘋果A系列處理器的代工商,但在2015年為蘋果代工iPhone 6s系列的A9處理器時,三星14nm工藝所生產的處理器,在能耗方面還高於台積電16nm工藝所生產的A9處理器,三星此後就一直未能獲得蘋果A系列處理器的代工訂單,在芯片工藝方面也一直略落後於台積電,台積電也憑着先進的工藝獲得了大量的芯片代工訂單。

不過,三星通過跳過4nm工藝、直接由5nm提升到3nm的方式,能否在芯片工藝方面擊敗台積電現在還很難說,台積電也有研發3nm工藝,在多年前就已開始謀劃。

台積電的3nm工藝,在公司創始人張忠謀退休前就已開始謀劃,在他退休前8個月的一次采訪中,就談到3nm工廠,當時他透露採用3nm工藝的芯片製造工廠計劃在2022年建成,保守估計建成時可能會花費150億美元,最終可能會達到200億美元。

在今年4月16日的一季度財報分析師電話會議上,台積電副董事長兼CEO魏哲家也曾談到3nm工藝,他表示3nm工藝的研發正在按計劃推進,計劃2021年風險試產,他們的目標是在2022年下半年大規模量產。

折扣商品信息>>

來源:快科技

摩爾定律延壽數十年 FinFET晶體管發明人胡正明獲IEEE榮譽獎章

日前IEEE電子電器工程師協會宣布,FinFET晶體管發明人胡正明(Chenming Hu)獲得了2020年的IEEE 榮譽獎章,這是IEEE協會的最高獎勵,這一技術使得摩爾定律延壽了數十年。

自從1965年,Intel聯合創始人戈登·摩爾提出「摩爾定律」以來,半導體工藝一直按照這個規律發展,2年提升一倍的晶體管密度。

不過摩爾定律原本應該終結了,因為按照之類的發展,傳統硅基半導體工藝製造難度越來越大,特別是在28nm工藝之後。

胡正明教授在這個問題上貢獻很大,他於1999年發明了FinFET晶體管,也叫鰭式晶體管或者3D晶體管,就是因為晶體管的形狀與魚鰭的相似性。

FinFET晶體管的設計可以改善電路控制並減少漏電流,縮短晶體管的閘長,FinFET閘長已可小於25nm,未來預期可以進一步縮小至9nm,約是人類頭發寬度的1萬分之1。

Intel在2012年正式量產了3D晶體管技術,首發的是22nm工藝,當時台積電、三星還停留在28nm工藝上,之後在16/14nm節點上他們才進入了FinFET晶體管時代。

從這一點上來說,胡正明教授發明的FinFET技術不僅拯救了摩爾定律,Intel、AMD、NVIDIA、蘋果、華為、高通、三星等半導體行業的公司都受益於胡正明教授的發明。

作者:憲瑞來源:快科技

分形工藝推出Define 7和Define 7 XL:更新機箱典範

分形工藝於昨日宣布推出新的Define 7系列機箱,一共有兩款,分別是中型的Define 7和大型的Define 7 XL。

新的Define 7系列在設計思路上面仍然秉承了Define系列一貫的靜音、模組化路線。

Define 7

系列引入了新的開放式雙布局內部結構,可以做到容納E-ATX主板,或是可以做到容納14個3.5寸HDD、4個2.5寸SSD/HDD外加1個5.25寸ODD,頂部更是可以放入420mm的冷排。同時其模塊化結構允許用戶自行定製機箱內部結構,新型通用支架具多功能性,任何閒置風扇位皆可改變為HDD、SSD、液冷泵或水箱的固定架。機箱可以做到三面全開,方便安裝及布線。

三面可拆,新型前面板經過改良設計,具有可逆鉸鏈並帶有磁性閂鎖

Define 7內部空間

硬碟架經過重新設計,現在有4個堅固支點。

內部共有9個120/140風扇位。

Define 7 XL

Define 7 XL的主要區別點在於它大了一號,從而可以提供更多硬碟位,最多可裝入18個3.5寸盤和5個2.5寸盤。

另外它的內部空間可以容納更大的SSI-EEB主板,或是285mm的E-ATX主板。

內部則是可以有9個140mm或11個120mm風扇位。

兩款機箱都自帶三枚140mm風扇,並且帶有風扇集線器,提供多種側板供選擇,可側透可靜音。USB接口配置是2xUSB 3.0+2xUSB 2.0+1x USB 3.1 Type-C。

售價方面,Define 7起售價為¥1199,Define 7 XL為¥1549。

目前媒體已經有針對這款機箱的評測了,這邊提供幾個連結,有興趣的朋友可以去看看:

Tom's Hardware: Fractal Design Define...

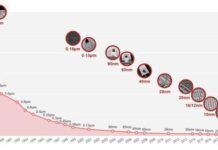

從3微米到5納米 一圖看台積電成立33年來的工藝演進

1月21日消息,據國外媒體報道,為蘋果、華為等公司代工芯片的台積電,近幾年在芯片工藝方面走在行業的前列,已連續4年獨享蘋果的A系列芯片大單,今年預計還會繼續。

台積電能夠連續4年獨享蘋果的大單,靠的是業界領先的工藝,而台積電也在官網,披露了他們自成立以來的工藝演進。

台積電芯片工藝演進圖

從台積電官網所公布的信息來看,在1987年成立時,他們的芯片工藝是3微米,隨後逐步提升,在1990年提升到了1微米;2001年的時候提升到了0.13微米,也就是130納米;2004年開始採用90納米工藝;隨後是65納米、45納米、40納米、28納米、20納米,2015年提升到了16納米;2016年升至10納米;2017年是7nm;5nm也已在去年風險生產,將在今年上半年開始大規模量產。

除了圖中列出來的工藝,台積電也在研發更先進的3nm工藝,在四季度的財報分析師電話會議上,台積電CEO魏哲家透露在4月29日舉行的台積電北美技術研討會期間,將披露更多3nm工藝的細節信息。

來源:快科技

價值200億美元 台積電4月份揭秘3nm工藝 與三星關鍵決戰開始

在上周的說法會上,台積電宣布2020年的資本開支是150到160億美元,其中80%將投向先進產能擴增,包括7nm、5nm及3nm。這次說法會上台積電沒有公布3nm工藝的情況,因為他們4月份會有專門的發布會,會公開3nm工藝的詳情。

台積電的3nm工藝技術最終選擇什麼路線,對半導體行業來說很重要,因為目前能夠深入到3nm節點的就剩下台積電和三星了,其中三星去年就搶先宣布了3nm工藝,明確會放棄FinFET晶體管,轉向GAA環繞柵極晶體管技術。

具體來說,三星的3nm工藝分為3GAE、3GAP,後者的性能更好,不過首發的是第一代GAA晶體管工藝3GAE。根據官方說法,基於全新的GAA晶體管結構,三星通過使用納米片設備製造出了MBCFET(Multi-Bridge-Channel FET,多橋-通道場效應管),該技術可以顯著增強晶體管性能,主要取代FinFET晶體管技術。

此外,MBCFET技術還能兼容現有的FinFET製造工藝的技術及設備,從而加速工藝開發及生產。

在2019年的日本SFF會議上,三星還公布了3nm工藝的具體指標,與現在的7nm工藝相比,3nm工藝可將核心面積減少45%,功耗降低50%,性能提升35%。

三星計劃在2030年前投資1160億美元打造半導體王國,由於在7nm、5nm節點上都要落後於台積電,所以三星押注3nm節點,希望在這個節點上超越台積電成為第一大晶圓代工廠,因此三星對3GAE工藝寄予厚望,最快會在2021年就要量產。

至於台積電,在3nm節點他們也大舉投資,去年宣布斥資195億美元建設3nm工廠,2020年會正式開工,不過技術細節一直沒有透露,尤其是台積電是否會像是三星那樣選擇GAA晶體管或是會繼續改進FinFET晶體管,這兩種技術路線會影響未來很多高端芯片的選擇。

作者:憲瑞來源:快科技

Intel 2029年上1.4nm工藝?非官方路線圖

Intel的製程工藝一直備受關注。今天早些時候,荷蘭光刻機巨頭ASML(阿斯麥)放出一張路線圖,赫然羅列了Intel 7nm、5nm、3nm、2nm、1.4nm等工藝節點,尤其是最後這個將在2029年上馬的1.4nm非常意外,是我們第一次看到非整數工藝節點。

就此消息,快科技收到了Intel官方的澄清聲明。

原來,這張路線圖並非完全來自Intel官方,而是ASML CEO Martin van den Brink拿了此前Intel 9月份公布的一張製程工藝更新PPT修改而來,自行添加了原來沒有的幾個工藝名稱,但並未說明,造成了誤會。

這才是Intel的原圖:

換句話說,Intel對於7nm、5nm、3nm等等這些新工藝肯定是在研究推進的,原始PPT也明確2021年開始,會每兩年對製程工藝進行一次重大升級,而且每代工藝都有+、++兩次優化更新。

但是更具體的新工藝技術節點和對應時間表,Intel尚未公布,1.4nm這樣的另類更是完全無從談起。

當然在另一方面,ASML作為光刻機巨頭,可以說是Intel工藝進步的源頭之一,雙方合作關系密切,肯定了解一些Intel的規劃,但未來究竟如何發展,還是要等Intel官方公布的消息了。

Intel還向我們強調,在摩爾定律精神的指引下,Intel推進創新的決心始終堅定!

文章糾錯

作者:上方文Q來源:快科技

進軍2nm工藝 中科院研發世界首個自對准柵極的疊層垂直納米環柵晶體管

目前全球最先進的半導體工藝已經進入7nm,下一步還要進入5nm、3nm節點,製造難度越來越大,其中晶體管結構的限制至關重要,未來的工藝需要新型晶體管。來自中科院的消息稱,中國科學家研發了一種新型垂直納米環柵晶體管,它被視為2nm及以下工藝的主要技術候選,意義重大。

從Intel首發22nm FinFET工藝之後,全球主要的半導體廠商在22/16/14nm節點開始啟用FinFET鰭式晶體管,一直用到現在的7nm,未來5nm、4nm等節點也會使用FinFET晶體管,但3nm及之後的節點就要變了,三星在去年率先宣布3nm節點改用GAA環繞柵極晶體管。

根據官方所說,基於全新的GAA晶體管結構,三星通過使用納米片設備製造出了MBCFET(Multi-Bridge-Channel FET,多橋-通道場效應管),該技術可以顯著增強晶體管性能,主要取代FinFET晶體管技術。

此外,MBCFET技術還能兼容現有的FinFET製造工藝的技術及設備,從而加速工藝開發及生產。

前不久三星還公布了3nm工藝的具體指標,與現在的7nm工藝相比,3nm工藝可將核心面積減少45%,功耗降低50%,性能提升35%。

從上面的信息也可以看出GAA環繞柵極晶體管的重要意義,而中科院微電子所先導中心朱慧瓏研究員及其課題組日前突破的也是這一領域,官方表示他們從2016年起針對相關基礎器件和關鍵工藝開展了系統研究,提出並實現了世界上首個具有自對准柵極的疊層垂直納米環柵晶體管(Vertical Sandwich Gate-All-Around FETs或VSAFETs),獲得多項中、美發明專利授權。

這一研究成果近日發表在國際微電子器件領域的頂級期刊《IEEE Electron Device Letters》上(DOI: 10.1109/LED.2019.2954537)。

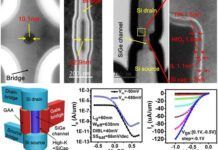

左上:STEM頂視圖,用原子層選擇性刻蝕鍺硅的方法製作的直徑為10納米的納米線(左)和厚度為23納米的納米片(右)

右上:具有自對准高k金屬柵的疊層垂直納米環柵晶體管(VSAFETs)的TEM 截面圖(左)及HKMG局部放大圖(右)

下: pVSAFETs器件的結構和I-V特性:器件結構示意圖(左),轉移特性曲線(中)和輸出特性曲線(右)

據介紹,朱慧瓏課題組系統地研發了一種原子層選擇性刻蝕鍺硅的方法,結合多層外延生長技術將此方法用於鍺硅/硅超晶格疊層的選擇性刻蝕,從而精確地控制納米晶體管溝道尺寸和有效柵長;首次研發出了垂直納米環柵晶體管的自對准高k金屬柵後柵工藝;其集成工藝與主流先進CMOS製程兼容。課題組最終製造出了柵長60納米,納米片厚度20納米的p型VSAFET。原型器件的SS、DIBL和電流開關比(Ion/Ioff)分別為86mV/dec、40mV和1.8x105。

文章糾錯

作者:憲瑞來源:快科技

向1nm技術節點進軍

IMEC於10月11日在東京舉辦了年度研究結果介紹會「 IMEC Technology ForumJapan 2019(ITF Japan 2019)「。

原先負責並領導IMEC的半導體微縮化工藝/器件部門的安·斯蒂根(An Steegen)於2018年秋季突然退休,留下重要職位空缺。會議當天,新到任的Myung-Hee Na博士作了題為「通往CMOS微型化極限的道路」的演講,並介紹了更新至1nm節點的IMEC半導體技術路線圖。在2001年加入IBM之後,她從事尖端半導體工藝和器件的研發工作已有18年,並於2019年加入IMEC。前任Steegen也來自IBM,因此Myung-Hee算是其後輩。

改進晶體管的結構和材料以延續摩爾定律

讓我們看一下IMEC發布的半導體技術路線圖。橫軸表示時間,縱軸表示每單價的晶體管數(晶體管數/美元)。隨着微型化和集成化的發展,由於工藝復雜性,製造成本正在迅速上升,因此,無法按摩爾定律降低單位晶體管的製造成本。

邁向1nm節點的技術路線圖(來源:IMEC)

長期以來,摩爾定律已經失效,但IMEC並沒有放棄,持續改進晶體管結構和材料,並且對工藝進行優化以呈現1nm節點的技術路線圖。

從28nm技術節點採用HKMG(High-K/ Metal Gate),並在16 / 14nm之後從傳統的平面結構轉向FinFET結構。從7 /5nm開始,開始採用Co作為MOL布線材料以及EUV光刻,以進一步改進FinFET結構。

從4/3nm節點開始,FinFET將被GAA結構取代,第一代GAA將採用硅納米片。獨創的埋入式電源線(將Vcc和地線埋入前層以壓縮標準單元面積)將採用Ru作為布線材料。

半導體器件結構路線圖(來源:IMEC)

2nm採用Forksheet,1nm採用CFET

對於高性能和低功耗應用,IMEC計劃採用FinFET的改進版本。換句話說,2nm技術節點將採用Forksheet結構,其中n型和p型納米片緊密地靠在一起,並且其間有一層「絕緣牆「。之所以命名為forksheet,是因為其截面類似於餐叉。與此同時,在芯片背面提供配電網絡(PDN)從而向BPR提供有效的電能供應。

當達到1nm節點時,IMEC會採用CMOS結構的Complementary FET(CFET)。在此,通過在p型FET上堆疊n型FET,即通過三維堆疊具有不同導電類型的晶體管,從而標準單元面積被大大減小。據說芯片的背面可以提供更多功能,但未公開細節。從這里開始,將採用high-NA EUV光刻以進一步微縮晶體管結構。

IMEC還希望採用二維材料,自旋電子學和量子計算。為了將來進一步微縮,除了設計和工藝協同優化(DTCO)之外,系統和工藝協同優化(STCO)也很重要。

最終的二維CMOS結構「Forksheet FET」(來源:IMEC)

到目前為止,SRAM必須在每個存儲單元的平面上構建6個晶體管。IMEC表示,通過改進晶體管結構和電源線,即通過採用GAA和BPR,頂視圖中SRAM晶體管的等效數量可以減少到每個存儲單元4.4個晶體管,即SRAM單元面積大約減小到原來的2/3。

延續摩爾定律的另一種技術是3D封裝。在2019年5月於比利時舉行的IMEC技術論壇2019上對此進行了詳細介紹。從芯片堆疊開始的3D封裝最終將出現在晶體管本身的3D堆疊中。IMEC正在同時研究垂直堆疊以及橫向微縮,並正在嘗試提高系統集成度。為此,IMEC同時專注於優化工藝技術,設計技術和系統技術。

查看原文

文章糾錯

來源:快科技

13000日元皮卡丘人偶公布 日本傳統工藝打造萌神

<p創立於大正8年(1919年)的真多呂人形今日公佈了一款江戶貼花皮卡丘人偶。

<p採用了用日本傳統工藝的皮卡丘人偶經過製作者多次嘗試,還原出了皮神圓圓萌萌的神態和造型,展現了現代寶可夢和傳統技藝的完美融合。

這款皮卡丘人偶為限量發售,尺寸150(W)×120(D)×157(H)mm,含稅售價13200日元,合人民幣約849元。

本文由遊民星空製作發佈,未經允許禁止轉載。

來源:遊民星空

英特爾14nm為何用到2021年?10nm太難,沒量產就虧了5.3億美元

去年英特爾發布了九代酷睿處理器,首先的主要是K系列,升級到了8核16線程,加速頻率可達5GHz,隨着前不久推出九代酷睿移動版及25款桌面版,九代酷睿家族基本上補全了。九代酷睿發布之後,英特爾台式機總經理克里斯·席爾瓦曾經表態九代酷睿將是14nm工藝的謝幕演出,意味着以後不再發14nm處理器了。不過英特爾的承諾顯然不會做到,最新的路線圖顯示直到2021年英特爾還會再推14nm工藝的處理器。為何英特爾如此依賴14nm處理器,不是說10nm工藝今年底就量產嗎?英特爾今年或許可以推出10nm處理器,但10nm的問題顯然沒有徹底解決,這還沒量產呢,Q1季度就因為10nm產能爬坡虧了5.3億美元了,嚴重拖了後腿。

英特爾上周發布了Q1季度財報,雖然官方表示Q1季度營收好於預期,但是對Q2季度及全年的展望更加保守,預期今年營收只有690億美元,比年初預計的減少了25億美元,這個利空消息一出,英特爾股價三天來已經跌了將近10%,市值損失了240億美元了。

拖累英特爾業績的因素很多,Q1季度中DCG業務營收及盈利全面下滑,PC業務倒是增長了,但是NAND閃存等業務因為大幅降價而損失慘重。在官方解釋中,10nm工藝及NAND閃存跌價是導致Q1季度盈利下滑的主要原因,此前英特爾財報數據顯示Q1季度NAND閃存降價導致虧損了3億美元,比一年前的8100萬美元虧損大幅增加,為此英特爾也要削減NAND產能。

那麼10nm工藝又給英特爾帶來多大的麻煩呢?財報數據中沒提,不過在英特爾提交的10-Q文件中提到了10nm產能爬坡帶來的虧損總計有5.3億美元,其中CCG客戶端計算部門損失2.75億美元,DCG數據中心部門損失了2.35億美元。

這兩大部門因為10nm產能爬坡損失了5.1億美元左右,還剩2000萬美元沒提,不過英特爾的10nm工藝不只用在X86處理器上,還有用於5G的Snow

Ridge、用於FPGA的Agilex,這兩部分雖然產能少很多,但影響也是存在的,剩下的2000萬美元虧損應該是出自這些部門了。

結合近期曝光的英特爾處理器路線圖,以及GPU部門可能尋找三星7nm或者5nm工藝代工的消息來看,英特爾的10nm工藝問題比想象中還要復雜——盡管2018年的幾次財報中英特爾一直在強調10nm工藝的良率問題已經解決了,將會如期在2019年量產。

但是最近爆出的種種新聞來看,英特爾的10nm工藝問題不是這麼容易解決的,初期發布的10nm芯片也主要是低功耗版,高性能處理器依然要依賴14nm工藝。

來源:超能網

NVIDIA為何不推7nm顯卡?黃仁勛:我要賺錢,不要額外成本

今天有多個報導為台積電7nm訂單及AMD

7nm處理器、顯卡叫好,認為7nm工藝今年大爆發,高通、聯發科、AMD訂單都會增加,AMD下半年的營收也會因為7nm

CPU及GPU而大幅增長。看好7nm工藝的公司有很多,但對7nm工藝保持冷靜的公司也不是沒有,NVIDIA就對7nm GPU並不熱心,今年GTC

2019大會上也沒公開7nm GPU。對於7nm工藝,黃仁勛的態度很明確:我們想要賺取利潤,而不是支付額外的成本,就價格而言,7nm工藝現在是效率低下的。

GTC大會上不發7nm GPU,今年內NVIDIA再推7nm工藝的新一代GPU可能性就不大了,目前RTX 20系列顯卡已經出到了RTX

2060,主流市場還有GTX 16XX一系列,型號繁多,這些顯卡依然是12nm工藝的,預計今年內都是12nm圖靈顯卡的主場,2020年能看到NVIDIA的7nm

GPU就不錯了。

韓國朝鮮日報報導稱,NVIDIA也可以購買7nm工藝,但現在依然以更高效的12nm圖靈顯卡為主。NVIDIA

CEO黃仁勛表示「我們想要賺取利潤,而不是支付額外的成本。」,黃仁勛提到7nm工藝的昂貴成本已經證實,現在沒有必要(推7nm芯片),「就價格而言,7nm工藝效率低下。」

結合黃仁勛此前在媒體采訪中對7nm工藝的表態,他對依賴特定工藝的做法並不認同,「7nm工藝是公開銷售的,台積電也樂意賣給我們,但是一個公司如果只是依賴購買別家的晶圓,那它的天才是什麼?你自己對晶圓又有什麼貢獻?」

雖然使用了(面積)更大的架構,但是黃仁勛表示NVIDIA超人的工程使得圖靈超過了競品,「(圖靈顯卡的)能效如此優秀,以致於比其他人的7nm顯卡還要好,成本更低、能耗更低、性能更好,而且功能更多。」

簡單來說,NVIDIA對待7nm工藝的態度就是現在的成本還是太高,而他們的12nm圖靈顯卡在性能、能效及功能等方面還是占優的,沒必要急着推7nm芯片,利用成熟工藝成本更低,更容易賺錢。

來源:超能網

台積電放緩今年增長目標,但工藝不停歇:Q2試產5nm EUV

台積電上週發佈了2018年Q4季度財報,當季營收2897.7億新台幣(約合94億美元),同比增長4.4%,環比增長11.3%,其中7nm工藝貢獻了23%的營收,成為營收增長的主動力。2018年台積電的營收基本達到了之前的預期,但是2019年由於半導體行業放緩,再加上智能手機市場需求不振,台積電已經放緩了今年的營收預期,不過他們對先進工藝的投資並沒有停止,今年除了量產7nm

EUV工藝之外,Q2季度要試產5nm EUV工藝,明年上半年則會正式量產5nm EUV工藝。

對於今年Q1季度,台積電的營收指引約為73-74億美元,同比下降了14%,環比下降了22%,這主要是因為產能利用率下降,特別是7nm先進工藝預期會有雙位數的降幅,很大一個原因就是今年的智能手機市場需求依然低迷,7nm主力客戶蘋果的iPhone賣不動,供應鏈已經多次傳來砍單的消息。

台積電也下調了今年的資本支出到100-110億之間,比原定目標減少了10億美元左右,以應對今年的市場變化。

今年的投資重點依然是先進工藝,包括7nm及未來的5nm、3nm工藝,從台積電的法人說明會上的消息來看,今年除了會量產7nm

EUV工藝之外,Q2季度還會試產5nm EUV工藝,預計2020年上半年正式量產,這個進度也沒有受到投資削減的影響。

此外,台積電已經透露有客戶願意升級到5nm EUV工藝,不過他們並沒有提及具體是誰,也沒有透露是哪個行業的。考慮到5nm

EUV工藝在芯片研發、製造上的巨額成本,顯然這會是一家大公司,只是目前沒有哪家公司公開過5nm工藝路線圖,AMD現有的產品線也公開了Zen 3處理器及Nex

Gen顯卡芯片的,不過他們使用的是7nm EUV工藝,而且是2020年才能上市。

來源:超能網

PSP《最終幻想 DFF》工藝品效果能力翻譯

能力名稱

能力詳細

交換次數

コスモスサド裝備可能

全調和方均可裝備

1~31

カオスサイド裝備可能

全渾沌方均可裝備

1~31

全員が裝備可能

全人物均可裝備

32~49

よく落ちる

對戰時掉落率變為25%

1~49

魔法の壁

破損の魔壁(1/3)

2個同時使用魔法防禦提升。

同時裝備3樣將會有反效果。

8~49

魔法の鉄壁

破損の魔壁(1/3)

魔法傷害防禦+10%、追撃傷害防禦+20%激突BRV傷害防禦+20%、激突HP傷害防禦+20%。

同時裝備3樣將會有反效果。

50~

物理の壁

崩落の壁(1/3)

2個同時使用物理防禦提升。

同時裝備3樣將會有反效果。

8~49

物理の鉄壁

崩落の壁(1/3)

物理傷害防禦+10%、追撃傷害防禦+20%、激突BRV傷害防禦+20%、激突HP傷害防禦+20%

同時裝備3樣將會有反效果。

50~

物理の力

オーバーワ(1/3)

2個同時使用物理傷害約有5%提升。

同時裝備3樣將會有反效果。

1~49

物理の極意

オーバーワ(1/3)

物理傷害+10%、追撃傷害+20%、激突BRV傷害+20%、激突HP傷害+20%。

同時裝備3樣將會有反效果。

50~

魔法の力

オーバーヒ(1/3)

2個同時使用魔法傷害約有5%提升。

同時裝備3樣將會有反效果。

1~49

魔法の極意

オーバーヒ(1/3)

魔法傷害+10%、追撃傷害+20%、激突BRV傷害+20%、激突HP傷害+20%。

同時裝備3樣將會有反效果。

50~

攻防一體

攻防の破綻(1/3)

物理傷害、物理傷害防禦、魔法傷害、魔法傷害防禦

各+5%。

同時裝備3樣將會有反效果。

8~49

攻防の秘伝

攻防の破綻(1/3)

物理傷害、物理傷害防禦、魔法傷害、魔法傷害防禦

各+10%。

同時裝備3樣將會有反效果。

50~

地の利

地の暴落(1/3)

地圖陷阱傷害防禦+10%。地圖破壊勇氣值+5%。召喚後EX光點吸収。

同時裝備3樣將會有反效果。

32~49

地の暴利

地の暴落(1/3)

地圖陷阱傷害防禦+20%。地圖破壊勇氣值+10%。召喚後EX光點吸収。

同時裝備3樣將會有反效果。

50~

EX王者

EX敗者(1/3)

EX核心吸収量+10%、EX持續時間+10%、EX核心出現頻度增加、LUK+1。

同時裝備3樣將會有反效果。

32~49

EX覇者

EX敗者(1/3)

EX核心吸収量+20%、EX持續時間+20%、EX核心出現頻度增加、LUK+2。

同時裝備3樣將會有反效果。

50~

EX亡者

EX破産者(1/3)

EX光點吸収量+10%、EX光點吸収距離+1m、攻撃中EX光點吸収、傷害中EX光點吸収

同時裝備3樣將會有反效果。

32~49

EX求道者

EX破産者(1/3)

EX光點吸収量+20%、EX光點吸収距離+2m、攻撃中EX光點吸収、傷害中EX光點吸収

同時裝備3樣將會有反效果。

50~

BRVアタッー

BRVルーザ(1/3)

開場BRV+10%、破壞地圖障礙物BRVUP+5%、進行M軌道移動BRVUP+1%。基本勇氣值恢復速度+12%。同時裝備3樣將會有反效果。

32~49

BRVマスター BRVルーザ(1/3)

開場BRV+20%、破壞地圖障礙物BRVUPP+10%、進行M軌道移動BRVUP+2%。基本勇氣值恢復速度+25%。同時裝備3樣將會有反效果。

50~

韋駄天(1/4)

裝備4樣才能發揮效果。移動速度+8%、跳躍力+10%、跳躍次數+1、空中迴避性能提升。

8~49

アーティファト変化+100%

通信對戰後所取得的裝備將100%產生變化。

8~49

裝備アクセサの壊れやすさ-20%

裝備損壞機率-20%

8~49

アイテムドロプ率+1%

裝備掉落率上升1%

8~49

経験値+10%

經驗值+10%

32~49

PP+100%

PP+100%

32~49

AP+100%

AP+100%

32~49

ちょっと高く売れる

賣出價格+1000 GIL

1~7

けっこう高く売れる

賣出價格+3000 GIL

8~31

すごく高く売れる

賣出價格+10000 GIL

32~49

來源:遊民星空