Tag: 工藝

《藥劑工藝:鍊金術士模擬器》煉藥節省時間方法介紹

《藥劑工藝:鍊金術士模擬器》中煉藥對時間的要求是很高的,很多時候煉藥的時間都是不夠的,很多玩家都不太清楚煉藥節省時間的方法是什麼,其實煉藥想要節省時間只需要把一些半成品保存成配方就行了,更多如下。

煉藥節省時間方法介紹

煉藥想要節省時間可以把半成品保存成配方,也就是說如果有幾種藥在一個方向能節省一些走公共路的時間,或者當你在嘗試三級藥的最佳路線時用這種方式給自己留個檔。

點擊進入:第一次煉藥推薦

來源:3DMGAME

《藥劑工藝:鍊金術士模擬器》第一次煉藥推薦

《藥劑工藝:鍊金術士模擬器》中第一次煉藥能夠煉的藥是可以選擇的,但是很多玩家都不太清楚遊戲中第一次煉什麼藥比較好,其實第一次煉藥最好的選擇就是煉三級藥,然後存成配方,能賺的錢非常多,更多如下。

第一次煉藥推薦

第一次煉藥最好還是選擇煉成三級藥,然後存成配方,這樣可以一勞永逸,賣的價錢高多了,就是要仔細看是有輔助線的,就是有點累眼睛。

點擊進入:商人打折注意事項分享

來源:3DMGAME

《藥劑工藝:鍊金術士模擬器》商人打折注意事項分享

《藥劑工藝:鍊金術士模擬器》中的商人在某些時候是會對自己的商品進行打折的,只需要注意一些事情就可以賺很多錢,但是很多玩家都不太清楚商人打折需要注意什麼,其實對於商人的降價商品只需要買就行了,根本不會虧,更多如下。

商人打折注意事項分享

商人對於自己的商品進行打折降價的時候只需要無腦買就行了,怎麼樣都不會虧,具體大概是半價,另外配方紙也會打折的

點擊進入:遊戲特色內容介紹

來源:3DMGAME

EPI 首個 CPU 原型 EPAC1.0 已經到來 :RISC-V 架構和 22nm 工藝

在處理器方面,不僅中國和美國需要自主研發,歐洲也不願意受制於人。法國等 10 個國家聯合發起了歐洲處理器計劃 (EPI), 自行開發高性能處理器 。EPI 的第一個 CPU 原型 EPAC1.0 已經到來,採用 RISC-V 架構和 22nm 工藝。

歐洲 EPI 處理器計劃已經進行了好幾年,其中一個就是為歐盟的 HPC 超級計算機開發自己的處理器,但進展緩慢,原型 EPAC1.0 直到現在才出現。

EPAC1.0 處理器採用混合架構 ,CPU 內核是...

《藥劑工藝:鍊金術士模擬器》遊戲特色內容介紹

《藥劑工藝:鍊金術士模擬器》這款遊戲中玩家是需要做很多事情的,比如煉制藥劑、購買材料、賣出藥劑和經營商店等等,而遊戲的特色內容有很多,比如獨特視覺效果,靈感來自於中世紀的手稿和醫學書籍,更多如下。

遊戲特色內容介紹

遊戲特色:

獨特視覺效果,靈感來自於中世紀的手稿和醫學書籍。

與原料和設備的物理互動,帶來強烈的滿足感。

沙盒風格的遊戲,玩法豐富,找到完成每個任務的最佳方法取決於你自己。

在扮演高尚情操的手藝人、貪婪的奸商、神秘的黑暗大師或者任何你想成為的人的同時,將你的藥劑賣給鎮上的居民!

使用各種原料

樹葉、鮮花、漿果、根莖、水果、礦物和各種的蘑菇都在你的研缽和杵中准備好了。就像濃縮咖啡一樣,研磨得越細越好!

學習製作藥劑的藝術

制定你的藥劑計劃。把原料磨碎,在坩堝里仔細混合。把煤加熱。煮沸,攪拌。加入基底:水,油,或者其他東西。祝賀你,第一瓶藥劑做好了!簡單嗎?現在試著掌握它!

實驗和發明新的配方

通過鍊金術地圖仔細規劃你的合成路線,以達到不同的效果。但要注意常識:你不會覺得一個有毒的治療藥劑是有市場的吧……你會嗎?

出售藥劑

每天都有顧客光臨到你的商店尋求解決他們問題的方法。你將面臨的後果取決於你決定賣給他們什麼。吸引行會,與知名人士交好(或與他們結仇),獲得財富和影響力,也許在某天,你甚至可能會決定整個鎮子的命運。

購買原料或自己種植

每個鍊金術士都需要原料。你可以從旅行商人那里買到:價格可能會很貴,但成功的討價還價可能會幫你省下一筆錢。或者你可以選擇自己種植!

創造性地定製

想為你最好的藥劑設計一個特別的外觀嗎?沒問題!改變瓶子形狀,標簽類型,圖標和顏色。你甚至可以為它自定義名字和標簽描述。小心翼翼地將你獨特的藥劑擺放到你商店的架子和桌子上展示……或者隨意地把它們扔得到處都是。我們不會告訴你該怎麼做,只要你玩得開心就好!

來源:3DMGAME

《藥劑工藝:鍊金術士模擬器》遊戲配置要求一覽

《藥劑工藝:鍊金術士模擬器》是一款非常有趣的單人模擬角色扮演遊戲,說白了就是鍊金術士模擬器,不過遊戲是2D畫面需要的配置要求也不算高,CPU最低只需要一顆比較新的多核處理器就行了,更多如下。

遊戲配置要求一覽

需要 64 位處理器和作業系統

作業系統: Windows 7 and up

處理器: Dual-core

記憶體: 4 GB RAM

顯卡: GTX 650 and up

存儲空間: 需要 2 GB 可用空間

來源:3DMGAME

科學家開發更環保的牛仔褲染色工藝 無需使用有毒化學品

據媒體報導,雖然人們可能認為藍色牛仔褲是一種樸素的常見服裝,但它們的染色過程絕對不是環保的。然而,由於一種新的染色工藝的開發,這種情況可能很快就不會再出現。通常,在牛仔褲的染色過程中,天然或(更常見的)合成靛藍染料與水混合,隨後將牛仔布浸入其中。由於這兩種形式的靛藍染料在初始狀態下都不溶於水,因此必須添加有毒的還原劑,如亞硫酸氫鈉,才能使其溶於水。

在這個過程完成後,廢水被釋放回當地的水道中。雖然政府的規定確實要求首先從其中去除大部分的化學物質,但水無一例外地保留了一些污染物。

在Sergiy Minko教授和博士生Smriti Rai的領導下,喬治亞大學的科學家們設計了一種替代工藝,將靛藍顆粒與木漿衍生的纖維素納米纖維、一種被稱為殼聚糖的天然糖(可從海產品廢料中獲取)和水混合。雖然到目前為止已經利用了天然靛藍,但研究人員表示,也可以使用合成靛藍。

當產生的水凝膠應用於未經處理的牛仔布時,納米纖維素纖維形成了一個網狀的塗層,包裹住了靛藍顆粒,將它們粘附在牛仔布纖維上。殼聚糖增強了粘附性和固定性,確保在材料乾燥並隨後被穿著和洗滌後,靛藍仍然與牛仔布粘合在一起。

這項技術不僅不需要使用任何有毒化學品,而且在將染料固定在牛仔布中方面也比現有工藝更有效。這意味著需要的水和染色時間要少得多。根據該大學的說法,為了使牛仔布達到所需的藍色,現有的工廠在對一條牛仔褲進行多次浸染時,需要消耗50到100升的水。

此外,通過新技術染色的牛仔布與傳統染色的牛仔布具有大致相同的厚度、重量和彈性。

「牛仔布和牛仔褲製造是一個很大的市場,所以即使是行業中的小變化也會產生巨大的影響,」Minko說。「有一些人群正在尋找以環境友好方式製造的產品。而且隨著法規變得更加嚴厲,該行業將不得不進行調整。」

關於這項研究的一篇論文最近發表在《綠色化學》雜誌上。

來源:cnBeta

新的化學工藝可將下水道的硫化氫氣體轉化為氫氣

研究人員已經開發出一種新的化學工藝,能夠將下水道系統中產生的氣體轉化為可用於燃料的氫氣。該工藝可以轉化有著臭雞蛋味道的硫化氫,通常被稱為下水道氣體,從糞便堆和下水道管道內排放出來。硫化氫也是在一些工業過程中產生的副產品,包括煉油、采礦和其他。

俄亥俄州立大學的科學家們創造的工藝的一個重要方面是,它相比傳統工藝需要相對較少的能源,而且所需的材料也相對便宜。該工藝的關鍵材料包括硫化鐵和微量的鉬。硫化氫是工業生產過程中產生的最有害的氣體之一,對環境和遇到它的人的健康都有相當大的害處。

由於這種氣體是有害的,研究人員一直致力於將其轉化為有用的東西的過程。研究人員使用了以前創造的一種叫做化學循環的工藝。該工藝在高壓反應器中加入金屬氧化物顆粒,使其能夠燃燒燃料,而不需要空氣和燃料之間的接觸。當應用於硫化氫時,該工藝被稱為SULGEN。然而,研究小組在研究過程中發現,純硫化鐵的性能並沒有達到工業過程所需的規模。

研究人員開始尋找能夠催化該反應的其他化學品,並最終發現,微量的鉬與硫化鐵可以實現所需的反應。此外,這兩種材料都相對便宜且容易獲得,使它們適合於工業規模的轉換過程。

當硫化氫被轉化為氫氣燃料時,它可以被用作石油和天然氣的替代品,這就減少了對環境的影響。然而,項目研究人員說,現在要知道他們的工藝是否可能取代市場上已有的其他類似技術還為時過早。

來源:cnBeta

三星堆發現24k純金小金珠:毫米大小含金量超99% 工藝成謎

9月10日,四川德陽三星堆遺址5號坑發現不少金珠,通過探測發現,三星堆小金珠含金量超99%,幾乎是純金。5號坑雖然是三星堆「祭祀坑」中面積最小的,但卻是含「金」量最高的。專家表示這可能是中國最早的金珠成形工藝。 專家表示,這些小金珠我們已經關注很久了,它的尺寸實際上非常地小,小的只有零點幾毫米,大的也無非一兩毫米左右。

它們如何形成有兩種可能性,一是其他金器在燒熔過程中,滴落下的金珠;二是三星堆先民採用專門工藝來製作的。目前更傾向後一種可能。

如果能夠證實的話,那這應該是中國目前發現最早的金珠成型工藝,可以說是非常重要的。這些還僅是推測,需要更多證據的支持。

值得一提的是,早先考古人員還在三星堆遺址5號祭祀坑發現一件金器,目前只露出一部分,有網友說長得像鍋鏟。

考古人員介紹,這件金器頗有厚度,與此前三星堆發現的薄片狀金器不同,其形制在三星堆也是獨一無二的;完整形制、具體用途尚需進一步發掘和研究。

來源:cnBeta

傳Xbox Series S新版本採用6納米工藝 性能提升55%

據YouTuberMLID(Moore』s Law is Dead,摩爾定律已死)爆料,微軟計劃在2022年底開始推出次世代主機Xbox Series

S的新版本。

首先獲得疊代的是Xbox Series S,新版本主機將搭載更高配置的AMD Zen

APU,基於6納米製程(7納米改良版)。由於良品率更高,微軟將可以在其Xbox Series S APU上開啟全部的24個計算單元。

值得一提的是,當前的XSS主機只開啟了20個計算單元,多達4個計算單元被關閉,這是為了保證好的良品率和對主機的穩定供應。由於有了更多的計算單元以及可能更高的時鍾頻率,新版XSS的性能甚至可能會提升55%。

當然性能更高的主機,定價也比之前更高。新版的XSS定價接近350美元,比當前機型多了50美元。不過微軟到時候可能會降低老版本XSS的價格到189-249美元。這意味著XSS新老機型將一起販賣。

Xbox視自己是一個長期的Saas(軟體即服務)公司,XSS有著很高的Game Pass使用率,微軟還希望使用新版XSS來對抗可能的PS5

Slim。

MLID沒有提到新版XSS將仍然使用Zen 2還是換成Zen 3架構。2022年AMD將發布搭載RDNA2和Zen3微架構的Rembrandt

APU,這是第二代Zen3移動產品。考慮到Cezanne (Zen3)的變化,新版XSS可能會換用Zen 3架構。

此外,MLID還表示Xbox Series X主機的新版本將在2023年或更晚時候推出,不過關於這款新版本,暫時沒有細節流出。

與之對比的是,MLID提到了PS5 Pro,計劃推出時間是2023-2024年之間,玩遊戲最高支持8K解析度。

來源:3DMGAME

《藥水工藝:鍊金術師模擬器》9月21日上線 暫不支持中文

近日,發行商TinyBuild正式宣布《藥水工藝:鍊金術士模擬器》搶先體驗版將於9月21日正式上線Steam,暫不支持中文,感興趣的玩家可以點擊此處進入商店頁面。

開放人員表示:「搶先體驗版將不同於試玩Demo,其中含有大量基於玩家反饋的新添加配方以及相應的遊戲玩法改進。」

遊戲介紹:

在《藥水工藝:鍊金術師模擬器》中玩家將成為神秘的鍊金術士,利用工具和草藥研磨製作功能不同的藥水,並與顧客進行交易。發掘神奇新配方,購買種植草藥,進行特殊瓶裝定製,滿足不同顧客需求。

遊戲截圖:

來源:3DMGAME

中芯國際先進工藝產能緊張擴產計劃不變

二季度,中芯國際先進工藝(FinFET/28納米)的財務表現十分亮眼,單季銷售收入環比增長158%,收入占比環比提升7.6個百分點至14.5%。8月6日,中芯國際聯合執行長趙海軍在二季度電話會議上表示,「從現在看,我們的FinFET工藝產能處在緊張狀態,還有很多客戶和新產品不斷進來。我們對這部分產能未來的訂單不是很擔心。」

由於去年底被列入實體清單,采購周期延長,市場對中芯國際能否如期推進擴產計劃存有顧慮,趙海軍稱計劃不變。8月6日下午,中國證券報記者實地走訪中芯京城一期工程項目建設現場發現,相比半年前破土動工時的場景,已有多座單體建築拔地而起,大量起重機正在有序作業。「晚上也有人在幹活。工人吃住都在工地。」一位安保人員說,多地出現疫情後,人員進出管控升級,工人外出需要分包負責人和總包負責人簽字。

代工需求持續火爆

電話會上,趙海軍率先對晶圓代工行業的景氣度做了分析。他認為,「宅經濟」對於萬物互聯的需求持續給晶片行業帶來市場機遇。市場需求主要來自三部分:一是原有的存量需求依然穩固;二是各類產品升級帶來增量,例如4G到5G產品的遷移、普通充電到快充的普及、電動汽車及充電樁的上量、智能家居的短距互聯通訊等,使單一終端產品的矽面積增加,總使用量也大幅增加;三是行業形態發生了轉移,本土生產、在地生產的製造需求大大增加。「這三個部分的需求疊加在代工行業上,就造成了行業的產能供應不足,特別是配套瓶頸問題尤為突出。」

中芯國際也交出了一份靚麗的答卷。二季度,公司實現營業收入13.44億美元,環比增長21.8%,盈利6.88億美元,環比增長332.9%。同時,公司將今年全年營收成長目標上調為增長約30%。

進一步看,在成熟製程方面,「我們穩扎穩打,用高質量和具有性能競爭力的產品使客戶滿意。我們這幾年主力布局的七大應用、八大產品平台正是現在市場上齊套性有突出問題的領域。在產能有限的情況下,我們秉承一貫的產能分配原則,優先滿足長期戰略客戶,然後是高價位、高毛利產品以及客戶重要產品的需求。」趙海軍說。

趙海軍表示,「先進位程(FinFET/28納米)方面,產品平台開發繼續推進,客戶拓展與產品多元化的儲備效應逐步顯現出來。二季度,先進位程產能利用率爬升,業績好於預期,預計全年對公司整體毛利率的不利影響從10個百分點下降到5個百分點左右。但由於受到大環境的影響,產能擴充速度受到限制,先進位程尚未實現規模經濟效應。」

產能擴張計劃不變

除業務之外,趙海軍重點介紹了出口許可准證申請和擴產的進展。「被列入實體清單以來,中芯國際一直在困境中前行,公司全體也一直在努力,為此付出了大量的人力、物力和財力。生產連續性方面,我們積極與供應商方面配合,保證對客戶的承諾得以實現,成熟工藝的不確定性進一步降低。產能擴建方面,我們仍按計劃推進,二季度末,公司約當8英寸晶圓的月產能擴產至56萬片,較上季度末增加了2萬片。」

由於實體清單的影響,采購周期有所延長,中芯國際年內擴產目標能否達成,趙海軍在電話會上給投資者吃下了一顆「定心丸」。他說,「設備到達主要發生在下半年,出貨體現在四季度或來年的一季度。從現在拿到的供應商承諾來看,應該說可以實現這個目標:北京廠12英寸增加一萬片,在12月出貨;8英寸擴產主要在深圳和天津,增加4.5萬片,會在四季度實現。」

至於明年擴產28nm製程是否存在困境這一提問,趙海軍回復說,「我們跟供應商、客戶等一直有密切交流,大家也在想辦法,細節不便透露太多,但辦法還是可以想出來的。同時,我們也有第二供應商的解決方案,大家也在努力地去驗證。」

趙海軍補充道,公司在一些技術節點上可以取得批文。但他也坦言,「14nm和28nm設備准證方面有延遲,但我們的供應商還在努力做這件事,我們也在努力溝通。」

研發投入會逐漸增加

中芯國際二季度毛利率的提升主要來自產能提升、產品結構調整和漲價。其中,漲價因素影響約為9%。

業內普遍預期,全球晶圓產能緊缺狀況至少要持續到2022年。這意味著未來晶圓代工市場存在漲價可能。

趙海軍認為,「(全球晶圓)產能擴建的速度很慢,交貨也很慢,想很快開出新產能來緩解供不應求的狀況,到明年上半年都不太可能。疫情和國際環境的不確定性也還在,大家要建立庫存,保證供應還是要繼續進行下去。所以,三四季度價格繼續提升是有可能的。」

趙海軍強調,「我們會跟客戶商量好怎麼做,相信在未來價格能夠持續穩定或者上漲。這主要還是來自於我們在細分市場的競爭力,就是在細分市場的一些節點上,產能會一直緊張下去。」

日前,有媒體透露,台灣的多家晶圓代工廠准備在明年一季度之前提高成熟製程的8英寸和12英寸晶圓報價,提價幅度至少為5%-10%。

趙海軍表示,「到現在為止,我們漲價是比較慢的。我們比較謹慎,尊重契約,實行以長期能夠實現穩定性的戰略。」

值得注意的是,中芯國際二季度研究及開發開支為1.43億美元,環比下降8.5%,同比下降9.5%。「研發投入是公司的未來,我們一定會把這些調整都補回去的,未來的研發投入會逐漸增加。」趙海軍說。

來源:cnBeta

中芯國際:FinFET工藝已量產 產能1.5萬片 客戶不斷湧入

8月5日晚,中芯國際發表了2021年Q2財報,,環比增長21,8%,歸母淨利潤為6.88億美元,環比增長332.9%,同比增長398.5%。

在財報電話會上,中芯國際聯席CEO趙海軍也透露了公司的先進工藝的情況,表示「我們的FinFET工藝已經達產,每月1.5萬片,客戶多樣化,不同的產品平台都導入了。(這部分)產能處於緊俏狀態,客戶不斷進來。」

根據之前的報導,中芯國際的FinFET工藝有多種類型,其中第一代FinFET工藝是14nm及改進型的12nm,目前1.5萬片產能的主要就是14/12nm工藝,第二代則是n+1、n+2工藝,已經試產,但產能不會有多大。

根據中芯國際聯席CEO梁孟松博此前公布的信息顯示,N+1工藝和現有的14nm工藝相比,性能提升了20%,功耗降低了57%,邏輯面積縮小了63%,SoC面積減少了55%。

從邏輯面積縮小的數據來看,與7nm工藝相近。

梁孟松博士也表示,N+1代工藝在功耗及穩定性上跟7nm工藝非常相似,但性能要低一些(業界標準是提升35%),所以中芯國際的N+1工藝主要面向低功耗應用的。

而在N+1之後,中芯國際還會有N+2,這兩種工藝在功耗上表現差不多,區別在於性能及成本,N+2顯然是面向高性能的,成本也會增加。

此外,梁孟松還透露,中芯國際的28nm、14nm、12nm、N+1等技術均已進入規模量產,7nm技術開發已經完成,今年4月可以進入風險量產,5nm、3nm最關鍵也是最艱巨的8大項技術也已經有序展開,只等EUV極紫外光刻機到來,就可以進入全面開發階段。

來源:快科技

科技以「改名為本」?別讓半導體工藝名稱收了「智商稅」

2021年7月29日,在本周的Inel Accelerated大會上,英特爾CEO帕特·基辛格和他的團隊分享了最新的工藝路線圖,並且介紹了相關工藝的研發情況。在英特爾製程技術路線圖,工藝名稱發生了較大改變。

英特爾將之前的10納米Enhanced SuperFin更名為現在的Intel 7。之前的Intel 7納米更名為現在的Intel 4。在路線圖上之後規劃的工藝名稱也變成了Intel 3和Intel 20A。

別再被工藝名稱中的幾納米誤導了

長期以來,很多數碼圈的朋友甚至是一些學習過集成電路知識的專業人士都存在著這樣的誤會,就是把工藝名稱中的幾納米真的當成電晶體上某種實際的「物理尺寸」。這種理解在許多年以前是沒問題的,但對於近些年新研發的一些「先進工藝」是不適用的。

工藝名稱中的幾納米到底是什麼?

在遙遠的過去與一些「物理尺寸」相關,而對於現在,什麼也不是。

遙遠的過去是什麼時候?

上個世紀,大約1997年。

英特爾在發布路線圖時表示「業界早就意識到,從1997年開始,基於納米的傳統製程節點命名方法,不再與電晶體實際的柵極長度相對應。」

台積電此前也回應過類似的問題,台積電營銷負責人Godfrey Cheng做客AMD webinar活動時回應,從0.35微米(350nm)開始,所謂的工藝數字就不再真正代表物理尺度了。他解釋,7nm/N7是一種行業標準化術語而已,之後還有N5等等。

如何理解工藝名稱中的幾納米?

簡單點說當成個代號就就好。

我們拿手機廠商的命名舉個例子,很多手機廠商多以數字來命名手機型號。比如:小米10、華為暢享10、iPhone x(勉強也算以10命名)。但是這時候如果有人說:「這幾款手機都是以10命名的10代手機,所以它們應該是差不多的。」

手機廠商不同,只是因為命名相近就得出這樣的結論,這顯然是沒有邏輯關系的。

對於半導體工藝來說也是這樣的,不同廠商之間的同命名產品,差距其實挺大的。具體舉例來說,如果按「命名法」理解,台積電的7nm應該是比英特爾的10nm電晶體密度高。但事實並非如此,英特爾10nm工藝的電晶體密度是比台積電的N7(7nm)要高。

如果把工藝名稱理解成某種「物理尺寸」比如關鍵尺寸(Critical Dimension,簡稱CD),那麼就很容易造成以上這種誤解了。專業人士有這種誤解的原因也很簡單,就像「關鍵尺寸」當年是寫入專業課課本甚至作為考題出現的。這些知識並沒有錯,只是時代變了,不適用於近些年的工藝了。

從另一方面說,這種情況也是無奈。當普通人問:「幾納米工藝的幾納米是指什麼?」這時要怎麼回答呢?

在不同歷史時期幾納米是指什麼;

對於不同的廠商,他們工藝之間的不同是什麼;

對於同一個廠商,同一個工藝節點的不同型號工藝(比如台積電N7/ N7P/ N7+)差別又是什麼。

所以想要准確的回答這種問題,其實挺難的。

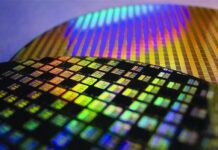

圖片僅作為示例,文檔中有各種尺寸的設計規則

不過對於從業者,這個倒好解決了,晶圓代工廠對於每種工藝都會提供一個描述文件,這個文件一般挺厚的,會很清楚的描述一種工藝哪里到哪里的尺寸是多少。

改名之爭的開端

對於了解半導體行業的朋友來說,摩爾定律應該是比較熟悉了。摩爾定律是英特爾創始人之一戈登·摩爾的經驗之談,他發現每隔18-24個月,晶片上電晶體數目就增加一倍。

為了使電晶體密度翻倍,每個電晶體尺寸需要縮小為原來的0.7倍,因此工藝節點也是以前一代工節點的0.7倍命名。例如350nm(0.35微米)下一代工藝就是250nm(0.25微米)。

*關於為什麼是0.7倍

舉例來說晶片面積假設為100,里面每個電晶體假設為正方形,邊長為a,對角線長度為b。

當電晶體數量由100翻倍到200後,邊長a和對角線長度b的尺寸都變為了原來的大約0.7倍。

因此0.7倍這樣的命名方式成為了業界的一種習慣,但是並不是每一次都能順利縮小電晶體尺寸。

從數據中我們可以看出,在0.35微米(350nm)之後,工藝代號與half-pitch(半節距)和Gate length(柵極長度)就已經不再相符了。

起名方式的分歧

工藝代號與「物理尺寸」之間的數據偏移其實並不麻煩,真正麻煩的是各家的標準不一樣。這時候主要分為了兩派,一派以英特爾為代表,另一派是以台積電、三星這些企業為代表。

英特爾這邊直到最近幾年都在堅持每一代工藝電晶體密度翻倍,而台積電、三星這邊則是工藝有提升就使用新一代工藝名稱發布。這就造成了一個結果,同樣是10nm工藝,英特爾的10nm工藝電晶體密度可能是三星10nm工藝的兩倍。

為什麼現在改名?

這之前這幾年,台積電嚴格來說不算是英特爾的同行。在很多晶圓代工廠排名榜上我們可以發現,台積電常年位居首位,而三星緊跟其後。但排行榜上卻沒有英特爾的影子。這不是因為英特爾實力不行,而是因為這幾年英特爾基本不從事晶圓代工。大約在2018年,英特爾關閉了晶圓代工業務,從此開始過上了自產自銷的生活。

2021年三月,帕特·基辛格就任CEO後宣布了「IDM 2.0」戰略,在這個戰略中,英特爾重新開放了晶圓代工業務。而此時晶圓代工行業的客戶早已習慣了「台積電式」的工藝命名。因此這次英特爾工藝大改名可以看做是向晶圓代工行業的一種妥協,命名方式也貼近台積電的標準進行。

在此次改名中將原有的「10納米Enhanced SuperFin」改名為了「Intel 7」工藝,這個名字是不帶「nm(納米)」的,這種命名方式也可以看做是英特爾在命名上最後的倔強了。

結語

在文章的最後,我有一些想法和補充的信息,在此分享給大家。

1.工藝名稱早已代號化了,現在還在用這種命名方式只是一種習慣。對於例如美光這樣的存儲晶片大廠,有著1X、1Y、1Z以及最近的1α這樣的工藝名稱。中芯國際也有N+1和N+2工藝。

2.科技以改名為本,工藝名稱數字小,營銷效果好。如今濃眉大眼的英特爾也把工藝命名改得像台積電了。不得不說,工藝名稱數字小,真香!

3.不同晶圓廠的工藝都存在差異,即使是同一廠家的同一個工藝節點,也有可能存在差異。對於拿不到設計規則文件的非從業者來說難以精確比較。

4.如果只是粗略比較,可以對比兩個工藝的電晶體密度,電晶體密度越高越好。

5.對於讀到這里的朋友,留一個思考題給大家。

對於一些專家所說的14nm夠用了,這里的14nm指的是中芯國際的14nm還是英特爾的14nm?

如果指的是中芯國際的14nm,那還好。可如果指的是英特爾的14nm,那麼對於電晶體密度打了大概67折之後的中芯國際14nm是否還夠用呢?

來源:cnBeta

Intel發布史上最詳細工藝和封裝技術路線圖 CEO:再一次領先業界

今天,Intel發布了公司有史以來最詳細的製程工藝和封裝技術路線圖,展示了一系列底層技術創新。

除了公布其近十多年來首個全新電晶體架構RibbonFET 和業界首個全新的背面電能傳輸網絡PowerVia之外,Intel還重點介紹了迅速採用下一代極紫外光刻(EUV)技術的計劃,即高數值孔徑(High-NA)EUV。

據悉,Intel有望率先獲得業界第一台High-NA EUV光刻機。

Intel CEO帕特·基辛格表示,基於Intel在先進封裝領域毋庸置疑的領先性,我們正在加快製程工藝創新的路線圖,以確保到2025年製程性能再度領先業界。

Intel正利用我們無可比擬的持續創新的動力,實現從電晶體到系統層面的全面技術進步。在窮盡元素周期表之前,我們將堅持不懈地追尋摩爾定律的腳步,並持續利用矽的神奇力量不斷推進創新。

Intel技術專家詳述了以下路線圖,其中包含新的節點命名和實現每個製程節點的創新技術:

基於FinFET電晶體優化,Intel 7與Intel 10nm SuperFin相比,每瓦性能將提升約10%-15%。2021年即將推出的Alder Lake客戶端產品將會采Intel 7工藝,之後是面向數據中心的Sapphire Rapids預計將於2022年第一季度投產。

Intel 4完全採用EUV光刻技術,可使用超短波長的光,刻印極微小的圖樣。憑借每瓦性能約20%的提升以及晶片面積的改進,Intel 4將在2022年下半年投產,並於2023年出貨,這些產品包括面向客戶端的Meteor Lake和面向數據中心的Granite Rapids。

Intel 3憑借FinFET的進一步優化和在更多工序中增加對EUV使用,較之Intel 4將在每瓦性能上實現約18%的提升,在晶片面積上也會有額外改進。Intel 3將於2023年下半年開始用於相關產品生產。

Intel 20A將憑借RibbonFET和PowerVia兩大突破性技術開啟埃米時代。RibbonFET是Intel對Gate All Around電晶體的實現,它將成為公司自2011年率先推出FinFET以來的首個全新電晶體架構。該技術加快了電晶體開關速度,同時實現與多鰭結構相同的驅動電流,但占用的空間更小。

PowerVia是Intel獨有的、業界首個背面電能傳輸網絡,通過消除晶圓正面供電布線需求來優化信號傳輸。Intel 20A預計將在2024年推出。Intel也很高興能在Intel 20A製程工藝技術上,與高通公司進行合作。

2025年及更遠的未來:從Intel 20A更進一步的Intel 18A節點也已在研發中,將於2025年初推出,它將對RibbonFET進行改進,在電晶體性能上實現又一次重大飛躍。

Intel還致力於定義、構建和部署下一代High-NA...

俄羅斯自己造處理器 12nm工藝、八核心2GHz

據俄媒報導,俄羅斯政府投資的大型科技企業Rostec已經與晶片設計公司Syntacore、伺服器公司Yadro達成合作協議,開發一款自己的處理器,採用開源的RISC-V架構,面向俄羅斯政府、教育機構的台式機、筆記本、伺服器。

這款處理器將採用RV64GC指令集,靈活微架構,10-12級流水線,規劃最多8個核心,主頻為2GHz,製造工藝為12nm,但不清楚是否由GlobalFoundries代工。

技術方面,該處理器擁有完整記憶體和緩存子系統,包括記憶體管理單元(MMU)、頁面虛擬記憶體、一二級一致性緩存、ECC,集成高性能的IEEE 754-2008標準浮點單元、可編程中端控制器(IPIC)、調試控制器。

作業系統面向Linux,支持用戶、監管(supervisor)、機器三種權限級別模式。

項目計劃在2025年前首批生產6萬顆處理器和配套整機,初期供給俄羅斯教育與科學部、衛生部。

整個項目投資約300億盧布,約合人民幣26億元,其中1/3由俄羅斯聯邦資助。

值得一提的是,Syntacore此前已經開發過自己的RISC-V架構核心,而不是簡單地購買授權,但現階段,RISC-V的性能是否可以滿足日常辦公還未可知,尤其是Rostec的頻率只有區區2GHz。

來源:遊民星空

三星Exynos 2200 SoC曝光 4納米工藝 集成RDNA2

媒體消息,三星的下一代旗艦處理器——Exynos 2200正在准備中, Exynos 2200的處理器代號為「Pamir」,採用4納米製程工藝,集成AMD RDNA2圖形架構,預計今年下半年將正式亮相。

三星的目標對手是高通的驍龍895 SoC及其Arm Adreno 730 GPU,有趣的是,新的驍龍也有望基於4納米的製程工藝。

來源:遊民星空

歐洲沖向2nm工藝:Intel甩出1300億元建廠

全球缺「芯」,作為半導體行業龍頭的Intel也產能緊張,擴建工廠勢在必行。

Intel今天披露,計劃投資200億美元(約合人民幣1300億元),在歐洲建設新的半導體晶片工廠,而且可能會在多個歐盟成員國同時投資。

目前,Intel正在就此向歐盟游說,希望能獲得資金、政治方面的支持,以及占地超過4平方公里、基礎設施發達的場地,可建設最多8座晶圓廠,並且能夠招聘到足夠的人才。

Intel已經在德國、荷蘭、法國、比利時等地尋找適合建廠的地方,預計今年底完成選址工作。

Intel計劃首先建設兩座晶圓廠,10年運營總成本約200億美元,而工廠的整個生命周期內,總投資可能超過1000億美元。

歐盟近來在半導體領域提出了一系列野心勃勃的目標,比如2030年晶片產量翻番,全球份額占比達20%,並攻克先進的2nm工藝,能效至少翻10倍。

Intel雖然近年來在半導體工藝上屢屢受挫,但實力依然是超一流的,如果歐盟能得到Intel的助力,無疑是巨大的幫助。

來源:快科技

華中科技大學團隊發現新製造工藝 可讓塑料更安全、更快速降解

通過改變塑料的製造工藝,科學家們希望讓這種無處不在的材料能更安全、更快速的分解。來自武漢華中科技大學的科研團隊近日展示了一個新案例,當塑料暴露在陽光和氧氣下,採用新型製造工藝的塑料只需要 1 周時間就能降解。他們認為這項研究可以使電子產品在壽命結束後更容易處理。

據悉該項目是華中科技大學的 Liang Luo 在研究一種先進的化學傳感器時發現的。這位材料科學家正在開發一種新型的聚合物薄膜,它能根據 pH 值的變化而改變顏色。這一過程是由該材料獨特的分子結構驅動的,單體鏈使薄膜呈現出深紅色,而當這些鍵被打破時就會失去顏色。

通過他帶領團隊的實驗,Luo 發現薄膜的深紅色很快就消失了,而且材料在陽光下幾天後就破裂了。打破這些鍵是更好地回收塑料的研究工作中的一個共同目標,在這樣做的過程中,Luo 可能無意中創造了一種有希望的、環保的材料版本。

這種塑料的分子構成意味著它不適合用於汽水瓶或購物袋,因為它只有在黑暗和沒有氧氣的情況下才能穩定地成為一種功能性材料。但是暴露在陽光和空氣中,它就會迅速瓦解,並在一周內完全分解,不會留下破壞環境的微塑料碎片。然而,該過程的一個副產品是自然產生的琥珀酸,它有可能被回收用於制藥或食品的商業用途。

然而,這種塑料可以在柔性電子產品或智能手機中找到用武之地,在那里它將在其使用壽命中與空氣和光線隔離。Luo想像,以這種方式使用時,這種材料可以持續數年,然後使這些類型的設備在使用後更容易處理。他計劃繼續探索圍繞這些類型的可降解塑料的可能性,但指出商業化仍需數年時間。

來源:cnBeta

曝蘋果M2晶片延期亮相 還是5nm工藝、全新架構

據此前消息,蘋果將會在9月份左右推出一款搭載M1升級款晶片的MacBook Pro,這款晶片之前一直被認為是蘋果第二代自研晶片M2。

不過從最新的一些消息來看,這款晶片只是M1的小幅升級版,將會被命名為「M1x」。

這就意味著,蘋果M2自研晶片的亮相還有很長一段時間,前不久有爆料者稱M2會在明年上半年登場,但是今天再次有新的爆料傳出,這款新品受到一些外在、和設計上的影響,將延期發布。

從DigiTimes的最新報告來看,M2晶片在量產時將會採用全新的架構,整體上類似於A15 Bionic,基於台積電N5P工藝打造,但是受供應鏈等方面的限制,預計將會在2022年5月份開始量產,並在下半年正式發布。

而新一代多彩設計的MacBook Air依然是最有可能首發這款晶片的產品,此前消息稱蘋果將在明年對MacBook Air進行一次較大的升級,除了性能方面的改進之外,外觀上也將發生重大變化,其整體與新款的iMac設計語言非常相似,並且連配色幾乎一一對應。

前段時間,還有海外機構曝光新MacBook Air的渲染圖,展示了該機的外觀設計,其中顯示該機將同步當前iPhone 12和iMac的機身設計,整體邊框採用直角方案,並且在左右側各配備了一個USB -C規格接口。

來源:遊民星空

曝蘋果M2晶片延期亮相:還是5nm工藝、全新架構

據此前消息,蘋果將會在9月份左右推出一款搭載M1升級款晶片的MacBook Pro,這款晶片之前一直被認為是蘋果第二代自研晶片M2。

不過從最新的一些消息來看,這款晶片只是M1的小幅升級版,將會被命名為「M1x」。

這就意味著,蘋果M2自研晶片的亮相還有很長一段時間,前不久有爆料者稱M2會在明年上半年登場,但是今天再次有新的爆料傳出,這款新品受到一些外在、和設計上的影響,將延期發布。

從DigiTimes的最新報告來看,M2晶片在量產時將會採用全新的架構,整體上類似於A15 Bionic,基於台積電N5P工藝打造,但是受供應鏈等方面的限制,預計將會在2022年5月份開始量產,並在下半年正式發布。

而新一代多彩設計的MacBook Air依然是最有可能首發這款晶片的產品,此前消息稱蘋果將在明年對MacBook Air進行一次較大的升級,除了性能方面的改進之外,外觀上也將發生重大變化,其整體與新款的iMac設計語言非常相似,並且連配色幾乎一一對應。

前段時間,還有海外機構曝光新MacBook Air的渲染圖,展示了該機的外觀設計,其中顯示該機將同步當前iPhone 12和iMac的機身設計,整體邊框採用直角方案,並且在左右側各配備了一個USB -C規格接口。

來源:快科技

RTX 40系列明年底或後年初發布:5nm工藝、性能兩倍於RTX 3090

,NVIDIA今年的GPU架構仍然是Ampere,也就是不會有全新的RTX 40系列,下代架構要等明年,未來延續2年更新一次架構的節奏。

據推特網友@Greymon55最新曝料,RTX 40系列要等到2022年第四季度至2023年第一季度才會發布,也就是要再等上大概一年半。

新一代將採用台積電N5 5nm工藝製造(三星工藝不足以支撐如此大核心和高功耗),而在性能方面最高可以達到如今卡皇RTX 3090的兩倍之多!

早先傳聞稱,NVIDIA下代遊戲卡GPU架構代號Ada Lovelace——阿達·洛芙萊斯女士,詩人拜倫唯一合法的女兒,第一位計算機科學家,編寫了歷史上第一個電腦程式,人稱「數字女王」。

新架構的大核心編號AD102,將有多達12個GPC(圖形處理集群)、72個TPC(紋理處理集群)、144個SM(流式多處理器),而如果每個SM繼續128個流處理器(CUDA核心),那麼整體下來就有多達18432個流處理器!

相比於目前安培架構GA102核心的10752個,這一下子就增加了超過71%!

順帶一提,@Greymon55還曝料,RTX 30 Super系列升級版將明年初發布,首批有RTX 3080 Super、RTX 3070 Super,可能會使用新的GA103核心。

Ampere

來源:快科技

三星在5nm工藝節點陷入困境,報告指良品率低於50%

半導體製造不是一件容易的事,特別到了尖端的先進工藝,每一個工藝節點的遞進都相當不容易,即便英特爾或三星這種業界巨頭已經過多年的技術打磨和市場考驗,依然可以感受到晶圓製造方面的艱辛。可以想像台積電(TSMC)今天在工藝技術上的穩步推進,背後付出了多少努力。

圖:三星在韓國京畿道華城市建設中的Fab

據《BusinessKorea》報導,三星在5nm工藝節點再次陷入了困境,正在為提高產能而努力。雖然三星5nm工藝已量產多時,但良品率不到50%,這意味著單個矽晶圓上製造的晶片只有不到一半能用,這絕對不是好事情。通常情況下,一個工藝節點進入大批量製造階段,良品率需要達到95%左右,低於這個水平也就代表生產效率不高,利潤也難以保證。

目前三星負責5nm工藝生產的是韓國京畿道華城晶圓廠V1生產線,是三星最先進的晶圓生產線,也是世界上第一條用於7nm以下的專用極紫外(EUV)生產線。具體哪些產品受到大的影響,問題出在哪里,這些細節暫時也不清楚。三星是在2020年2月開始建立5nm工藝的生產線,然後花了幾個月的時間完成製造相關的准備工作。正常來說,生產上在某個時間點應該會超過閾值,最好是為客戶大規模生產第一批晶片的時候,然後經過細微的調整以確保良品率在90%以上。 ...

歐盟投上萬億發展2nm工藝 英飛凌唱反調:沒人會用

半導體技術對未來的重要性已經無需多說,現在世界主要國家和地區都在積極發展,其中歐盟也希望在先進工藝上分一杯羹,去年17個歐盟國家推出新計劃,將投資1450億歐元,約合1.2萬億人民幣發展半導體。

根據歐盟的計劃,他們在半導體上主要有2個目標,一個是希望2030年將晶片產量翻倍,市場份額提升到20%,另外就是計劃製造更先進的晶片,致力於在2030年生產出5nm到2nm的晶片。

歐盟地區自身的半導體技術很強大,更有全球知名的IMEC比利時微電子中心、ASML阿斯麥等研發中心,其中ASML是全球唯一量產EUV光刻機的公司,歐盟發展2nm工藝必不可少。

此外,歐盟還有多家全球性的半導體巨頭,比如ST意法半導體、英飛凌、NXP恩智浦等等,GF格芯在德國德勒斯登也有晶圓廠,似乎天時地利都有了。

然而歐盟的2nm工藝計劃卻沒有得到本地公司的支持,至少ST意法、英飛凌兩家都不打算參與,英飛凌給出的理由很簡單——歐盟要2nm晶圓廠有什麼用?誰會考慮在歐盟2nm工廠生產2nm晶片?

ST、英飛凌的理由很充分,2nm工藝很重要,但是要想建成2nm工藝,首先要解決的就是2nm工藝真能搞出來,有哪些客戶會用?這實際上是各國發展2nm工藝的核心問題。

ST、英飛凌在2nm工藝上唱反調的原因也很簡單,因為歐盟自己的晶片公司擅長的及所需要的晶片都不需要2nm這樣的先進工藝,ST、英飛凌、NXP的核心業務主要是汽車晶片、電源晶片等,很多晶片依然停留在90nm、65nm、55nm、40nm、28nm等節點,即便再高級一些,16/14nm、7nm節點也能滿足未來的需求了,沒有2nm工藝的需求。

來源:快科技

新工藝有望能更有效地回收電動汽車電池

據媒體報導,雖然電動汽車肯定比燃油汽車更環保,但它們的電池組仍沒有達到可回收的程度。通過更有效地從舊鋰離子電池中提取可重復使用的材料,一種新的工藝可能會有所幫助。作為英國法拉第研究所鋰離子電池回收項目的一部分,這項技術是由英國萊斯特大學和伯明罕大學的科學家開發的。

它的目標是有朝一日能取代現有的回收過程,在現有的回收過程中,電池通常要麼被放入碎紙機要麼被放入高溫反應堆。根據法拉第研究所的說法,這種方法不僅在物理和化學上復雜,而且它們也是能源密集型的,並且它們在從電池中獲取可重復利用材料方面效率低下。

這項新技術涉及到將鋰離子電池中的金屬箔電極放入一個機器中,在這個機器中,一個名為超聲波發生器(sonotrode)的設備將它們置於聚焦超聲脈沖中。這樣做會導致電極的活性材料塗層從底層的鋁或銅基層剝離。

因此,賤金屬和活性材料如鋰、鎳、錳和鈷都能以更純淨、更容易回收的形式得到回收。重要的是,據報導,這一過程比傳統技術更節能,據稱要快100倍。

這項研究的首席科學家、萊切斯特大學的Andy Abbott教授說道:「它的工作原理基本上跟牙醫的超聲波除垢器一樣,其打破了塗層和基體之間的粘合劑。這項技術的初步應用很可能會將回收材料直接送回電池生產線。這是電池回收領域真正的重大變革。」

法拉第研究所目前正在跟幾家回收公司和電池製造商進行談判,希望能獲得該系統的商業許可。計劃要求今年晚些時候在一個工業地點建立一個技術演示。

來源:cnBeta

科學家利用新型回收工藝將可生物降解塑料餐具變成可用的泡沫

據媒體報導,我們已經看到在生態友好型塑料領域取得了許多令人振奮的進展,這些材料在幾年甚至幾個月內就能在環境中安全分解。雖然這些材料是石油基塑料的絕對綠色替代品,但紐西蘭的科學家們已經想出了一種創新的方法來賦予它們「第二次生命」,進一步提高它們的環保資質。

這項工作是在紐西蘭坎特伯雷大學進行的,科學家們以可生物降解的餐具為出發點,這些餐具被認為是不可回收的。由PLA生物塑料製成的這些刀、叉子和勺子在使用後可以安全地被堆肥,但研究人員想出了一個辦法,在這些材料被永遠扔掉之前,將它們變成有用的材料。

該團隊的突破在於一個創新的處理過程,即把這種餐具放入一個充滿二氧化碳的房間。然後,在腔室中加大壓力,使二氧化碳溶解到塑料中。然後,當壓力突然被釋放時,氣體在塑料內膨脹,並將其變成泡沫。

根據該團隊的說法,這很像打開一罐蘇打水並釋放出碳酸的過程。有趣的是,科學家們發現他們可以通過對該過程進行調整來改變最終產品。例如,腔室中較低的壓力導致了帶有大量氣穴的體積較大的泡沫。

研究作者Heon Park說:「調整溫度和壓力,有一個窗口,我們可以製造出好的泡沫。並不是說每個溫度或每個壓力都有效。我們發現什麼溫度或什麼壓力最能使那些不能發泡的塑料變成泡沫。」

科學家們說,像浮標這樣的漂浮裝置是這些笨重的泡沫的一個可能的應用,而其他版本的泡沫可以進入牆體保溫。對於這些回收的生物塑料來說,泡沫是一個很好的結局,因為在大多數情況下,它們不需要提供很大的強度就能達到目的,而這一特性在塑料回收過程中通常會受到影響。而且有希望的是,科學家們認為該技術可以應用於更廣泛的材料。

Park說:「我們可以將發泡應用擴展到很多塑料,而不僅僅是這種塑料。」

這項研究發表在《流體物理學》雜誌上。

來源:cnBeta

研究人員通過光敏化學物質找到成本更低、效果更好的γ -環糊精生產工藝

據媒體報導,一項新的研究使得流行的化合物更便宜、對環境也更好。達特茅斯學院的一項研究顯示,使用光敏化學物質的工藝可以大大降低生產γ -環糊精的成本和能源消耗。γ -環糊精是一種廣泛用於製造業的化合物。

發表在《Chem》上的這項研究展示了一種腙模板如何取代能源密集型蒸餾來生產和分離γ -環糊精--一種吸引其他分子的水溶性化學物質並被用於改善食品、藥品和廣泛的消費品。

「這些化合物是可生物降解的、生物相容的、良性的、常用的,」達特茅斯大學化學教授Ivan Aprahamian說道,「我們正在提高生產效率以便更多地用於工業。」

環糊精是一種天然的化合物,它在使用前封裝並保存產品中的活性成分。這種水溶性化合物由葡萄糖構成,當酶被添加到澱粉中時就會產生。它們像甜甜圈一樣的形狀使其可以作為分子容器包圍其他化合物,直到它們被熱或其他物理過程釋放出來。

跟其他常見的環糊精如α -環糊精和β -環糊精相比,γ -環糊精體積最大、水溶性最強。

「這種分子的獨特結構有助於它容納像維生素和敏感染料這樣的大分子,」該研究的論文第一作者、達特茅斯阿普拉哈米亞研究小組的研究生Sirun Yang說道,「γ -環糊精在工業上已經很有用了,現在我們讓它更容易地用於制藥、食品和家用產品的生產商。」

在藥品中,這種化合物延長了藥物的保質期並使它們形成易於食用和消化的形式。空氣清新劑利用這種化合物捕捉難聞的分子、降低它們在空氣中的濃度。香水可用它來緩慢釋放氣味宜人的化合物。

據Aprahamian介紹稱,工業面臨的挑戰是γ -環糊精也是能源密集型和昂貴的制備和分離。截止到目前,還需要一種昂貴的蒸汽蒸餾過程來去除用於形成化合物的分子模板。

通過使用由光敏腙製成的模板,新工藝在酶生產過程中將γ -環糊精引導成獨特的容器狀甜甜圈形狀,然後可以使用成本效益高、環境友好的光輻照工藝將其去除。

「我們的方法依賴於使用腙,這是一種可以很容易地添加到γ -環糊精腔中的光開關,」Aprahamian說道,「一旦你引入光,它會改變形狀並離開腔體並促進化合物的分離。(這個過程)不再需要蒸汽蒸餾。」

跟更容易獲得的環糊精相比,新工藝使高功能化合物更具資源和價格競爭力。

由於生產成本更低,γ -環糊精可以被更廣泛地用於消費產品。對於制藥行業來說,增加這種化合物的使用將使製造商能配製出更低劑量的活性成分、使藥物更便宜並減少副作用。

來源:cnBeta

3nm工藝太貴 台積電被投行看衰 失去關鍵優勢

作為全球第一大晶圓代工廠,尤其是率先量產了先進的7nm、5nm工藝之後,台積電已經成為影響全球半導體產業的重要一環。接下來台積電還會量產3nm工藝,然而海外投資者這時候看衰台積電,認為3nm節點太貴,台積電將失去關鍵優勢。

台積電現在業績正佳,不少投行都是看好未來的,但也有投行發表了相反的看法,認為台積電被高估了,將其股價評級為中性,目標股價下調到580新台幣,比其他同行的目標價少了20%左右。

台積電被看衰的一個重要因素就是3nm工藝,原來台積電預計2022年量產3nm工藝,最近有傳聞說是會延期,不過就算沒有延期,3nm工藝巨大的投資也會提高成本,導致台積電的代工承壓,失去了關鍵性的議價優勢,它們的毛利率在2022-2023年會跌破50%,低於預期的52%。

除了3nm成本問題之外,台積電的先進工藝還會受到其他技術的影響,比如業界正在採納的3D晶片封裝,通過這種技術也可以降低能耗,而不再是單純依賴工藝微縮,台積電3nm甚至未來的2nm工藝需求也會減少。

來源:遊民星空

3nm工藝太貴 台積電被投行看衰:失去關鍵優勢

作為全球第一大晶圓代工廠,尤其是率先量產了先進的7nm、5nm工藝之後,台積電已經成為影響全球半導體產業的重要一環。接下來台積電還會量產3nm工藝,然而海外投資者這時候看衰台積電,認為3nm節點太貴,台積電將失去關鍵優勢。

台積電現在業績正佳,不少投行都是看好未來的,但也有投行發表了相反的看法,認為台積電被高估了,將其股價評級為中性,目標股價下調到580新台幣,比其他同行的目標價少了20%左右。

台積電被看衰的一個重要因素就是3nm工藝,原來台積電預計2022年量產3nm工藝,最近有傳聞說是會延期,不過就算沒有延期,3nm工藝巨大的投資也會提高成本,導致台積電的代工承壓,失去了關鍵性的議價優勢,它們的毛利率在2022-2023年會跌破50%,低於預期的52%。

除了3nm成本問題之外,台積電的先進工藝還會受到其他技術的影響,比如業界正在採納的3D晶片封裝,通過這種技術也可以降低能耗,而不再是單純依賴工藝微縮,台積電3nm甚至未來的2nm工藝需求也會減少。

來源:快科技

七種工藝合一 美國應用材料展示全新裝備:深入3nm

在半導體工藝延伸到7nm之後,光刻機越來越重要,EUV光刻機現在只有荷蘭ASML能生產。不過光有EUV設備也是不行的,美國半導體設備公司應用材料日前展示了一款全新的設備,能將7種工藝整合在一起,可用於3nm工藝。

美國應用材料公司是全球第一大半導體設備公司(ASML今年有望超越他們),雖然不做光刻機,但他們的PVD、CVD沉積設備等也是半導體製造中不可少的,也是限制台積電、三星、Intel等公司提升工藝的關鍵。

他們現在研發的設備名為Endura Copper Barrier Seed IMS,是用於邏輯晶片布線的,隨著電晶體的縮小,晶片布線也是個難題,而且導線越小電阻越大,從7nm微縮到3nm的話,電阻就會增加10倍,這會帶來更高的功耗,讓工藝微縮失去意義。

現在這套設備可以在真空環境下,將ALD、PVD、CVD、銅回流、表面處理、界面工程和計量等七種工藝處理集成到一個系統中完成,不僅簡化了操作,同時還降低了50%的電阻,晶片的性能及能效更高。

有了這個設備,三星、台積電及Intel從7nm延伸到3nm也有了可能,因為邏輯布線占的功耗已經達到了晶片功耗的1/3。

來源:快科技

製程工藝逼近極限 晶片將在中國超越摩爾定律

28nm、14nm、7nm、5nm、3nm……晶片巨頭們都在追求更小的製程,晶片真的越小越好嗎?製程工藝達到極限後還能怎麼提升?

的確,更小工藝製程可以大幅提高電晶體的密度,會帶來性能的大幅提升,同時帶來更低的功耗。

但目前的3nm已基本接近工藝極限。在製程達到7nm以下之後,短溝道效應和量子遂穿效應會越來越明顯,這將對工藝帶來極大的挑戰。

在6月9至11日的2021世界半導體大會暨南京國際半導體博覽會上,中國科學院院士毛軍發表示,晶片現在有兩條路線,一個是延續摩爾定律,一個是繞道而行。

延續摩爾定律方面,當前,半導體大廠正通過工藝、結構、材料的精進做成新型器件,使得技術能夠沿著摩爾定律繼續往前走,但在這條路上,產業要克服的技術和成本難題有很多。

而所謂繞道而行,就是推動集成電路從單一同質、二維平面,發展到異質集成、三維立體,可以突破單一工藝集成電路的功能、性能極限,算是一種新的技術路徑。

這一路徑挑戰也不會少,毛軍發提出三個挑戰,多物理調控,包括電磁、溫度、應力;多性能協同,包括信號、電源完整性,熱、力;多材質融合,包括矽、化合物半導體、金屬等。這些方向的改變,似乎帶來了更多的技術問題。

還有第三條路:超越摩爾定律。賽迪顧問股份有限公司副總裁李珂表示,手機和消費電子時代,信息產業一路遵循摩爾定律,形成了一種慣性:簡單粗暴地靠速度、集成度、更高的工藝來解決問題。

而物聯網正在崛起,相比消費網際網路,這個市場所需的晶片用量遠遠大於消費電子,但是對晶片性價比的要求是更高的,主要是對晶片的製程和工藝要求比手機低很多,國際大廠在製程上追趕5nm、3nm,將摩爾定律逼至極限,但這些物聯網的晶片甚至只需要28nm、45nm工藝水平,只是對晶片適配業務、適應場景的能力要求更高。

李珂認為,所謂超越摩爾,比拼的不再是技術上的先進,而是應變能力,比如在同樣的線寬、同樣工藝上實現價值最大化以及能否在不提升工藝的情況下提升性能。

而更重要的一點是,這條路徑需要更龐大的市場和應用,比如大規模城鎮化帶來基礎設施的增長,這在很多歐洲國家是無法做到的,但對中國來說恰恰是一個機遇。

李珂表示,機會就在中國,中國市場是一個超越摩爾定律的絕佳土壤,疫情的爆發和晶片的缺貨,讓全球意識到,中國有著大規模的人臉識別、語音識別的應用,甚至二維碼的應用,背後都需要晶片,但並不需要太高的工藝技術。

來源:快科技

E3 2021:《藥水工藝:鍊金術師模擬器》新預告

今日(6月13日),在Guerrilla Collective Showcase上,中世紀鍊金術師模擬器《藥水工藝:鍊金術師模擬器》 (Potion Craft: Alchemist Simulator)公布了新的預告,本作現已上架Steam,試玩Demo免費下載,正式版預計今年年內登陸Steam。

Steam地址:點我試玩

《藥水工藝:鍊金術師模擬器》新預告:

在《藥水工藝:鍊金術師模擬器》中玩家將成為神秘的鍊金術士,利用工具和草藥研磨製作功能不同的藥水,並與顧客進行交易。發掘神奇新配方,購買種植草藥,進行特殊瓶裝定製,滿足不同顧客需求。

預告截圖:

來源:3DMGAME

晶片巨頭進入3nm競賽:良率與製程到底誰更重要?

五月初,IBM宣布2nm工藝製程取得重大技術突破引發一番熱議,提醒業界5nm處理器已經大規模市場化,晶片巨頭們也已進入下一輪製程競賽:三星披露其即將推出的3nm工藝將基於下一代電晶體類型全柵極(GAA)FET,台積電也計劃將FinFET擴展到3nm,然後到2024年左右遷移到2nm的納米片FET。

一直以來,晶片巨頭都將先進位程作為競爭的目標,一方面是將摩爾定律奉為圭臬,力爭做到功耗、性能和面積(PPA)的平衡,另一方面隨著節點命名規則的混淆,先進位程逐漸演變為廠商的營銷策略。但更先進的製程長期以來代表著技術的領先性,以及更高的性能和更低的功耗,因此格外受到外界關注。

事實上,先進位程對晶片巨頭而言固然重要,但並非唯一重要的評判標準,正如IBM 2nm距離真正量產還需大約兩年時間,與先進位程的研發同等重要的,還有晶片良率。

1%的良率意味1.5億美元淨利潤,晶片順利量產的必經之路

一般而言,新節點誕生的完整過程,需要經過前期研發和後期工廠驗證,在風險試產的過程中逐漸提升良率,達到一定標準後才能正式量產,進入市場。

「通常而言良率要達到85%以上才能順利量產,低良率不僅意味著虧損,也代表劣質低效,即便是最終被應用了,也可能出現異常,會給使用者帶來不好的體驗,所以良率是一個非常嚴肅的問題。」聚焦晶圓製造良率問題的中國企業眾壹雲的創始人之一、戰略咨詢專家李海俊告訴雷鋒網。

不過,85%的良率並不是一個標準的參考線。半導體行業資深人士陳一(化名)向雷鋒表示,工廠一般有大致達標的良率供參考,對於一定達到什麼數值才能算真正進入量產,每個公司認定標準不同,除了良率,還要看良率的一致性。

專注幫助晶片設計公司以及晶圓製造廠改善良率的普迪飛半導體公司資深技術總監王健也向雷鋒網(公眾號:雷鋒網)表示,不同的公司、不同的產品與設計不盡相同,沒有放之四海而皆準的統一標準。「一般而言,手機等消費級產品量大,良率更高,汽車、航空等晶片產品其類製造流程中會做一些特定的改進,復雜的製造流程加上更加嚴格的指標和要求,導致其最終良率會比消費類低,售價也相應高一些。」王健補充到。

需要注意的是,雖然較低的晶片良率有可能會影響到最終的成品情況,但晶片良率與產品合格率有所區別。「晶片製造過程中會引入各種各樣的不確定因素,流程缺陷、環境中的顆粒物、工藝的波動,最終生產出來的產品會有一些不確定性,最終的產品不滿足這些指標就沒辦法正常交付,正常產品的占比就是良率。」王健說。

陳一對產品合格率加以解釋,「我所理解的產品合格率,是一個質量概念,即賣出去的良品失效的比例,這是對封裝工廠的重要考核指標,主要取決於工廠的技術和管理水平。」

也就是說,如果按晶片製造流程來分,晶片設計和製造決定良率,封裝測試決定產品最終的合格率。雷鋒網了解到,晶片總良率是wafer良率、Die良率和封測良率的總乘積,影響晶片良率的因素復雜多樣,一般而言設計越復雜、工藝步驟越多、製程偏移率越大,晶片良率越低,此外,環境污染也會對良率造成一定的影響。

對於晶片企業來說,晶片良率直接反應了所投放的晶片里可出售比例,因此也直接影響晶片製造成本。「從評估整個成本的角度來講,良率是一個非常重要的指標,直接來說,良率直接影響到最終的實際成本,良率越高,最終實際分攤到每一顆正常晶片上的成本就越低。」王健說。

良率對晶片成本的影響,圖片源自伯克利大學論文

此前半導體材料廠商Entegris(應特格)執行副總裁及營運長Todd Edlund曾在接受媒體采訪時表示,對於3D NAND晶圓廠而言,1%的良率提高可能意味著每年1.1億美元的淨利潤;而對於尖端的邏輯晶圓廠而言,1%的良率提升意味著1.5億美元的淨利潤。

比研發先進位程更實際有效,摩爾定律的另一種延續

之所以說提升晶片良率與製程開發同等重要,除了提升良率是晶片從實驗室階段到量產的必經之路以及晶片良率與整體成本密切相關之外,從經濟角度上講,提升晶片良率可以視為摩爾定律的另一種延續。

摩爾定律最早由英特爾創始人之一戈登摩爾在1965年提出,集成電路上可容納的電晶體的數目每隔兩年便會增加一倍。之後在眾多專業人士的集思廣益下得以延伸,兩年縮短為18個月,電晶體數目的增加一倍也意味著微處理器性能提升一倍或價格下降一半。雖然一直以來被業界奉為圭臬,但追根到底,摩爾定律並非自然科學定律,而是摩爾的經驗之談,是集成電路領域的經濟定律。

「摩爾定律具有高度抽象性,包含一些經濟成本方面的考慮,整個業界不同的階段也都會去做一些成本的核算和控制,每個細分環節和領域都會有類似的評估以及一些指導性工作。」王健說。

正在推動摩爾定律向前發展的,實際上是用更低的成本做出更好的產品。摩爾定律發展至今,無論是技術上還是資本上都已經舉步維艱,IBS的數據顯示,開發3nm晶片設計成本高達5.9億美元,5nm器件的成本達4.16億美元。因此衍生出超越摩爾定律(More than Moore),不再只局限於電晶體微縮,更優化的電路設計、系統算法以及異構集成都被納入其中。按照這一邏輯,在非最先進位程上進一步提升晶片良率也可以被視為摩爾定律的延伸。

2005年,ITRS首次引入「More than Moore」(MtM)和「More Moore」(MM),圖片源自IEEEE IRDS社區

王健告訴雷鋒網,傳統上業界習慣用PPA的方式去評估晶片設計上做出的一些決定,但大概在近20年左右的時間里,大家開始發現PPA無法非常全面地衡量晶片設計上一些決定以及最終對產品的影響,隨之加入了一些其他標準,包括成本(C)、產品導入市場的時間(T),以及產品的可靠性(R),這些標準與良率直接相關。

值得注意的是,將其視為摩爾定律延伸的前提是:晶片良率多少並不直接決定晶圓廠是否進入到下一代工藝的研發。「新工藝的開發不是建立在前一工藝良率穩定的基礎上,研發團隊一直在挑戰製程極限,」陳一說到。這也就是為什麼晶片大廠在公布技術路線圖時,往往出現同時研發多個工藝節點的情況。

如果進一步比較提升晶片良率與研發下一代製程哪一種路徑性價比更高,李海俊認為前者更加實際有效,「除了手機電腦晶片,大部分智能應用場景所需的晶片可能連28nm的工藝都用不到,從性價比看根本不需要5nm以下的晶片,也就不需要花費動輒上億美金開發先進位程,還有可能花了很多錢之後,做出來的機率依然很低,這是一個聽起來讓人絕望的怪路徑,所以提高晶片良率更為實際有效,目前大部分學者也贊同這一方向,認為其符合內循環的政策引導。」

既然研發先進位程從經濟上講怪路徑,為何晶片巨頭們還在咬牙堅持,李海俊進一步解釋,「站在產業鏈發展和國家利益來說,先進位程研發的步伐一刻不能停,半導體是贏家通吃的局面,落後只有死路一條。這事關市場和地位爭奪、國家安全和民生安全,雖然是充滿挑戰的怪路徑,但催人振奮。」

一場晶片廠商終身的自我較量

如果將先進位程的研發視為晶片巨頭們之間的競爭,那麼提高晶片良率則可以視為晶片廠商的自我競賽,一方面是因為良率作為晶片廠商的最高機密數據十分敏感,不會像公布工藝節點那樣公布自家真實良率情況,另一方面是影響良率的因素眾多,很難有一個准確的數值與競爭對手進行比較,而晶片廠商始終致力於能夠在短時間內就向客戶交付安全正常的晶片,提升良率需要爭分奪秒。

「對晶片設計公司而言,如何更加高效地提升產品良率,如何把經驗傳承到下一代產品設計中去是需要思考的問題,對於晶片製造公司而言,如何更快地完成工藝研發使得能夠更早地引入客戶,以及如何幫助客戶更快地提升良率是需要思考的問題,」王健告訴雷鋒網。

隨著半導體行業逐漸發生變化,尤其是從IDM向Fabless、Foundry等經營模式延伸,業界提升晶片良率所面臨的難題及措施都在相應地發生改變。

「晶片的良率取決於兩個因素,一是產品對工藝的需求和工藝能夠滿足兩者之間的匹配度,而是產品工程師和產線工藝工程師的溝通是否到位。」陳一說到。

也就是說,作為晶片公司的自我較量,晶片良率需要晶片設計公司和晶片製造公司的緊密配合和有效溝通才能得以最終保障。這一溝通與配合在IDM時代實現更容易,在Fabless、Foundry盛行的今天卻面臨一些難題。

「很重要的一個問題是隨著整個工藝集成越來越復雜之後,最終產品良率會受到設計和工藝的交互影響,如果單純從製造端的角度或方式來分析良率,很難完全分析整個良率當前所遇到的問題根源。」王健表示。

尤其是在工藝研發階段,晶片公司無法窮盡所有版圖圖形組合做完整的評估,而在設計公司提交的設計中,某些特定的圖形組合將觸發特定的問題,這需要用借用第三方大數據平台分析。

也正因如此,在半導體產業近10年至20年的發展過程中,逐漸誕生了類似普迪飛、眾壹雲等幫助晶片設計公司和晶片製造公司更加高效合作以提升晶片良率的公司,作為產業鏈中一個新環節出現,為半導體公司提供大數據分析平台,或提供面向缺陷和良率管理的套件組合。

在幫助晶片廠商改善良率的過程中,這一「新環節」上的公司前期主要關注整個良率的評估,將良率水平的差距分解到具體的工藝或設計上,同設計廠或製造廠共同合作在短時間內改善良率,當良率達到理想水平後,便將注意力更多地放在維持量產監控以及預防上。

提升良率,作為晶片廠商的一場自我較量,雖然很難以具體的數值占比來評估其重要性,但它貫穿產業鏈的上下游,貫穿一顆晶片的生命周期,業界普遍將其視為晶片製造的終極挑戰,是晶片廠商自始至終都需要面臨的問題。

「晶片良率問題,直接對應的是工藝、設備、材料的問題,在這之後是管理的問題、商業模式的問題,人才的問題、開放式創新的問題。」李海俊說到。

來源:快科技

Marvell推出100G PAM4 I/O的1.6T乙太網PHY解決方案,採用5nm工藝製造

Marvell(美滿電子科技)推出了業界首款採用5nm工藝的1.6T乙太網PHY解決方案,支持100G的PAM4輸入/輸出(I/O)。Marvell表示,數據中心需要進一步增加帶寬以滿足海量數據增長的需求,這也推動了乙太網骨幹網絡向1.6T過渡,而100G串行I/O可以在雲服務基礎架構中發揮關鍵作用,為人工智慧、機器學習、雲端等工作負載帶來可擴展性。

650 Group創始人兼技術分析師Alan Weckel表示,100G串行電信號非常重要,因為這將是下一代高速網絡奠定的基礎。隨著I/O速率的提高,信號完整性方面往往會面臨挑戰。Marvell的1.6T乙太網PHY解決方案(Alaska 88X93160)支持用於高密度交換機的下一代100G串行400G和800G乙太網連接,為了解決傳輸速率翻倍對信號完整性可能造成的問題,其採用了對沖定時器,滿足交換機配置多埠的需求。

這也是業界首款完全符合IEEE 802.3ck 100G串行I/O標準和乙太網技術聯盟800GbE規范的PHY設備。同時支持Gearboxing功能,可讓數據中心獲得100G串行I/O的交換機ASIC的全部帶寬,並保持與現有50G的PAM4 I/O相兼容,同時功耗將下降40%。

隨著新一代產品的推出,Marvell將保持在高速重定時器及調速領域的領先位置,提供了從10GbE到800GbE的不同產品組合,並支持MACsec加密/符合C類標準的IEEE1588 PTP時間戳。目前Marvell已開始向部分客戶提供1.6T乙太網PHY解決方案的相關樣品。 ...

Marvell全球首發160萬兆乙太網PHY方案:5nm工藝

你的寬帶網速有多少?萬兆?可能很多人想像不到,在數據中心領域,骨幹網的速度已經達到了何種程度。

今天,美滿電子(Marvell)宣布推出全球第一款1.6T乙太網PHY(物理層)解決方案,相當於160萬兆,支持100G(10萬兆)速度的PAM4點起輸入輸出,並使用了先進的5nm製造工藝。

該方案產品型號「Alaska 88X93160」,可以在乙太網骨幹網上實現1.6Tbps的超高速傳輸,也就是每秒200GB,五部藍光電影一秒鍾就可以搞定。

有了它,就可以在高密度交換機上實現做到基於100G串行的400G(40萬兆)、800G(80萬兆)的乙太網連接。

當然,翻倍的傳輸速率也對信號完整性提出了嚴峻挑戰,為此美滿電子使用了對沖定時器,滿足多埠交換機的需求。

它還是全球首個完全滿足IEEE 802.3ck 100G串行I/O標準、乙太網技術聯盟800GbE標準的PHY設備,支持Gearboxing功能,可讓數據中心運營商獲得100G串行I/O的交換機ASIC的全部帶寬。

另外,由於採用了最新的5n工藝,800GbE PHY方案的輸入輸出功耗,比現在的50G PAM4方案低了足足40%。

美滿電子已經向部分客戶提供1.6T乙太網PHY的樣品。

來源:快科技

Intel 5nm工藝曝光 效能竟不弱於台積電2nm

在先進半導體工藝上,Intel目前最新的是10nm工藝,已經落後於台積電、三星。新上任的CEO基辛格決心用幾年時間重新超越,未來幾年將會投入200億美元建設先進工藝晶圓廠。

Intel下一個目標是7nm工藝,這幾天的台北電腦展上,基辛格稱司已經完成7nm Meteor Lake晶片的「Tape-in」。Tape-in在Tape-Out(流片)前,大概是IP模塊完成設計驗證階段。

Meteor Lake(流星湖)是Intel第一代7nm客戶端處理器,計劃2023年開始出貨,7nm數據中心處理器Granite Rapids也會在同年交付。

再往下就是5nm工藝了,Intel官方是沒有給出什麼明確信息,不過有投行分析師透露了5nm工藝的水平,電晶體密度大約在400MTr/mm2,也就是每平方毫米4億電晶體,差不多是Intel 10nm工藝的4倍了。

對比其他廠商呢?專家指出台積電的2nm工藝的電晶體密度也就是500MTr/mm2,5億電晶體每平方毫米,雙方的密度差距只有20%左右,Intel 5nm效能與台積電2nm差不多。

但是台積電的優勢是在成本上,而且量產的時間也會更早,畢竟2nm工廠已經取得土地,Intel這邊7nm工廠還在建設中,5nm量產還早。

來源:遊民星空

弗勞恩霍夫研究所介紹可清潔自毀的融酶塑料製造工藝

過去幾年,德國弗勞恩霍夫研究所(Fraunhofer Institute)的科學家們一直在研究面向未來的新型塑料,並且開始取得了一些激動人心的新進展。通過在塑料中嵌入一種活性酶,這些塑料不僅能夠用於外賣包裝 / 飲料吸管,還能夠被賦予不同的功能 —— 比如分解表面蛋白質或自我降解,以避免造成環境污染。

弗勞恩霍夫展示薄膜 / 顆粒形式的雙功能塑料(來自:Fraunhofer IAP)

這項工作是在弗勞恩霍夫應用聚合物研究所進行的,那里的科學家們一直致力於解決圍繞酶和塑料的復雜工程問題。

研究難點在於酶難以承受塑料製造過程中的高溫,但弗勞恩霍夫團隊似乎找到了更好的解決方案。

Ruben R. Rosencrantz 博士解釋稱,他們在無機載體的幫助下將酶添加到了熱塑料熔體中,前者能夠保護活性酶免受過大的力和極端溫度的影響。

通過使用高度多孔的無機顆粒,活性酶就能夠在此過程中嵌合於其中。盡管這限制了酶的流動性,但至少能夠讓它們保持活性、並且能夠承受更高的溫度。

具有生物活性的塑料酶的活性測定(圖自:Fraunhofer IAP)

此前已有許多科學家為「雙功能塑料」搭配過蛋白酶,並且製成了顆粒和薄膜製品。這些酶能夠分解其它蛋白質,從而為製造具有自清潔特性的塑料鋪平了道路,比如不易堵塞的管道。

科學家們正在探索的另一種特性,就是能夠快速降解的塑料,以解決普通塑料需要幾個世紀才能在自然環境中被徹底降解的難題。此外弗勞恩霍夫研究團隊還暢想了更多可能,比如打造具有防霉表面的材料。

畢竟作為一種並非「一刀切」的方法,他們還可以對無機載體和嵌入流程進行相應的調整,以適應不同的酶,從而催生更環保的材料形式。

團隊成員 Thomas Büsse 表示 —— 我們開發出了一種既適用於生物塑料、也適合基於傳統石油基塑料(比如聚乙烯)的新工藝。

研究還表明,一旦將之嵌入塑料,就能夠保持酶活性的穩定、以及讓它承受較以往更高的熱負荷等壓力,從而讓融酶塑料的使用和所有工藝步驟都變得更加輕松。

【相關新聞】早些時候,加州大學伯克利分校的科學家們也在一篇文章中介紹過類似的研究。通過在塑料中嵌入酶。並在條件觸發時迅速分解材料。

來源:cnBeta

科學家開發新回收工藝 從廢棄地毯中提取「原始標準」的聚丙烯

廢棄的地毯不可避免地在垃圾填埋場占用大量空間,或在焚燒時產生大量的煙霧。但是,研究人員很快就有可能從合成地毯中回收高等級的聚丙烯。作為歐盟ISOPREP項目的一部分,德國弗勞恩霍夫研究院建築物理研究所的科學家正在開發這種新的回收工藝。

研究人員首先是對廢棄的地毯進行清洗,這涉及到盡可能多地去除底層。然後,剩餘的材料被切碎,與一種專有的離子液體溶劑混合,並置於一個反應室中。在該反應器中,聚丙烯從地毯纖維中溶解出來,進入溶劑中,留下染料等雜質。

在隨後的步驟中,聚丙烯從溶劑中分離出來,其中大部分可以重新使用。收獲的聚丙烯被描述為「原始標準」,這意味著它可以用於生產高質量的產品--相比之下,許多回收的塑料只能用於低質量的產品。

科學家們現在正致力於最大限度地提高可重復使用的溶劑數量(因為它相當昂貴),並將能源需求和溫室氣體排放保持在最低水平。"弗勞恩霍夫研究院研究員Maike Illner說:「如果損失率能夠保持在1%或更低,那麼該工藝的成本就有可能與生產新聚丙烯的成本相媲美。」

研究人員計劃在一個試驗工廠中試用該工藝,該工廠將於明年3月開始每天回收1噸的地毯廢料。可以想像,這項技術也可以應用於其他類型的含聚丙烯的廢物。

來源:cnBeta

台積電3nm工藝工廠進展順利 將在三季度開始風險試產

5月26日消息,據媒體報導,在5nm製程工藝大規模量產超過1年後,晶片代工商台積電更先進的3nm工藝的量產事宜,也就成了關注的焦點。

媒體最新的報導顯示,台積電將採用3nm製程工藝代工晶片的新工廠,建設進展順利,並未受到影響。

媒體在報導中還提到,台積電的3nm製程工藝,在三季度就將開始風險試產,這符合台積電CEO魏哲家此前在財報分析師電話會議上透露的量產時間。

在最近幾個季度的財報分析師電話會議上,魏哲家均透露3nm工藝將在今年下半年風險試產。

在最近幾次的財報分析師電話會議上,魏哲家還透露,他們3nm製程工藝的研發,在按計劃推進。

同5nm工藝相比,3nm工藝將使電晶體的理論密度提升70%,性能提升15%,能耗降低30%。

按台積電方面的計劃,他們的3nm製程工藝,將在2022年大規模量產。

台積電3nm晶片工廠的建設,在2017年就已開始謀劃,當時創始人張忠謀還未退休。他在當年10月份的一次采訪中透露,保守估計,3nm工廠的建設將花費150億美元,可能達到200億美元。

來源:快科技

歐盟重申半導體 拿下全球20%份額、量產2nm工藝

全球晶片危機遲遲不見緩解,甚至有惡化的趨勢,歐洲汽車行業受到的沖擊也越來越大。這讓歐盟深刻地意識到,過於依賴美國、韓國等國家和地區的晶片行業,難以保證供應鏈安全。

當地時間周四,歐盟內部市場專員Thierry Breton再次強調,歐盟計劃投入大量資金發展歐洲半導體製造業,以完善其晶片供應鏈。

Breton表示,歐洲需要擴大產能製造中等水平的晶片,才能實現到2030年半導體市場份額增加一倍的目標。

根據歐盟的規劃,屆時歐盟半導體市場份額將占據全球總量的20%,同時還將有能力生產最先進的2納米晶片。

據悉,歐盟正考慮建立一個半導體聯盟,目前有意向加入的包括ASML、恩智浦、STM和英飛凌等歐洲半導體公司。

由於歐洲半導體行業和頂級晶片製造商還有差距,Breton希望能引進國際三大晶片製造商之一(台積電、三星和英特爾),在歐洲建立一個先進的工廠。Breton表示,資金可能來自於歐盟正在推進的幾個項目,例如8000億歐元的新冠復蘇基金,該計劃20%的資金將用於歐洲大陸的數字轉型。

Breton稱,歐盟希望為晶片製造商提供機會,讓他們能夠在歐洲大陸投資,加強供應鏈安全。Breton還表示,希望能盡快在幾個月內採取行動。

ASML總裁Peter Wennink是Breton計劃的支持者,在他看來,歐洲現在開始扶持汽車晶片和邊緣計算等行業是明智的行為,這些領域在5年內非常重要,而歐洲公司在這些領域已經初具優勢。

來源:遊民星空