Tag: 5nm

台積電第三季度財報顯示,預計2021年5nm製程收入將占總收入的20%

隨著蘋果A14處理器的發布,5nm工藝算是真正與消費者見面了,這款採用TSMC 5nm工藝,集成了118億電晶體。的手機處理器,集成了118億電晶體。並且在桌面端上,AMD也表示其之後的Zen 4處理器也將升級5nm工藝,電晶體密度會比現在的7nm工藝提升80%,整體性能會提升15%。

在台積電(TSMC)第三季度財報中,有關5nm製程將如何影響台積電財務的細節浮出水面。從長遠來看,台積電預計5nm將是一個「長而大」的節點,這意味著它將大量銷售並且在很長一段時間內仍是其代工業務的關鍵。

台積電本季度預計5納米製程僅占收入的8%,預計到2021年,它將占到20%左右,盡管台積電(TSMC)執行長還不想表示確切的預測。

台積電預計5nm工藝的絕大部分將用於高性能計算和5G移動設備,這並不奇怪,因為預計蘋果將成為其移動設備晶片製造的第一大客戶,同時,AMD的5nm Zen 4架構晶片也有望在2022年投放市場,盡管目前尚不確定,但它們很有可能將基於台積電的5nm工藝。

從長遠來看,台積電的目標是實現生產毛利率的50%,但是,來年5nm節點將使這一數字減少2-3%,同時不利的匯率也使這一數字有所下降。 ...

台積電5nm代工價曝光 一片晶圓比7nm幾乎貴了一倍

隨着蘋果A14處理器的推出,台積電的5nm產線已經滿載,正馬不停蹄地趕工中,畢竟除了iPad Air 4,後續還有iPhone 12系列,年底前甚至還有5nm Apple Silicon(A14X?)。

下面來探討一個趣味問題,找台積電代工5nm,需要多少錢?

半導體業內人士chiakokhua在最新Blog網誌中,以一顆類似NVIDIA P100規模的芯片(面積610mm2、907億顆晶體管)為參照,匯總了它在台積電工藝節點下的晶圓和芯片銷售價格。

簡單來說,5nm晶圓單片的代工銷售價約是16988美元,對比7nm,漲幅超80%。

當然,因為晶體管密度大增,同是300mm(12寸)晶圓能切割出來的芯片增多,故換算到單顆芯片的代工價,其實只有238美元,比7nm的233美元只貴了5美元。

考慮到5nm用於商業宣傳上的利好效應、15%的性能提升、30%的功耗下降,這5美元感覺還挺超值。

5nm晶圓之所以貴,主要是工藝復雜,EUV多達14層,每一層都要動用ASML的Twinscan NXE光刻機,這台設備單價超1.2億美元。

另外,目前是5nm大規模量產的初期,良率在逐漸拉升,後期成本會慢慢降下來。

比較極端的例子是,90nm的晶圓可是只要1650美元,可真要做907億顆晶體管規模的芯片,單價需要2433美元。

作者:萬南來源:快科技

取代Intel蘋果自研Mac處理器四季度啟動量產 台積電5nm代工

年底前重要的蘋果產品,除了iPhone 12系列、Apple Watch Series 6、iPad Air 4、AirTags、AirPower等,還有基於Apple Silicon的新Mac電腦。

來自Digitimes的最新消息稱,蘋果已經通知台積電於四季度啟動Apple Silicon的量產工作,月產能5000~6000片晶圓,基於5nm工藝。

早先有消息稱,Apple Silicon首發芯片就是A14X,除了iPad Pro要用,新Mac也是。

據稱,A14X研發代號Tonga,年底前用在12寸MacBook上,作為中央處理器,替代Intel x86方案。

前不久有爆料稱,12寸MacBook採用視網膜屏幕、重量小於1公斤、續航時間可達15~20小時。

更早些時候傳出,A14X可能設計為12核,至少配置4顆性能核心,實力非常可觀。

當然,取代Intel x86要做的不僅僅是紙面性能,還有實際應用表現,包括如何建立起來圍繞ARM架構的桌面PC形態。此前,微軟曾聯合高通在Windows陣營上做嘗試(ACPC全時連接電腦),可雷聲大雨點小,市場反應並不強烈,生態掌控力更強的蘋果會成功嗎?不妨拭目以待。

作者:萬南來源:快科技

7nm安培繼任者定了 NVIDIA確認正在開發Hopper顯卡 5nm?

9月2日,NVIDIA應該會正式推出安培GPU架構的RTX 30系列遊戲卡了,RTX 3090上位成為新旗艦,價格殺奔13999元。

NVIDIA今年5月份以在線GTC大會的形勢發布了Ampere安培GPU架構,7nm工藝、540億晶體管、826mm2面積,40GB HBM2顯存、6912個CUDA核心,各方面規格都是頂級水平的。

不過這是安培是面向數據中心市場的,遊戲卡的安培GPU可能有所不同,目前連製造工藝都沒有靠譜說法,可能是台積電7nm,也有可能是三星8nm LPP,或者兩者兼而有之。

對NVIDIA來說,不論是7nm還是8nm工藝,安培GPU只剩下最後的市場階段了,技術上已經完結,所以他們早就開始尋找下一個目標了。

NVIDIA CFO Colette Kress日前在參加BMO虛擬技術大會時透露,NVIDIA已經開始研發未來的GPU架構了,其中就有Hopper GPU。

,但是NVIDIA首次證實安培繼任者的GPU代號,指的應該是Cobol語言之母、發明世界上第一個編譯器的Grace Hopper(格蕾絲·赫柏)。

現在談論Hopper GPU的具體規格還早,不過它面向的製造工藝應該是下個節點——5nm,不確定是三星或者台積電誰能代工,但是Colette Kress表示NVIDIA的產品會在兩家代工廠之間做最佳劃分。

不過變化依然很多,考慮到NVIDIA近年來在製程工藝上一直比較保守,採用7nm工藝的改良版工藝6nm也不是沒可能。

作者:憲瑞來源:快科技

麒麟9000即將絕版 台積電5nm產能不降反增 增產70%

隨着9月15日最終期限的臨近,華為的麒麟9000處理器也即將絕版,目前台積電正在開足馬力生產,

華為是僅次於蘋果的台積電第二大客戶,去年的營收占比高達14%,今年也是5nm工藝的兩大客戶之一,損失華為對台積電來說很可惜。

不過台積電的5nm工藝也不會因此無人問津,相反華為之外的客戶現在反而多了機會,高通也從三星5nm轉單台積電,AMD的5nm芯片也加速了,聯發科、NXP等客戶也開始轉向5nm工藝。

以致於台積電現在5nm產能不夠用了,目前還在不斷擴充5nm產能,目前的產能是6萬片晶圓/月,南科工業園的Fab 18工廠P3工程將於Q4季度量產,明年Q2季度P4工程還會進一步增加產能約1.7萬片晶圓/月。

隨着這些工廠的擴產,台積電的5nm產能將從目的6萬片晶圓/月提升到接近11萬片晶圓/月,增幅超過70%,不僅是全球最大5nm產能,還拉大了與三星等對手的差距。

作者:憲瑞來源:快科技

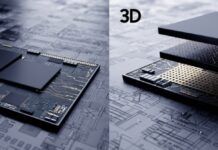

芯片搭積木 三星官宣X-Cube 3D封裝技術 可用於7/5nm工藝

在Intel、台積電各自推出自家的3D芯片封裝技術之後,三星也宣布新一代3D芯片技術——X-Cube,基於TSV硅穿孔技術,可以將不同芯片搭積木一樣堆疊起來,目前已經可以用於7nm及5nm工藝。

關於3D芯片封裝,了解半導體芯片技術的玩家應該不陌生了,現有的芯片都是2D平面堆疊的,隨着芯片數量的增多,占用的面積越來越大,不利於提高集成度。

3D封裝顧名思義,就是將芯片從平面堆疊變成了垂直堆疊,類似搭積木那樣一層層疊加,減少了芯片面積,提高了集成度。

台積電、Intel之前都公布了3D封裝技術,技術風向大同小異,具體的實現方法不同,,已經在Lakefield芯片上應用,集成了10nm CPU、22nm IO核心。

三星自家的3D封裝技術叫做X-Cube,基於TSV硅穿孔技術將不同芯片堆疊,已經可以將SRAM芯片堆疊到芯片上方,釋放了占用空間,可以堆棧更多記憶體芯片。

此外,TSV技術還可以大幅縮短芯片之間的信號距離,提高了數據傳輸速度,降低了功耗,並且客戶還可以按需定製記憶體帶寬及密度。

目前三星的X-Cube技術已經可以用於7nm及5nm工藝,三星將繼續與全球無經驗半導體公司合作,將該技術部署在新一代高性能芯片中。

作者:憲瑞來源:快科技

台積電將因5nm訂單使今年第三季度業績創新高,預計可達112億美元至115億美元

近日台積電宣布,其2020年7月份的銷售額同比增長25%,環比下降12%,至新台幣105.9億元。至此,台積電2020年7個月的累計銷售額同比增長33.6%,至新台幣7272.2億元。其CFO黃仁昭表示:「在5G智慧型手機,高性能計算和物聯網相關應用的推動下,對台積電5nm和7nm技術的強勁需求有望推動第三季度的銷售。」

該公司預測,2020年第三季度的銷售額將在112億美元至115億美元之間,這可能會創下歷史新高。該公司還在8月11日舉行的董事會會議上批准了52.716億美元的資本支出。將投資建設新的晶圓廠,安裝設備,引進新技術以及研發設備。

長期以來,由於英特爾和三星電子在EUV光刻技術方面相對停滯,並且長期以來產量一直低迷,自近些年半導體行業興起以來,大部分注意力一直集中在台積電的5納米工藝上。

截至2020年8月,台積電的5nm EUV生產線幾乎已滿負荷生產,可用於蘋果下一代iPhone處理器A14 Bionic SoC和華為智能手機處理器SoC麒麟1000。但是,由於美國方面的原因,9月11日之後將無法向華為發貨,因此仍有空間可以接受其他公司的製造合同。據報告,台積電將5nm產能給了以下八個客戶:

Apple(用於iPhone和iPad的A14 Bionic和A14+ Bionic處理器,用於Mac Book的CPU「 Apple Silicon」等)

英特爾(GPU和CPU,據報導正在協商中)

Altera(現在為Intel,FPGA SoC)

高通(Snapdragon 5G AP,數據機等)

AMD(GPU,CPU)

英偉達(GPU)

聯發科技(Dimensity 5G AP,數據機等)

比特大陸(比特幣挖礦晶片)

應該注意的是,由於Altera已被Intel收購,並且已經是該公司的業務部門,因此實際上應該是7家公司。在被英特爾收購之前,Altera一直將製造業務外包給台積電,並建立了友好的關系。 ...

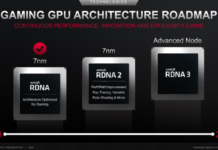

走Zen2的老路 AMD下下代GPU架構RDNA3或用小芯片設計

從去年7月份開始,AMD的GPU開始全面轉向7nm RDNA架構,現在的Radeon 5000系列是第一代RDNA架構,今年還有big Navi/Navi 2X系列,會使用7nm+工藝的RDNA2架構,能效再次提升50%。

今年的顯卡旗艦big Naiv據悉最多有80組CU單元,也就是5120顆流處理器,比RX 5700多出122%,此前泄漏顯示其性能比RTX 2080 Ti會高出40-50%,。

再往後呢?AMD之前公布的路線圖顯示RDNA2之後是RDNA3架構GPU,但是除了代號之外,AMD不願意提及詳細情況,Zen3之後的Zen4 CPU都明確是5nm工藝了,可RDNA3隻用「高級節點」來代替。

為什麼官方這麼遮掩?可能是RDNA3進度有點慢,現在都沒確定具體工藝,不過這個說法在台積電5nn明確量產、AMD也確定採用5nm的情況下並不成立。

最新的爆料稱,AMD之所以不明確具體節點,很可能跟RDNA3架構的全新設計有關,那就是它也會採用小芯片的方式,將計算單元與IO單元分離,整個設計類似AMD在7nm Zen2處理器上設計的那樣。

小芯片設計的好處就是靈活,可以像搭積木那樣堆出所需的芯片,RNDNA3這樣設計的話堆CU計算單元就更容易了,方便擴充流處理器單元,比如計算核心就可以用5nm工藝製造,而IO核心很有可能跟Zen2那樣採用12/14nm工藝製造以降低成本。

當然,具體情況現在沒有定論,有關RDNA3的架構目前也只是猜測,只不過從技術趨勢上來說這條路最有可能。

考慮到big Navi顯卡最快也是今年11月份才上市,那RDNA3恐怕一年內都沒希望上市,要等到2022年才有戲了,AMD還有足夠的時間改良、優化RDNA3架構。

作者:憲瑞來源:快科技

128核CPU有戲 AMD Zen4處理器已有樣品問世 5nm工藝、面積80mm2

AMD承諾今年會推出7nm+工藝的Zen3處理器,再往後就是全新的5nm工藝Zen4了,EPYC服務器處理器「熱那亞」會首發Zen4。此前信息顯示Zen4應該會在2022年問世,不過現在可能會提前,AMD現在已經有5nm Zen4的樣品了。

台積電今年就會量產5nm工藝,之前最大的客戶是蘋果和華為,正常是輪不到AMD的,不過最近的情況有變了,,2021年的7nm及5nm產能可達20萬片晶圓,遠超目前的水平。

另一方面,Zen3的進度應該到最後的上市階段了,流片、驗證早就過去了,現在有消息爆料稱5nm Zen4已經有樣品了,意味着流片完成了。

據悉,現在流片的5nm Zen4芯片雖然詳細規格未知,但是核心面積大約為80mm2,比目前的7nm Zen2核心面積74mm2高出10%。

台積電聲稱,5nm工藝相比7nm工藝可提升80%的晶體管密度,這樣算來5nm Zen4核心80mm2下至少可以容納12核、多則16核CPU核心,比目前的Zen2翻倍。

當然,實際上每個芯片內可以做到多少核心還要看AMD的架構設計,理論上存在翻倍的可能,如此一來AMD就可以造出最多128核心256線程的EPYC處理器,主流桌面銳龍提升到32核也不是沒可能。

作者:憲瑞來源:快科技

3nm工藝太燒錢 沒有46億元別來流片

最近幾天,半導體行業出了一件大事,Intel宣布7nm工藝延期,導致公司股價大跌,而AMD及台積電兩家公司股價創造了歷史新高,他們在先進工藝上暫時是領先的。

Intel現在遇到的工藝延期問題有多方面原因,技術、人才、管理上都可以找到一堆理由,但是還有一個因素不容忽視,那就是先進工藝越來越燒錢了。

之前的數據顯示,28nm工藝開發一款芯片的費用不過5130萬美元,16nm工藝就超過1億美元,10nm工藝要1.74億美元,7nm工藝要3億美元。

現在Intel、台積電、三星等公司的競爭已經進入5nm以下節點,設計芯片的費用更是水漲船高,IBS數據顯示5nm工藝要4.36億美元,3nm工藝更是要6.5億美元,換算下來就是46億元。

這還只是芯片設計的費用,也就是從紙面到流片的價格,算上後期的生產,價格還要繼續增長,全球也沒多少公司能承受得起這樣的價格。

與之對應的是,成本數倍甚至數十倍增長的同時,先進工藝帶來的收益越來越小,從7nm升級到5nm,台積電數據顯示同性能下功耗降低了30%,同功耗下性能提升15%,倒是晶體管密度可以大漲80%。

作者:憲瑞來源:快科技

聯發科明年的5nm天璣旗艦晶片或將由三星代工,但三星5nm被曝良率不足

受到5G手機普及以及其他外在因素的影響,聯發科憑借著自己的天璣1000系列以及天璣800系列產品在網友以及手機廠商兩個角度取得了不錯的表現,進入到今年下半年以來,搭載兩個系列處理器的產品也是逐漸多了起來。一定程度上,聯發科推出的處理器產品幫助了5G手機的普及。另一方面,5G手機的普及也幫助了聯發科晶片的出貨。

爆料信息,圖片來自手機晶片達人

根據之前的爆料消息,聯發科將會在明年第二季度推出新的5G旗艦晶片產品,並且會基於5nm製程工藝。對此,消息人士「手機晶片達人」表示,台積電的5nm製程工藝客戶主要有蘋果、海思、AMD以及高通等,而聯發科則是不在台積電的5nm製程客戶名單內。如果聯發科的5nm新品不是由台積電打造,那麼基本上就可以確定是由三星進行代工了。

而關於三星5nm製程工藝方面,目前兩大消息,一是三星會推出基於自家5nm工藝的新ARM處理器,除了手機之外,還有可能推出桌面版本。另一個就是,三星的5納米工藝良品率低下,質量被曝不達標。

受到三星5nm工藝良率不足的影響,由三星代工的5nm驍龍875處理器的發布以及上市時間可能都會受到不小的影響。如果消息屬實的話,那麼這將造成後續一連串的連鎖反應,比如說一票採用驍龍875處理器的安卓旗艦或許會面臨缺貨等狀態。另外,既然高通受到了影響,同樣基於三星5nm製程的聯發科新旗艦晶片必然也將受到影響。 ...

中興再次回應7nm、5nm芯片傳聞 有20年設計經驗 無製造能力

今年6月份,中興宣布旗下的7nm芯片已經量產,5nm也開始導入,被自媒體吹成了華為第二,結果,引發了股民聲討。對於這個問題,中興再次澄清,自己有20多年設計經驗,但沒有製造能力。

盡管過去了一個多月了,不少人對中興7nm、5nm芯片一事依然耿耿於懷,日前在互動易平台上,有股民再次要求中興公司澄清有關7nm、5nm芯片,隨後獲得了中興公司的官方回應。

中興表示,在芯片設計領域,中興通訊專注於通信芯片的設計,並不具備芯片生產製造能力。在專用通信芯片的設計上,公司有20多年的經驗積累,具備從芯片系統架構到後端物理實現的全流程定製設計能力;

中興表示,「在芯片的生產和製造方面,我們依託全球的合作夥伴進行分工生產。」

中興稱,芯片的設計和製造需要全產業鏈通力合作,公司一直和產業鏈各方保持密切合作,打造公司競爭力的核心基石,持續為客戶創造價值。

推薦商品信息

作者:憲瑞來源:快科技

高通驍龍875將由三星代工,但似乎受到製程工藝良率不足的不利影響

高通近兩年在旗艦級別移動SoC上面採用了半代升級的方案,也就是先出一款架構換新的SoC,過半年左右的時間推出它的頻率加強版,然後再於當年年底推出下一代的旗艦SoC,從驍龍855、855 Plus再到865、865 Plus,高通都是這麼走的,所以今年年底,我們很有可能會見到驍龍的下一代旗艦SoC,不出意外的話,型號應該是驍龍875,目前業界消息稱高通將會把該SoC交由三星,使用他們的5nm EUV工藝進行代工。不過昨日又有不利消息傳出,業內人士透露,因為良率並不理想,三星的5nm EUV工藝可能會影響到驍龍875的發布和上市時間。

之前驍龍855和865兩代旗艦SoC,高通都是交給了台積電進行代工。從年初開始,我們看到高通又重新開始和三星合作,採用他們家的工藝來代工新的基帶和SoC等產品,這背後可能有成本因素的推動,也或許有與三星移動業務間合作關系的考量。

不過三星似乎在推進新工藝這件事情上走的並不順利,之前已經有報導稱他們取消掉了4nm工藝的研發計劃,直接跳到3nm,現在又傳出他們在5nm EUV上的良率不高的消息。如果驍龍875因為製程而遭遇滑鐵盧,那麼對三星來說也是不小的打擊。

另外,現在還有消息稱高通已經計劃將驍龍875的下一代,也就是驍龍885重新交給台積電進行代工了。 ...

5nm芯片被炒熱 中興股價暴漲22%又暴跌10% 大股東套現8億

這幾天,中心通訊公司的股價猶如過山車,此前公司高管表態7nm芯片量產,5nm芯片已導入,這個重大利好導致中興股價暴漲了22%,自己只是設計芯片,沒有7nm、5nm芯片的生產製造能力。

中興公司CEO徐子陽在日前的股東大會上也談到了中興的芯片進展,宣稱目前公司7nm芯片已實現規模量產,而5nm芯片將在2021年推出。

徐子陽指出,芯片方面,中興做了前端和後端的設計,但在生產和製造方面,是依託全球合作夥伴分工生產。

中興澄清之後,這兩天中興的股價又開始暴跌,昨天跌了6%,今天跌了4.5%,兩天就跌去了10%,跟風高位買入的股民損失不小。

更耐人尋味的是,中興股價高企的時候,第一大股東中興新在6月22日宣布通過大宗交易方式共計減持公司2036.68萬股A股,交易均價39.44元/股。經計算,中興新此次減持套現金額超8億元。

去年5月到現在,中興新已經多次減持,隨着這次減持,中興新持有的中興通訊股權已經從28.40%減少至當前的23.40%。不僅如此,中興新同時表示不排除在未來12個月內增持或減持公司股份的可能。

特惠商品推薦>>作者:憲瑞來源:快科技

Zen4今年Q3季度流片 AMD明年入局5nm CPU

AMD今晚發布了銳龍3000XT系列新品,這是7nm Zen2的提頻版,7月7日正式開賣,正好是7nm上市一周年的日子。如果不延期的話,今年還會有7nm+工藝的Zen3處理器,也就是銳龍4000桌面版。

一旦Zen3架構處理器上市,AMD的AM4插槽就要完成歷史使命了,未來會有更新的Zen4處理器接任,它確定是5nm工藝的,不過AMD一直沒有明確Zen4處理器什麼時候發布。

根據最新流傳的一個說法,AMD的5nm Zen4處理器可能比想象中的要快,今年Q2季度開始流片(tape out),這是芯片研發製造中的重要一步,能流片說明設計差不多完工了,要開始測試、驗證了。

流片之後,處理器會有幾個月甚至一年的時間,之後准備妥當了才會開始量產、上市,所以今年流片,但不可能看到Zen4處理器上市了。

按照規劃,AMD會在2021年獲得台積電的一部分5nm產能,初期產能在每月3000到5000晶圓之間,相比蘋果每月5萬+的產能,AMD分配到產能很少。

但是隨着華為有可能被美國封禁,如果台積電今年9月份之後無法得到美國的許可,那5nm產能就要重新分配了,屆時AMD獲得的產能會顯著增加。

這麼算的話,AMD最快在2021年開始推出5nm Zen4處理器,但首發的要保證EPYC霄龍處理器,桌面版的銳龍5000系列可能還是要等到2022年才有希望看到。

618特惠活動匯總>>作者:憲瑞來源:快科技

台積電宣布4nm工藝 5nm加強版、2023年量產

台積電、三星這幾年在新工藝方面非常激進,但相比於Intel的「老老實實「,14nm再怎麼優化加強也叫14nm,這兩家就有點跳躍了,某代工藝強化一下就是新一代。

台積電CEO劉德音在今天的股東大會上宣布,台積電將會推出4nm工藝「N4」,是其最先進5nm工藝「N5P」的進一步加強版,預計2023年投入量產。

台積電顯然在重復6nm工藝N6的老套路,它就是最強7nm工藝N7+的升級版,好處是在性能、功耗繼續優化的同時,設計上彼此兼容,客戶可以輕松遷移,以較低的成本獲得更好的芯片,還有新工藝的光環加持。

台積電這種套路是從16nm開始的,當時還嚴格遵從技術標準,但是三星類似的工藝叫做14nm,從紙面上看台積電就落後了,於是把16nm加強升級一下,推出了12nm,從此就一發不可收拾……

根據規劃,台積電將在今年第四季度量產初代5nm,同時已完成3nm工藝的設計工作,預計2021年上半年投入試產,還在加快推進2nm工藝。

作者:上方文Q來源:快科技

AMD爭搶華為先進工藝份額 RDNA3提前用上5nm 可與RTX 4080 Ti一戰?

台積電今年將量產5nm工藝,此前最大的兩個客戶就是蘋果及華為,前者的A14、後者的麒麟1000系列處理器都會使用5nm工藝,千萬級的出貨量也遠超其他客戶,優先度是最高的。

不過現在情況有變,台積電5nm正在拉攏其他客戶,AMD可能因此受益,下下代的RDNA3 GPU也可能會提前用上5nm工藝。

在5nm工藝上,AMD之前明確了Zen4架構會使用5nm工藝,但是他們並沒有公布具體的時間,業界一致認為是在2022年,意味着台積電要過了蘋果、華為等客戶的5nm訂單高峰期之後才能給AMD安排5nm產能。

與CPU相比,AMD的下下代GPU路線圖有更多不確定性,今年推出7nm+工藝的RDNA2架構沒跑,往下是RDNA 3代,也就是Navi 3X家族的,只是AMD之前一直都沒公布RDNA3架構的工藝,只用了「Advanced Node」(高級節點)的模糊說法。

與當初的情況相比,台積電現在的策略要改變了,華為的5nm產能預計不會有之前那麼多了,後面的廠商有望從中受益,AMD除了Zen4 CPU之外,RDNA 3架構的GPU也有可能提前。

目前人們對RDNA3架構的細節還是一無所知,AMD只公布了7nm RDNA2架構相比RDNA提升了50%的能效比,並加入了硬件光追技術支持。

如果RDNA3提前用上了5nm工藝,那麼晶體管密度至少還能提升80%,CU單元預計會大幅增加,可能從目前的RDNA 40組、RNDA2 80提升到120-160組,算力大幅增強,屆時有可能跟NVIDIA的RTX 4080 Ti一戰了。

作者:憲瑞來源:快科技

AMD推遲發布Zen3隻因上馬5nm?別想了 7nm跑不了

AMD今年的CPU布局最近有些看不懂了,7月份要推出改良版的Zen2處理器銳龍3000XT系列,頻率繼續提升。今年還有Zen3處理器,不過前不久又有消息稱Zen3推遲,直接跳過7nm使用5nm工藝。

Zen3使用更先進的5nm工藝消息源於台灣媒體,他們的理由是台積電今年提前量產了第二代5nm+工藝,還在為AMD打造一條專屬5nm工藝。

背後沒說出來的原因其實還有一個,那就是華為被打壓之後,台積電的5nm產能釋放出來了,AMD等廠商有機會提前用上5nm工藝,不用等到2022年了。

不過AMD延期Zen3改用5nm工藝的傳聞可信度並不高,不說時間上的安排,針對7nm打造的Zen3架構也不是說立馬就能切換到5nm工藝上的,這幾乎是重新開發了。

此外,Fudzilla網站也援引信源表示Zen3還是7nm工藝,不會上馬5nm工藝。

目前來看,AMD官方的表態一直沒有變化,一直強調Zen3是基於台積電7nm(實際上是二代的7nm+,但AMD為慎重起見不標那麼詳細,路線圖上寫的還是7nm),今年下半年發布。

作者:憲瑞來源:快科技

AMD五六代銳龍齊曝光 7nm Zen3連用兩代、5nm Zen4再等等

昨日有曝料稱,因為進展太順利,AMD Zen 3架構的第四代銳龍將從7nm工藝升級到5nm+,台積電也在為AMD打造專屬的5nm工藝,只是發布時間要推遲一些。

這就有些顛覆了,當然對於玩家們來說更多的應該還是興奮和期待,不過只隔了一天,又有不同說法傳來。

推特用戶@MebiuW放出一份路線圖聲稱,目前的第三代銳龍3000系列代號Matisse,基於7nm工藝、Zen 2架構,而接下來的第四代銳龍代號Vermeer,架構確實升級到Zen 3,但工藝還是7nm,而且至少工程樣品是加強版的N7P 7nm DUV工藝,並不是N5 5nm。

他指出,台積電5nm、7nm的設計規則並不相通,Zen 3要想更換工藝基本等於要在很大程度上推倒重新設計、流片,代價高昂,不符合正常邏輯。

而接下來的第五代銳龍,代號將是「Warhol「——安迪·沃霍爾,1928-1987年,美國藝術家、作家、搖滾樂作曲、出版商、電影導演與製作人,紐約社交界、藝術界大紅大紫的明星式藝術家,被譽為20世紀藝術界最有名的人物之一,是波普藝術的倡導者和領袖。

按照最新說法,Warhol這一代仍將是7nm工藝、Zen 3架構,繼續支持PCIe 4.0,當然也不會有DDR5記憶體,而作為證據,同時給出的還有一張迅即被刪除的局部路線圖:

嗯我知道大家要說擠牙膏了,感覺Warhol這一代應該是臨時增加的,原因不詳,可能是認為Zen 3架構仍有潛力可挖,再提升一次,也可能是認為短期內Intel不會在技術規格上構成太大威脅,刻意放慢腳步。

再往後的第六代銳龍才是傳說中的5nm工藝,架構也來到Zen 4,代號為「Raphael」——拉斐爾·桑西,1483-1520年,意大利著名畫家,「文藝復興後三傑「中最年輕的一位,代表了文藝復興時期藝術家從事理想美的事業所能達到的巔峰。

有趣的是,剛才路線圖上在Rapheal對應的位置,還能看到「Nav」三個字母,難道是Navi GPU?

至於銳龍路線圖上為何會出現GPU,目前尚無線索,難道到時候銳龍也要全線集成GPU而不僅限於部分APU型號?又或者CPU-GPU之間會有什麼更進一步的協同?

作者:上方文Q來源:快科技

AMD被曝推遲發布Zen3架構第四代銳龍處理器 7nm升級為5nm+

今日傳來台積電將於今年四季度量產5nm+(5nm增強版)的消息,沒想到,更進一步的爆料指出,AMD似乎決定改變第四代銳龍處理器(Vermeer,維米爾)關鍵製程工藝。

AMD早先公布的路線圖顯示,AMD Zen 3家族產品基於7nm工藝打造,明年的Zen 4才會升級到5nm,不過因為進展異常順利,AMD的第四代銳龍將直接升級到5nm+。

這倒是契合此前同一信源的報道,當時線報稱,台積電正為AMD打造專屬的5nm工藝。

不過,這也帶來一個問題,AMD需要推遲第四代銳龍的發布計劃,原來的安排是9、10月份。當然,AMD之前從未明確Zen3的具體時間,只說今年晚些時候,留有操作空間。

有了更先進工藝的加持,Zen3的IPC提升幅度在15~20%以上也並非沒可能,甚至頻率也會摸到更高。

另外,AMD此番加速還有助於增強自己的市場競爭地位,至少繼續保有對Intel在製程方面的明顯優勢。

作者:萬南來源:快科技

Intel回應製程工藝競爭 10nm高性能版今年問世 大力研發5nm

在CPU製程工藝上,Intel今年還在使用14nm工藝,並做到了10核5.3GHz,這個工藝優化水平絕對是世界第一的,其他代工廠在14/16nm節點最高也就做到了4GHz出頭而已。

對於廠商之間的工藝競爭,Intel公司日前在股東大會上也回應了投資者的提問,強調創新一直是Intel的核心,摩爾定律是Intel工作的關鍵部分,Intel擁有全面、完整的路線圖以滿足未來10年的需要。

Intel指出,當前的重點是加速10nm工藝量產,今年中將推出高性能10nm節點,同時致力於7nm工藝的量產,此前Intel提到7nm工藝將在2021年首發,不過首款產品是高性能GPU而非CPU。

再往後,Intel提到他們正在投入大量資源研發5nm工藝,不過Intel沒有提到5nm工藝的量產時間。

Intel強調,未來摩爾定律還會持續,而製程工藝雖然非常關鍵,但重要的不只是性能,還有架構、封裝、記憶體、連接、安全及重要的OneAPI軟件,這也就是Intle的六大支柱技術優勢。

作者:憲瑞來源:快科技

台積電120億美元美國建5nm晶圓廠 專家 成本是最高的

5月13日的報道中台積電還表示美國建廠在考慮中,5月15日台積電就突然宣布在美國投資120億美元建設5nm晶圓廠,出乎所有人的意料。對於台積電遠赴美國建廠,分析師表態稱美國的成本是最高的,毛利率一定會最低。

根據台積電的信息,將在美國亞利桑那州興建和營運一座生產5nm半導體芯片的先進晶圓廠。這個5nm新廠規劃月產能2萬片,2021年動工,2024年左右量產。

美國工廠的總投資120億美元(約851億元),預計將帶來超過1600個高科技專業工作機會,並間接製造上千個半導體行業工作機會。

對於台積電美國建廠,不論是宣布的時機還是建成時間,實際上都非常微妙,2024年落成意味着美國下一任總統任期完了之後才能看到,屆時5nm工藝也不是台積電最先進的技術了,因為台積電的2nm工藝那時候都要量產了。

美國政府施壓台積電去美國建廠已經有段時間了,但是之前台積電一直不肯正面回應,開出了美國建廠的三大條件——符合經濟效應、成本有優勢、人員及供應鏈要完備,總結起來就是台積電擔心美國工廠不能賺錢,至少不能像現在那樣維持超高毛利率。

對於這個問題,半導體行業的分析師也是這樣看的,認為美國建廠成本是最高的,導致台積電美國工廠未來的毛利率一定是最低的。

在半導體晶圓廠建設方面,分析師指大陸建廠是最低成本的,台灣次之,美國最高。

作者:憲瑞來源:快科技

Intel Xe獨顯集齊三種新工藝 高端遊戲卡DG2要上台積電5nm?

22年後的今年,Intel將在i740之後重返高性能GPU市場,要把獨顯業務重新做起來,為此Intel拉攏前AMD RTG主管Raja Koduri打造了Xe架構,通吃計算及遊戲市場。

根據官方的信息,Xe架構的設計極富彈性,一個架構就能滿足從核顯到遊戲卡再到數據中心計算卡等市場,有Xe LP、Xe HP及Xe HPC三種不同的類型。

2020年推出的顯卡代號DG1,今年會使用Intel自家的10nm工藝生產,據悉DG1獨顯擁有96組EU執行單元,一共是768個核心,基礎頻率1GHz,加速頻率1.5GHz,1MB二級緩存以及3GB顯存,TDP為25W。

DG1的性能與GTX950相當,比GTX 1050則差了15%左右,不過它並不針對桌面市場,主要用於筆記本電腦。

還有一個確定的Xe顯卡是Ponte Vecchio,這是針對HPC高性能計算打造的,,2021年首發Intel自家的7nm工藝,還會採用Intel Foveros 3D、EMIB(嵌入式多芯片互連橋接)封裝技術,技術水平很高。

這兩款顯卡之外呢?Intel似乎還少個高端桌面顯卡,DG1已經不可能了,傳聞這個角色是DG2,使用的是Xe HP架構,之前信息顯示它設計了三種EU配置,分別是128個、256個和512個。

按照DG1顯卡96個EU單元、2-3TFLOPS的性能來算,DG2的512 EU版性能可達10-15TFLOPS,達到RTX 2080 Ti的水平。

至於DG2的製造工藝,之前傳聞說是交給台積電的7nm生產,但是最新爆料顯示7nm應該不可能了,等到DG2問世的時候7nm有些落伍了,所以它有可能用上台積電的5nm工藝生產,時間點也會在2021年到2022年之間。

總之,Intel的Xe架構顯卡真的是好事多磨,不說架構有多復雜,光是製造就要橫跨10/7/5nm三代,而且有自產的,也有代工的,讓人感覺有點亂。

作者:憲瑞來源:快科技

NVIDIA GPU今年或是雙胞胎 7nm安培、5nm霍普雙殺

再過10天,NVIDIA CEO黃仁勛就就要發表GTC 2020演講了,這次推出7nm安培(Ampere)架構是板上釘釘了。不過2020年的GTC可能不止於此,NVIDIA還有可能更新GPU路線圖,公布5nm Hopper(霍普)GPU,而它有可能是三星5nm EUV代工的。

在GPU工藝上,之前的泄露信息顯示出了NVIDIA的復雜,安培GPU使用10mm、8nm及7nm工藝的爆料都有,不過目前來看台積電7nm工藝代工的安培GPU還是主力。

但是NVIDIA並不會完全依賴台積電,前幾年就跟三星有GPU代工了,14nm節點就在Pascal顯卡的GTX 1050系列上有合作,在7nm及以下工藝中也會如此。

日前三星宣布Q2季度開始量產基於EUV工藝的5nm LPE工藝,並強調他們的客戶來自處理器及顯卡,而這個GPU客戶可以排除AMD,基本上就是在暗示拿到了NVIDIA的5nm GPU訂單。

最新爆料稱,NVIDIA今年的GPU計劃很龐大,7nm工藝用於安培GPU,但它很有可能主要用於計算卡市場,而5nm工藝則是給下下代架構Hopper(霍普)准備的,這才是面向消費級遊戲卡市場的,那也意味着RTX 3080 Ti要變成5nm工藝了。

如果按照這個路線發展,那麼今年的GPU倒是跟之前的Volta伏打、Turing圖靈差不多,兩代GPU面向的市場不同,使用的工藝、架構也不同,NVIDIA是徹底把遊戲與計算卡市場分開了。

作者:憲瑞來源:快科技

三星電子稱芯片代工業務Q1業績下滑 計劃Q2開始大規模量產5nm產品

4月29日消息,據國外媒體報道,三星電子今日發布了第一季度財報,該公司表示芯片代工業務第一季度業績下滑。

三星電子

三星電子芯片代工業務第一季度收益(earnings)略微下滑,因為中國客戶的高性能計算芯片需求下滑。

三星電子表示,第二季度將加強EUV(極紫外光刻,Extreme Ultra-violet)領導地位,開始大規模量產(mass production)5nm產品。

三星電子還表示,將專注於GAA 3nm製程。GAA即Gate-All-Around,環繞式柵極技術。

在芯片代工業務領域,三星電子目前位列第二。排名第一的是台積電,去年市場占有率達52%。

台積電本月早些時候也提到,5nm製程於2020年上半年開始量產。

關於3nm製程技術,台積電表示,相較於5nm製程技術,3nm製程技術大幅提升晶片密度及降低功耗並維持相同的晶片效能。2019年,台積電的研發着重於基礎製程制定、良率提升、電晶體及導線效能改善以及可靠性評估。台積電表示,今年將持續進行3nm製程技術的全面開發。

台積電還表示,已開始開發領先半導體業界的2nm技術,同時針對2nm以下的技術進行探索性研究。

關於台積電和三星電子之間的競爭,台積電創始人張忠謀曾表示,三星電子是很厲害的對手,目前台積電暫時占優勢,但台積電跟三星的戰爭絕對還沒結束,台積電還沒有贏。

來源:快科技

三星宣布5nm EUV本季度大規模量產 暗示已拿到NV訂單

三星今日在一季度財報中確認,將於今年第二季度,也就是在7月開始之前投入5nm EUV的大規模量產工作。

三星表示,藉此,其將加強在EUV(極紫外光刻)技術領域的領導地位。

同時,三星此次還預告,他們還將專注於3nm GAAFET(環繞柵級場效應晶體管)的開發,也就是放棄華人科學家胡正明教授的FinFET(鰭式場效應晶體管)。

另外,三星提到很重要一點,下半年,其晶圓業務將不再僅僅聚焦於手機芯片,而將更多關注消費計算領域。

外媒謹慎猜測,這是暗示三星拿到了處理器、顯卡等產品的訂單,AMD似乎不太可能,最可能的對象就是NVIDIA了。

關於NVIDIA Ampere(7nm)和Hopper(5nm)代工訂單的歸屬,一直眾說紛紜,不知道在5月14日晚9點的NVIDIA GTC上,老黃會否給出最終答案。

作者:萬南來源:快科技

據報導,NVIDIA可能在秘密研發使用5nm製程的晶片

據DigiTimes報導,台積電方面最近可能收到了來自NVIDIA和AMD的大量訂單,涉及到新老產品,並足以讓他們在疫情沖擊之下保持原有的利潤水平。報導中的另一個關鍵信息是,NVIDIA將會使用台積電的5nm工藝。

NVIDIA的下一代GPU,也就是即將要發布的Ampere GPU用的不會是台積電的5nm工藝,這點是相當明確的,所以NVIDIA只能是在開發一些神秘的新晶片。這也是相當正常的事情,畢竟隨著台積電將5nm工藝推向大規模量產化,它要和其他幾家主要半導體設計公司一樣,基於新工藝開發點新晶片,准備面向未來的應用。另外根據此前的報導,台積電的CoWoS封裝工藝也是接近滿載,NVIDIA是這項工藝的老客戶了,具體產品有如Tesla加速卡這樣需要超高顯存帶寬的設備。而正巧,台積電在前不久宣布了新一代2x封裝面積的CoWoS封裝工藝,其中就有對新一代5nm製程的支持,很有可能NVIDIA就是在利用5nm製程和CoWoS封裝工藝開發新的神秘晶片。

NVIDIA最近向台積電下的訂單中包括有16nm、12nm和7nm的晶圓,其中包括了像Nintendo Switch使用的Tegra X1晶片、Pascal和Volta GPU,當然占比很大的還有Turing GPU,部分7nm的應該是下一代的Ampere GPU。而這次提前用上5nm製程進行晶片開發,可能是受到外部競爭壓力和新晶片需要的影響。我們也比較好奇,NVIDIA這葫蘆里賣的是什麼藥。 ...

2年升級一次 Intel 10nm、7nm及5nm工藝開發不會削減投資

在去年了量產10nm工藝之後,按計劃Intel將在2021年推出7nm工藝,5nm也會在2023年問世,回到之前的2年升級一次的周期。

開發新工藝、提升新工藝產能都是需要錢的,不巧的是今年遇到了疫情危機,Intel也不得不推遲或者削減部分投資,可能會多花掉6到8周的資本開支,顯然有些項目會受到影響。

但是Intel的先進工藝不會被削減成本的問題困擾,Intel在財報會議上表示,10nm、7nm及5nm工藝的任何重要資本開支都在按計劃進行,不受影響。

Intel的7nm工藝將在Xe架構的高性能GPU上首發,官方目前還沒公布技術細節,但是晶體管密度預計在2億/mm2到2.4億/mm2之間,超過台積電的5nm,略低於台積電的3nm。

按照這個趨勢下去,2023年的5nm工藝將會徹底反超台積電及三星的3nm工藝。

作者:憲瑞來源:快科技

蘋果下半年轉向5nm AMD將超高通、華為成台積電7nm第一大客戶

在最近一次財報會議上,台積電表示5nm正在量產提速中,下半年將向市場推出商用芯片產品。

來自Digitimes的報道稱,AMD日前吃進3萬晶圓訂單,占到彼時台積電7nm產能的21%。雖然台積電的7nm產能在今年初就被預訂一空,但因為疫情事件,短暫出現空擋,可隨即就被AMD、NVIDIA等捷足先登。

報道指出,在下半年蘋果轉向5nm後,AMD將超越高通和華為海思,成為台積電7nm第一大客戶。

實際上,AMD不僅現款產品依賴於7nm,下半年的Zen 3、RDNA2、CDNA同樣是7nm或7nm+,更不說動輒千萬甚至上億出貨的PS5、Xbox Series X等。考慮到當前的市場表現,蘋果的悄然轉型等於也是解了AMD燃眉之急。

另外,盡管沒有一號客戶蘋果那麼激進,但AMD的5nm也在准備中,預計明年的Zen 4、RDNA3、CDNA2等上馬。

早先有消息稱,為了牢牢鎖定AMD這個客戶,台積電甚至要為其專門定製一套高性能的5nm工藝方案。

作者:萬南來源:快科技

流失華為/NV訂單 台積電挽留AMD 開發專屬5nm

7nm時代,台積電大獲全勝。剛剛公布的今年一季度財報顯示,其收入同比繼續增長,其中7nm晶圓銷售占比達到35%,成為絕對龍頭。

不過,最新有消息傳出,華為減少了下一代海思5G SoC的訂單量,而且NVIDIA也決定選擇三星代工其下一代GPU產品。

當然即便如此,台積電的5nm的客戶依然紛至沓來,何況蘋果、高通、AMD尚在列。有趣的是,報道稱,台積電將為AMD開發一套專屬的5nm製程,以牢固與AMD之間的關系。

根據官方路線圖,AMD的5nm產品包括Zen 4、RDNA3、CDNA2等,這套專門的5nm估計是特別為高性能計算訂制,畢竟AMD對於功耗、晶體管規模的需求與蘋果、高通的SoC不盡相同。

另外,回到剛才提及的華為。雖然手機SoC訂單有所減少,可華為同步增加了基站芯片的代工訂單,台積電並未因此損失多少。

作者:萬南來源:快科技

台積電5nm工藝速覽:引入更多EUV掩膜,密度提升1.84x

最近有業內消息稱,台積電將會在下個月開啟5nm製程的大規模量產,上周六,WikiChip將他們從各種會議上掌握到的台積電5nm工藝信息整理成了文章,本文就簡單介紹一下台積電5nm製程的一些特性與它達成的目標。

圖片來自於WikiChip,下同

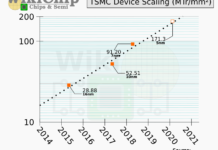

WikiChip預測台積電的5nm工藝密度將達到171.3MTr/mm2,而在IEDM上面,台積電公開密度提升有1.84倍,與WikiChip預測的1.87倍十分相近。

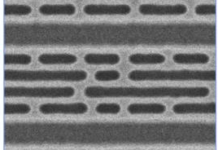

台積電N5工藝使用的EUV掩膜

根據台積電在IEDM會議上面的發表,WikiChip推測它的柵級間距為48nm,最小鰭片間距為30nm,相對於N7工藝,前者是0.84x,後者則是0.75x。單元高度仍為6T,與N7工藝相同,另外N5 HPC可能將會把單元高度擴大到7.5T。

然後看到工藝在性能和功耗上面的改進,在IEDM上面,台積電介紹N5在同能耗下能夠提升15%的頻率,在同頻率下降低30%的能耗。另外,對於由60%邏輯電路、30%SRAM和10%I/O電路組成的典型移動SoC,N5能夠讓它的尺寸減小35%~40%。

N5除了N7時代就有的uLVT(ultra-LVT)工藝外,還新增了一種eLVT(extreme-LVT)工藝,相比起N7 uLVT,它能夠提升25%的頻率,而在不追求極限密度的N5 HPC工藝下,它相比uLVT還能提高10%的頻率。

台積電強調N5將會大規模使用EUV光刻,而實際上這將會是台積電的首個主要EUV節點。因為N7+不兼容原有的電路設計,基本上沒幾個客戶用,而台積電也將N5設計為N7主要的遷移節點。

通過大規模引入EUV光刻,台積電成功地減少了N5所需的掩膜數量,上圖是將N16所需的約60層掩膜作為底數算出來的情況,如果N5沒有使用EUV光刻,那麼它所需的掩膜數量將從N7的1.45x激增到1.91x。而在EUV光刻的幫助下,N5使用的掩膜數量甚至比N7的87層還要少,約為1.35x/81張。台積電使用了約10層EUV掩膜,它們成功取代了至少4倍的DUV層。

另外,台積電還在N5上面引入了高遷移率通道(High-mobility Channel)這項新技術來改善驅動電流的情況。官方並沒有給出具體實現情況,不過WikiChip認為台積電可能為pMOS期間使用了SiGe通道,也就是引入鍺元素。它將會帶來約18%的性能提升,相當可觀。

N5的其他改進還有Scaling Boosters和內部互聯,不同都沒有公布太多細節。

N5對於SRAM生產有兩種庫,高密度(High-Density)和高性能(High-Performance)庫,前者的單元面積為0.021μm2,後者的面積為0.025μm2,無論採用哪種庫,其密度都是迄今為止最高的。

在N5製程下,用作L1緩存的SRAM可以在0.85V電壓下跑到4.1GHz,如果將電壓提高到0.9V,其頻率還可以進一步提升到4.2GHz。

台積電測試晶片的規格

在年內我們應該能看到應用台積電N5工藝的SoC,比如說蘋果的A14和華為的下一代旗艦SoC。要上桌面端的話,還是要等等,高密度帶來的一個問題就是高積熱,這是很難解決的。

如果台積電的N7還不能說是完全領先於其他家的話,那麼N5是真的拉開了很大的差距,三星的N5密度比台積電的低太多了,而Intel的7nm也許可以追上,但是還要很長的時間。 ...

比官方宣傳還猛台積電5nm晶體管密度比7nm提高88%

一般來說,官方宣傳數據都是最理想的狀態,有時候還會摻雜一些水分,但是你見過實測比官方數字更漂亮的嗎?

台積電已在本月開始5nm工藝的試產,第二季度內投入規模量產,蘋果A14、華為麒麟1020、AMD Zen 4等處理器都會使用它,而且消息稱初期產能已經被客戶完全包圓,尤其是蘋果占了最大頭。

台積電尚未公布5nm工藝的具體指標,只知道會大規模集成EUV極紫外光刻技術,不過在一篇論文中披露了一張晶體管結構側視圖。

WikiChips經過分析後估計,台積電5nm的柵極間距為48nm,金屬間距則是30nm,鰭片間距25-26nm,單元高度約為180nm,照此計算,台積電5nm的晶體管密度將是每平方毫米1.713億個。

相比於初代7nm的每平方毫米9120萬個,這一數字增加了足足88%,而台積電官方宣傳的數字是84%。

雖然這些年摩爾定律漸漸失效,雖然台積電的工藝經常面臨質疑,但不得不佩服台積電的推進速度,要知道16nm工藝量產也只是不到5年前的事情,那時候的晶體管密度才不過每平方毫米2888萬個,5nm已經是它的幾乎六倍!

另外,台積電10nm工藝的晶體管密度為每平方毫米5251萬個,5nm是它的近3.3倍。

作者:上方文Q來源:快科技

三星5nm工藝生產線6月底完工 首發驍龍X60 5G芯片

2020年,全球最先進的半導體工藝要從7nm升級到5nm了,台積電最近上半年就開始量產5nm EUV工藝,而三星也加碼投資,預計6月底完成5nm EUV生產線。

三星在2019年4月份宣布完成5nm工藝開發,也會全面使用EUV光刻工藝,並且IP核心可以兼容7nm工藝的。

與7nm EUV工藝相比,三星的5nm EUV工藝性能提升10%,功耗降低了20%,邏輯面積效率提升25%。

日前韓國媒體報道,三星正在加速在韓國華城建設5nm生產工廠V1,已經對主要的設備廠下單,預計6月底之前完成生產線建設。

不過工廠落成之後,還需要較長時間裝配、調試,預計三星最快會在今年底開始生產5nm工藝,再晚一點就是2021年初。

除了三星自己的芯片之外,三星5nm工藝的客戶還有高通,此前高通發布的驍龍X60 5G基帶就是三星5nm工藝生產的,預計會在2021年上市,搭配新一代的5G平台驍龍875。

作者:憲瑞來源:快科技

Intel 7nm時代明年開啟、5nm重拾領導地位

據外媒報道,Intel首席財務官George Davis在昨天舉行的摩根士丹利會議上發表演講,談及了多個話題,其中特別指出,Intel「毫無疑問正處在10nm工藝時代「,並且將在2021年迎來7nm節點。

Davis指出,Intel目前「肯定是走進了10nm時代」,已經出貨了Ice Lake筆記本芯片、網絡ASIC,並即將發布Xe獨立顯卡和Ice Lake至強處理器。

同時,Intel節點內的工藝升級也進展良好,也就是現有工藝的「+「升級版。Davis透露,在推出7nm工藝之前,基於10nm+工藝的Tiger Lake處理器將通過節點內工藝升級,實現了指數級的進步。

他表示:「我們還為客戶提供了CPU之外的很多產品,並且我們已經開始在工藝方面加速。我們曾經說過在7nm節點上追平,並在5nm時代重拾領導地位。」

Intel 10nm工藝與台積電7nm工藝提供類似的晶體管密度,因此很難說Davis說的是10nm節點的性能還是製造上的經濟性。

在這兩種情形下,Davis預測Intel的7nm節點(大概與台積電的5nm相當)將在2021年末重新追平業內發展水平,而在此之前,這或將對Intel的競爭地位和業績產生影響。

Davis指出,Intel將通過提供差異化的平台級解決方案來應對挑戰,包括在AI和軟件方面進行緊密的硬件集成。

「在2019年5月的分析師日上,我們曾說過:瞧,這(10nm)可能不是Intel有史以來最好的工藝節點,它的產出率將低於14nm,低於22nm,但我們看到的改進讓我們非常興奮。我們預計將在2021年末開啟7nm時代,到時會看到性能上的大幅躍升。"

「此外,為了重拾領先地位,我們加快了10nm和7nm之間以及7nm和5nm之間的重疊,這也會體現在成本方面。從2021年開始,會同時出現10nm取得回報、7nm正進行投資、5nm也開始投資的情況,這些也會影響毛利率。「

Intel計劃在2021年末推出7nm工藝,而有關5nm節點的計劃尚未正式公布。與此同時,台積電正積極推進新工藝,今年上半年量產5nm,並且應當會在2022年末推出3nm節點,因此尚不清楚Intel在5nm節點奪回領先地位的預期,是否是基於台積電目前的3nm計劃。

在此期間,Intel將必須抵禦AMD的挑戰。當被問到Intel是否預測會在服務器領域損失市場份額時,Davis回應說:「今年下半年,我們預計競爭會更加激烈。我們認為,這個時間點會提前,但我們看到市場對我們產品的需求非常強勁。展望我們的產品路線圖,我們預計在從7nm到5nm的過程中會取得更強大的競爭優勢。」

雖然面臨挑戰,但Intel在新的領導層和全新的六大技術支柱的領導下,重新聚焦於其廣泛的IP組合,可以預計Intel將繼續投資不完全依賴工藝領先的最新技術,例如EMIB和Foveros,並在廣泛的產品中採用新的小芯片架構,充分發揮封裝優勢的同時,避開向更小節點邁進時碰到的一些問題。

此外,我們預計Intel將繼續發展超異構計算,推動架構的跨節點組合,以應對未來的挑戰。

作者:上方文Q來源:快科技

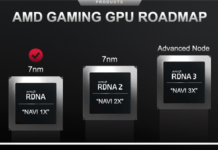

AMD官宣Zen 4架構邁向5nm工藝

FAD 2020分析師大會上,AMD官方公布了未來Zen CPU架構路線圖,包括企業級的EPYC霄龍、消費級的Ryzen銳龍兩條線。

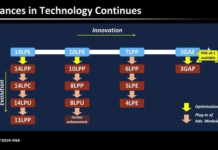

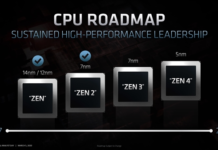

AMD Zen架構誕生於2017年,迄今已經先後有了14nm Zen、12nm Zen+、7nm Zen 2,接下來我們將看到的是7nm Zen 3、5nm Zen 4,一路走到2022年。

AMD雖然此前在多個場合提到過Zen 4,但這是第一次大大方方地登上官方路線圖,據說後邊還會有Zen 5。

此前路線圖上的Zen 3架構一直標注7nm+工藝,而台積電7nm工藝有兩代,一是初代7nm DUV,二是升級版的7nm EUV。由於台積電一直將後者稱為7nm+,我們也自然而然地理解為Zen 3會使用7nm EUV極紫外光刻工藝,甚至樂觀地預計有可能直奔5nm。

不過,AMD現在澄清說,Zen 3不會使用EUV極紫外光刻工藝,而是繼續7nm DUV,但也會相比Zen 2上的初代7nm有提升,至於具體變化將在稍後公布。

當然,也不排除AMD最初計劃在Zen 3上使用7nm EUV,但計劃不如變化,中途更改了。

數據中心企業級市場上的霄龍,AMD已經發布兩代產品,分別是14nm...

台積電5nm打造1700平方毫米巨型中介層 集成96GB HBM2E記憶體

晶體管越來越小,但是高性能計算需求越來越高,有些人就反其道而行之,嘗試製造超大芯片。

之前我們就見識過Cerebras Systems打造的世界最大芯片WSE,擁有46225平方毫米麵積、1.2萬億個晶體管、40萬個AI核心、18GB SRAM緩存……並得到了美國能源部的青睞和部署。

現在,台積電、博通聯合宣布,雙方將利用晶圓上芯片封裝(CoWos)技術,打造面積達1700平方毫米的中介層(Interposer),是芯片蝕刻所用光掩模(光罩)尺寸極限858平方毫米的整整兩倍。

這樣規模的中介層顯然是無法一次性單個製造出來的,台積電實際上是同時在晶圓上蝕刻多個中介層,然後將它們連接在一起,組成一個整體。

工藝上,台積電也用上了最先進的5nm EUV(N5),它將在今年上半年投入量產。

所謂中介層,用途就是串聯不同裸片(Die)的橋梁,因為隨着現代芯片日益復雜,製造單個大型SoC的代價越來越大,所以行業普遍開發出了各種新的封裝技術,將不同的小芯片、模塊整合在一起,構成一顆大芯片。

博通就計劃用這個龐大無比的中介層,封裝多個SoC芯片,以及六顆HMB2記憶體,單顆容量16GB,總容量達96GB/s,帶寬也高達2.7TB/s。

看這規格,應該是三星最新的HBM2E。

台積電和高通未透露這種龐大芯片的具體規格,只是說將用於高性能計算領域。

另外,台積電還在改進CoWoS封裝技術,所以未來不排除面積超過1700平方毫米的更大芯片。

作者:上方文Q來源:快科技

Intel 10nm不會像14nm那樣高產、5nm時代將重奪製程領導地位

由於在14nm上停靠太久,Intel在名義製程工藝上,已經明顯落後台積電與三星。

日前參加大摩TMT會議時,Intel CFO George Davis坦言,10nm不會像14nm和22nm那樣高產。他這番話有兩層意思,一是與14nm並軌的狀態下,10nm產品本身就有限;二是10nm僅會改良1~2代(10nm+、10nm++),以便迅速推出7nm。

Davis確認,第一代改良的10nm+工藝Tiger Lake處理器會在今年底推出。

他同時透露,預計2021年底前拿出7nm產品,之後迅速切換到5nm,並重新奪取製程領域的領導地位。

這個「領導地位「需要解釋下,因為Intel 5nm時,台積電和三星至少都進入3nm了。不過台積電和三星只是名義製程,晶體管規模密度落後Intel一代。換言之,Intel只是重新回到了14nm之前「不擠牙膏」的狀態而已。

然而,即便如此,Intel付出的代價也不小。

Davis給外界敲響警鍾,10nm量產、7nm提速、5nm投資,這都是需要錢的,考慮到這部分技術交集主要集中在2020~2021年,必然會影響到Intel毛利率。

作者:萬南來源:快科技

三星5nm首發影響不大 台積電 2020仍是唯一5nm代工廠

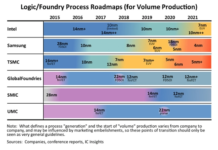

高通公司前晚發布了驍龍X60基帶,這是全球第一個5nm工藝的芯片。三星被證實代工高通5nm基帶處理器,這也意味着三星搶先台積電獲得了5nm訂單。

考慮到之前在10nm、7nm、7nm EUV工藝上,台積電都是領先三星一年半載量產,這一次三星搶發5nm芯片對三星來說意義重大。

對台積電來說,當然這次被三星搶先肯定會丟一點面子,不過台積電在5nm工藝上依然有足夠的底氣。

首先,高通的5nm芯片還不確定是否由三星獨家代工,這幾年來高通在台積電、三星之間是左右逢源,7nm的驍龍865給台積電代工,7nm EUV工藝的驍龍765則是三星代工。

分析師表態,高通5nm基帶芯片訂單也會有三星、台積電分別代工,具體的配比現在則不好確定。

至於高通的下一代移動平台——驍龍875,分析師援引供應鏈的消息稱是台積電代工,不過高通的芯片慣例是第二年初上市,驍龍875要到2021年上半年才量產。

除了高通訂單之外,華為、蘋果的5nm芯片訂單還握在台積電手里,這兩家沒有轉移訂單給三星的趨勢,麒麟1020、A14處理器預計會在Q3季度末發布,他們也是台積電最重要的5nm客戶。

對於5nm,台積電還是相當自信,之前表態2020年他們依然是唯一能夠量產5nm工藝的晶圓代工廠,言外之意三星代工的驍龍X60基帶要到明年才能出貨。

作者:憲瑞來源:快科技

5nm A14芯片性能紙面推演 晶體管規模125億、GB5多核5000分左右

今年的iPhone 12系列依然有不少看點,比如首次支持5G網絡、後置四攝(加入ToF)、搭載5nm A14處理器等。

關於這款SoC,外媒對其性能做了紙面推演。

相較於A13的83億顆晶體管,A14預計在85平方毫米的面積內塞入125~150億顆,超越麒麟990的103億顆。

恐怖堆料後,A14在Geekbench 5中的多線程跑分預計在5000分上下,相當於6核的MacBook Pro了。如果在考慮6GB RAM以及GPU單元規模加大,部分圖形任務場景提升50%將不是問題。

另外,蘋果這些年還特別注重A系列處理器神經運算單元的設計,具體到A14上,設計目標據說至少是A13的兩倍。

歷代的A系列處理器都沒讓用戶擔心過性能,況且蘋果一直能最優先地拿到台積電的先進製程,保證技術強度和產能量級,不得不讓人再次期待起來。

作者:萬南來源:快科技

iPhone 12系列搭載5nm A14處理器及7nm 5G基帶,全部由台積電代工

蘋果2020年下半年將推出四款iPhone 12系列手機,除搭載運算效能更強大的A14 Bionic處理器,也會搭載高通Snapdragon

X55通訊基帶,並將依照各國5G網絡的不同而搭載僅支援Sub-6GHz的5G基帶或同時支援Sub-6GHz及mmWave(毫米波)的5G基帶。先有供應鏈業者指出,蘋果A14處理器將採用5納米製程,高通X55通訊基帶則採用7納米製程,晶圓代工訂單全部由台積電通吃。

台積電2019年及2020年資本支出提升至140~150億美元,用於增加7納米產能及加速5納米產能建置。蘋果2019年推出的iPhone

11系列手機的銷售情況優於預期,加上2020年上半年將推出低價版iPhone SE2並搭載A13處理器,所以蘋果對台積電7納米的晶圓代工需求仍然很高。

隨著各國將在2020年大面積開通5G網絡,蘋果2020年推出的iPhone 12將支持5G。供應鏈消息顯示,蘋果預估推出四款iPhone

12,包括搭載5.4寸及6.1寸OLED面板的兩款iPhone 12、搭載6.1寸OLED面板的iPhone 12

Pro還有搭載6.7寸OLED面板的iPhone Pro Max,其中,iPhone 12 Pro/Pro Max會搭載3鏡頭及ToF。

蘋果iPhone

12系列將全部搭載A14處理器,採用台積電5納米製程打造。台積電的5納米目前已進入試產階段,2020年上半年進入量產,蘋果及華為海思是首批兩大客戶。蘋果看好支持5G的iPhone

12將帶動iPhone 7/8等舊機用戶的強勁換機需求,預估出貨量將在1億部以上,並且,蘋果已包下台積電三分之二的5納米產能,將於2020年第二季底開始量產。

iPhone

12系列將全數搭載高通5G通訊基帶X55。高通X55是現在唯一同步支援Sub-6GHz及mmWave的5G通訊基帶,蘋果將依各國5G的開通情況,而搭載僅支援Sub-6GHz的5G基帶或同時支援Sub-6GHz及mmWave(毫米波)的5G基帶,在蘋果的強勁需求帶動下,高通已開始大舉擴張2020年7納米產能。 ...