IMEC成立於1984年,目前是歐洲領先的獨立研究中心,研究方向主要集中在微電子,納米技術,輔助設計方法,以及信息通訊系統技術(ICT)。近日,IMEC就發布了其1nm以下工藝的路線圖,分享了對應的電晶體架構研究和開發計劃。

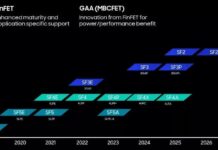

據TomsHardware報導,IMEC的工藝路線圖顯示,FinFET電晶體將在3nm走到盡頭,然後過渡到新的Gate All Around(GAA),預計2024年進入大批量生產,之後還會有FSFET和CFET等。A代表的是埃米,10A等於1nm。

隨著時間的推移,遷移到更小的製程節點會變得越來越昂貴,原有的單晶片設計方法已經讓位給小晶片設計,意思是將晶片的各種功能分解成各種小晶片,然後再連接到一起作為整體運行。IMEC對CMOS 2.0範式的願景包括將晶片分解成更小的部分,將緩存和存儲器分成具有不同電晶體的單元,然後以3D排列堆疊在其他晶片功能之上。這種方法還將嚴重依賴後端供電網絡(BPDN),會將所有供電改到電晶體的背面。

通過系統技術協同優化(STCO)重新思考設計過程,對系統和目標應用的需求進行建模,然後利用這些知識為創建晶片的設計決策提供信息。在這個過程中,會將晶片拆分為單獨單元,以使用不同類型的電晶體來優化每個單元所需的性能特徵,從而降低成本。其目標之一是將緩存/記憶體拆分到它們自己獨特的3D堆疊設計層,從而降低晶片堆棧的復雜性。

CMOS 2.0是通往真正3D晶片的道路,目前AMD利用3D V-Cache技術將L3緩存堆疊在計算晶片頂部以增大容量,IMEC設想的是整個緩存層次包含在自己的層中,L1、L2和L3緩存垂直堆疊在構成處理核心的電晶體之上。每一層緩存都將用最適合該任務的電晶體來創建,由於SRAM的縮放已大幅減緩,這意味著可以讓SRAM有可能使用舊的製程節點來降低成本,理想情況下3D堆疊還可以幫助緩解與大型緩存相關的延遲問題。

來源:超能網