Tag: 3D堆疊

IMEC公布亞1nm電晶體路線圖:3D堆疊的CMOS 2.0計劃

IMEC成立於1984年,目前是歐洲領先的獨立研究中心,研究方向主要集中在微電子,納米技術,輔助設計方法,以及信息通訊系統技術(ICT)。近日,IMEC就發布了其1nm以下工藝的路線圖,分享了對應的電晶體架構研究和開發計劃。

據TomsHardware報導,IMEC的工藝路線圖顯示,FinFET電晶體將在3nm走到盡頭,然後過渡到新的Gate All Around(GAA),預計2024年進入大批量生產,之後還會有FSFET和CFET等。A代表的是埃米,10A等於1nm。

隨著時間的推移,遷移到更小的製程節點會變得越來越昂貴,原有的單晶片設計方法已經讓位給小晶片設計,意思是將晶片的各種功能分解成各種小晶片,然後再連接到一起作為整體運行。IMEC對CMOS 2.0範式的願景包括將晶片分解成更小的部分,將緩存和存儲器分成具有不同電晶體的單元,然後以3D排列堆疊在其他晶片功能之上。這種方法還將嚴重依賴後端供電網絡(BPDN),會將所有供電改到電晶體的背面。

通過系統技術協同優化(STCO)重新思考設計過程,對系統和目標應用的需求進行建模,然後利用這些知識為創建晶片的設計決策提供信息。在這個過程中,會將晶片拆分為單獨單元,以使用不同類型的電晶體來優化每個單元所需的性能特徵,從而降低成本。其目標之一是將緩存/記憶體拆分到它們自己獨特的3D堆疊設計層,從而降低晶片堆棧的復雜性。

CMOS 2.0是通往真正3D晶片的道路,目前AMD利用3D V-Cache技術將L3緩存堆疊在計算晶片頂部以增大容量,IMEC設想的是整個緩存層次包含在自己的層中,L1、L2和L3緩存垂直堆疊在構成處理核心的電晶體之上。每一層緩存都將用最適合該任務的電晶體來創建,由於SRAM的縮放已大幅減緩,這意味著可以讓SRAM有可能使用舊的製程節點來降低成本,理想情況下3D堆疊還可以幫助緩解與大型緩存相關的延遲問題。 ...

IME突破四層3D堆疊技術, 未來晶片或許就像三明治

隨著半導體工藝技術的研發愈加困難,想突破更先進的工藝變得相當不容易。且不說英特爾在14nm工藝節點徘徊了很久,想進入10nm以下區域估計也要費不少周折,即便處於領先地位的台積電(TSMC),近期也傳出3nm工藝延期的消息,至於台積電身後的追隨者三星,似乎也不是特別順利。 既然工藝技術提升受阻,或者要換個方式來提高未來晶片的性能了,也許3D堆疊技術是一種選擇。據TomsHardware報導,Institute of Microeletronics(IME)的研究人員剛剛實現了一項技術突破,實現了多達四個半導體層的堆疊。與傳統的二維製造技術相比,可以節省50%的成本,該技術可能會用於未來的CPU和GPU上,或許真正的新一代3D晶片堆疊就在眼前。

相比此前台積電和AMD的SRAM堆疊技術,IME的這項新技術更進一步。在AMD展示採用3D堆疊技術的Ryzen9 5900X處理器的原型設計里,基於台積電無損晶片堆疊技術的產品只有兩層,第一層是Zen 3架構的CCX,第二層是96MB的SRAM緩存。IME的研究人員則展示了另外一種工藝,通過TSV(矽通孔技術)成功粘合了四個獨立的矽層,允許不同模具之間通信。

這樣的技術帶來的好處是顯而易見的,可以允許晶片由不同工藝的組件在不同晶圓中製造,在近期英特爾的演講中可以感覺到,新晶片的設計上已經往這方面的思路發展了。這樣的堆疊當然也會帶來其他的問題,就如許多人所想的那樣,雖然晶片效率提高了,但要面對散熱問題,所以會看到許多奇特的、直接用在晶片上的散熱技術開始浮現。

來源:cnBeta

英特爾公布Lakefield細節:3D多層堆疊+大小核搭配、超小封裝實現完整計算SoC

英特爾早在幾個月前就確認了Lakefield處理器,這款處理器最重要的技術就是英特爾的Foeveros

3D封裝技術,可以將不同架構、工藝的核心封裝在一起,提供了極大地靈活性。在近日的Hot Chips 31會議中,英特爾也將一些技術細節公布出來。

根據Tom's Hardware的報導,英特爾在Hot Chips

31進行了Lakefield處理器的技術講解。在幾個月前英特爾已經公布了一些規格,包括Lakefield處理器猜就得是1個大計算核心+4個小核心,構成了類似於ARM的big.LITTLE架構形式。3D堆疊讓處理器的集成度更高。英特爾稱Lakefield處理器主要目標是開啟全新規格的移動計算設備,並為這些設備提供較強性能的同時保證低TDP,做到持續在線及非常低的待機功耗。而第一代就是Lakefield。

Lakefield處理器的封裝大小為12×12mm,厚度為1.00mm,大小與一枚硬幣相仿。可在極小的PCB上實現完整的計算平台。

對比之前的處理器尺寸,新的Lakefield處理器要小不少,對比SkyLake-U第一代Y系列處理器,Lakefield僅為其40%大小。採用POP封裝的LPDDR4及LPDDR4X記憶體。電源管理也改為了PMIC。

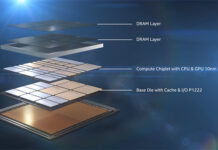

除了3D封裝帶來的好處外,英特爾稱3D封裝最重要的好處可以用不同的工藝適配不同的模塊,以發揮出不同工藝的優勢。比如低漏電P1222工藝用於基礎Die,10nm的工藝用於計算Die。在12×12mm的封裝之上就是基礎層,這一層主要為音頻、USB、UFS等接口。在基礎層之上英特爾並沒有直接放置計算層,而是放了一層Die,分隔計算層和基礎層。英特爾的計算層中包含了CPU核心及GPU核心、這部分採用了英特爾的10nm+工藝製造。在計算層之上就是DRAM層。各層間通過TSV矽穿孔技術提供電力和I/O傳輸。

在計算層,英特爾使用了一個基於Sunny

Cove架構的大核心以及四個基於Tremont的Atom核心。通過大小核的搭配既保證了性能,也保證了效率。英特爾也展示了在Web瀏覽時大小和的調度情況。

降低待機功耗也是英特爾Lakefield處理器的一大目標,相比第六代Core處理器,Lakefield處理器在待機狀態下的功耗僅為其8%。

圖形性能也是英特爾提升的主要目標,在Lakefield處理器中,英特爾也使用了與第十代Ice Lake處理器相同的Gen11

GPU,也採用了64個EU設計,不過主要針對低功耗,所以頻率上應該要低一些。

Lakefield處理器作為第一批英特爾3D封裝的處理器,主要用於低功耗、二合一或雙屏設備。現在Lakefield處理器已處於生產准備就緒的最後階段,將在今年四季度提供樣品。到明年我們就見到採用該處理器的產品了。 ...

利用半導體製冷,AMD新專利有望解決3D堆疊散熱問題

隨著半導體製程工藝的升級難度越來越大,進度越來越緩慢,台積電的7nm工藝開發成本已經超過了30億美元,接下來的5nm工藝預計要超過50億美元,在平面上想提升電晶體密度這事情已經變得相當有挑戰性,3D度堆疊工藝可能是解決這問題的一個好方法,結構簡單的NAND快閃記憶體已經大面積轉向3D堆疊工藝了,HBM顯存也是利用3D堆疊工藝生產的,但是3D堆疊工藝也不是萬能的,散熱就是3D堆疊工藝要面臨的一大難題,層數越多熱量堆積就越嚴重,AMD近日申請的一項專利就有可能解決這一問題的。

CPU也要上3D堆疊工藝了,這是Intel採用Foveros 3D封裝工藝所生產的Lakefield SoC

AMD這一專利的就是在3D堆疊記憶體的邏輯層和存儲層之間插入一片TEC熱點效應散熱模組,也就是我們所說的半導體製冷器或溫差製冷器,它利用珀爾帖效應,由N、P型材料組成一對熱電偶,當熱電偶通入直流電流後,因直流電通入的方向不同,將在電偶結點處產生吸熱和放熱現象。

而這個現象是可以根據電流的方向而反轉的,也就是說可以根據傳感器反饋的結果,都可以利用熱電偶把熱量從較高的那一端轉移到溫度較低的一端,讓熱量分布更為平均,這一專利在任何3D堆疊生產的晶片上都相當實用,然而這一過程是會產生額外的發熱的,也會帶來額外的功耗,所以這一專利是否真的有用我們還得等實際產品出來再說。

...

不遑多讓,AMD有望在CPU和GPU之上直接堆疊SRAM和DRAM記憶體

Intel在去年12月的「架構日」活動上公佈了名為「Foveros」的全新3D封裝技術,該技術首次引入了3D堆疊的優勢,可實現在邏輯芯片上堆疊邏輯芯片,當時Intel展出使用該技術製造的Hybrid

x86

CPU,也公佈了一些規格細節。老對手AMD當然也不甘落後,AMD在最近的活動中透露,他們正致力於在其處理器之上使用3D堆疊DRAM和SRAM的新設計來提高性能。

AMD高級副總裁Norrod最近在Rice Oil and Gas

HPC會議上發表講話,並透露該公司正在進行自己的3D堆疊技術,角度與英特爾的略有不同。此前AMD已經將HBM2記憶體堆疊在其GPU核心旁邊,這意味着它與處理器位於同一個封裝中,但該公司計畫在不久的將來轉向真正的3D堆疊。Norrod解釋說,AMD正致力於在CPU和GPU之上直接堆疊SRAM和DRAM記憶體,以提供更高的帶寬和性能。

其實顯然這種創新已經成為必然的選擇,因為摩爾定律已經失效,多年來業界一直在追求提升半導體工藝不斷降低線寬,但是線寬的微縮總是有一個極限的,到了某種程度,就沒有經濟效應,因為難度太大了。Norrod在會議中也說到,該行業正在達到集成電路微縮的極限。即使是像Threadripper處理器這樣的多芯片設計,由於處理器封裝的尺寸已經非常龐大,也會遇到空間限制的阻礙。

與許多半導體公司一樣,AMD已經調整了應對這新困難的戰略,同時也步入下一個新的浪潮:3D堆疊芯片技術。不過由於熱量和功率輸送限制,該方法也帶來了挑戰。Norrod沒有深入探討正在開發的任何設計的具體細節,但這很可能是AMD處理器設計的一個歷史性節點。

來源:超能網