1947年12月,人類第一代半導體放大器件在貝爾實驗室誕生,其發明者肖克利及其研究小組成員將這一器件命名為電晶體。

就是這一小小的電晶體,在此後的75年不斷改寫世界,與此同時,電晶體本身的發展也進入瓶頸,摩爾定律放緩。

電晶體誕生的第75年,還可以用哪些方法延續摩爾定律?

2022年,我們依然需要新的電晶體

為了紀念電晶體被發明75周年,IEEE(電氣與電子工程師協會)電子器件分會(E lectron Device Society )組織了一場活動,在此活動上有Fin-FET的發明者胡正明教授對電晶體的過去進行回顧,也有諸如英特爾這樣的行業領先者分享在延續摩爾定律上做出的技術創新。

我們的世界是否還需要更好的電晶體?

胡正明在演講中給出了肯定的回答,“是的,我們需要新的電晶體”,並給出了三個理由:

第一,隨著電晶體的改進,人類掌握了從未想像到的新能力,例如計算和高速通信、網際網路、智慧型手機、記憶體和存儲、計算機技術、人工智慧,可以想像的是,未來還會有其他新技術涌現出來;

第二,電晶體廣泛的應用正在改變所有技術、工業和科學,同時半導體技術的演進不想其他技術一樣受到其材料和能源使用的限制,IC使用相對較少的材料就可以生產,並且正在變得越來越小,使用的材料也越來越少,IC本身也在變得更快更高效;

第三,理論而言,信息處理所需的能量依然可以減少到今天所需能量的千分之一以下,雖然我們可能還不知道如何達到這種理論效率,但我們知道這在理論上可行,而其他大部分技術的能源效率已經達到理論極限。

“我相信電晶體現在是,並將繼續是應對全球變暖的關鍵,氣候變化可能會給社會、經濟和個人帶來巨變,因此我們需要更強大的工具來應對這種變化。“胡正明說道。

2030年,單顆晶片可容納1萬億個電晶體

需要新的電晶體是事實,但研發製造出新的電晶體已經舉步維艱,無論是在經濟上還是在技術上,都遇到了新的困難。

電晶體技術的發展道路本就是不平坦的,幾乎每隔一段時間都有巨大的挑戰需要應對。

1980年前後,晶片動態功耗成為大問題,採用CMOS取代NMOS和雙極技術之後,將工作電壓從5伏降低到1伏,帶來了巨大的進步;

2000年至2010年,晶片的靜態功耗再次成為挑戰,按照當時研究人員的預測,每平方厘米IC產生的熱量很快就會達到核反應堆堆芯的熱量,不過後來3D Fin-FET以及多核處理器架構解決了這一問題,電晶體的發展又進入了相對平穩的發展時期。

發展到現在,Fin-FET的進步能夠帶來的性能提升和功耗降低又越來越有限,業界正在採用一種新的3D CMOS結構的環柵(GAA)製造新的電晶體,英特爾就是其中一員。

不久前,英特爾為了進一步縮小電晶體的三維尺寸,用RibbonFET的結構實現了GAA,但是發現源極和漏極之間的距離進一步縮小的同時,會產生比較明顯的短溝道效應而漏電。

如果將傳統的通道材料矽材料換成非矽的新材料,就能改善這種情況。學術界也有了一些相關的研究,使用一種名為過渡金屬硫化物的材料作為通道材料,這種材料只有三個原子的厚度,電子流動性好,作為通道材料有天然優勢。

在這種2D材料方面,針對這種材料,英特爾也做了很多研究和分析,並在會議上展示了一種全環繞柵極堆疊式納米片結構,使用了厚度僅三個原子的2D通道材料,同時在室溫下實現了近似理想的低漏電流雙柵極結構電晶體開關。

除此之外,3D封裝技術也能進一步提升單個設備中電晶體的數目。

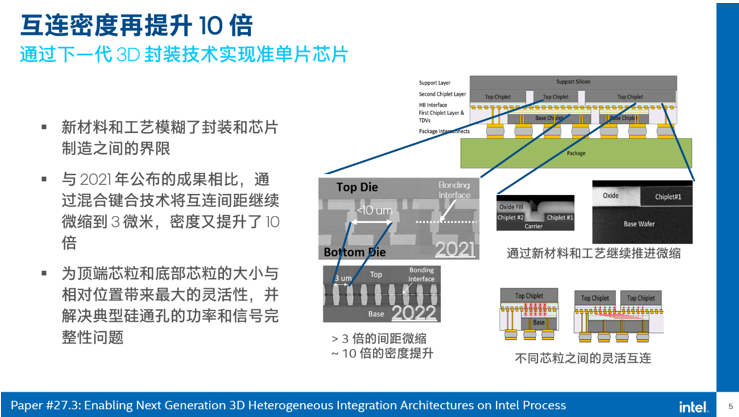

英特爾在3D封裝方面也取得了新進展,與IEDM 2021上公布的成果相比,英特爾IEDM 2022上展示的最新混合鍵合研究將功率密度和性能又提升了10倍。

另外,通過混合鍵合技術將互連間距繼續微縮到3微米,英特爾實現了與單片式系統級晶片(system-on-chip)連接相似的互連密度和帶寬。加上將多晶片互連的工藝里需要的材料換成無機材料,以便於與封裝廠多種工藝要求兼容。

雖然進一步實現電晶體的微縮是一件需要耗費巨大財力和人力的事情,但依然有像英特爾這樣的企業在持續投入研發,並對電晶體的未來抱有期望。

英特爾認為,從2023年到2030年,單個設備中電晶體的數目將翻10倍,即從1千億個電晶體到1千萬個電晶體。

要實現這個目標,需要英特爾等業內領先企業持續投入研發,嘗試更多可行的技術。

不知當一顆晶片中就可以容納1萬億個電晶體的時候,我們的世界又會變成什麼樣子?

來源:快科技