Tag: 封裝測試

俄羅斯自主晶片嚴重受挫:超過50%的都是廢片

據俄羅斯媒體Vedmosit近日報導,俄羅斯自主晶片企業貝加爾電子(Baikal Electronics)在受到西方制裁之後舉步維艱,其封裝的處理器良品率只有不到50%。

報導援引消息人士的話稱:“(貝加爾電子)超過一半的晶片都是瑕疵品,原因一是相關設備還需要正確調校,二是晶片封裝工人技能不足。”

消息人士還透露,俄羅斯已經可以小批量封裝處理器,但達到一定規模後,廢片就會大量出現,無法在規模上維持足夠的良率。

貝加爾電子的處理器採用台積電製造工藝、Arm CPU架構,其中,最多48核心、24MB三級緩存,2.0-2.5GHz頻率,120W熱設計功耗。

但是俄烏沖突後,台積電等晶片製造封測企業完全切斷了與俄羅斯晶片企業的合作,台積電已經製造封裝好的3萬顆晶片都拒絕出貨給貝加爾電子。

但是,俄羅斯本土晶片製造還無法做到16nm,只能自己培育,包括GS Group in Kaliningrad、Milandr、Mikron等等,但看起來進展並不太好,還需要繼續精進。

來源:快科技

美國狂砸30億美元:要在這個先進封裝業圍堵中國廠商

11月22日消息,美東時間周一,拜登政府宣布將投入大約30億美元的資金,專門用於資助美國的晶片封裝行業。

這是美國《晶片與科學法案》的首項研發投資項目,表明美國政府對於美國晶片封裝行業的重視。考慮到美國當前晶片封裝產能在全球占比較低,美國政府的此次投資舉動,也表明其補足弱點的決心。

美國《晶片法案》首項研發投資

隨著晶片行業的戰略地位不斷提高,去年,美國推出了關鍵晶片法案《晶片與科學法案》,旨在重振美國的晶片製造業。

今年2月,美國政府啟動了第一輪《晶片與科學法案》對半導體製造業的資助。截止目前,美國政府已經收到了460多份關於美國半導體製造及相關項目的激勵申請。

不過,本周一宣布的封裝行業投資計劃,是《晶片與科學法案》的第一項重大研發投資。這項投資計劃的官方名稱為“國家先進封裝製造計劃”,其資金來自《晶片法案》中專門用於研發的110億美元資金,與價值1000億美元的晶片製造業激勵資金池是分開的。

這筆資金將由商務部的國家標准與技術研究所管理,該研究所將建立一個先進的封裝試點設施,並為新的勞動力培訓計劃和其他項目提供資金。

投入30億美元發展先進封裝

美國商務部表示,美國的晶片封裝產能只占全球的3%。相比之下,中國的封裝產能估計占38%。

美國商務部副部長勞里·洛卡西奧(Laurie Locascio)在宣布這一投資計劃時表示:“在美國製造晶片,然後把它們運到海外進行封裝,這會給供應鏈和國家安全帶來風險,這是我們無法接受的。”

洛卡西奧聲稱,到2030年,美國“將擁有多個大批量先進封裝設施,並成為最復雜晶片批量先進封裝的全球領導者。

洛卡西奧還表示,美國商務部預計將於明年宣布其晶片封裝計劃的第一個材料和基板資助機會,而未來的投資將集中在其他封裝技術以及更大范圍的設計生態體系。

海外多家封裝巨頭或進入美國

在美國晶片法案的激勵下,已經有不少外國企業計劃將封裝項目落地美國。

此前,韓國晶片製造商SK海力士公司曾表示,將投資150億美元在美國建立先進的封裝設施。

亞利桑那州州長凱蒂·霍布斯也透露,該州正在與台積電進行談判,可能在該州建設先進封裝廠。

大鳳凰城經濟委員會執行長克里斯 卡馬喬此前表示,亞利桑那州正處於與多家全球封裝公司、測試和質量保證公司談判的“中期階段”,預計多家公司可以在2024年破土動工。

來源:快科技

Intel發明全新玻璃基板封裝:互連密度提升10倍

製程工藝不斷提升的同時,整個半導體行業還在持續研究各種先進封裝技術,二者結合打造越來越龐大、強大的晶片。

Intel在先進封裝技術方面尤其有著悠久的歷史和豐富的成果,早在20世紀90年代就引領從陶瓷封裝向有機封裝過渡,率先實現無鹵素、無鉛封裝,EMIB、Foveros、Co-EMIB如今都已經投入實用,Foveros Direct、Foveros Omni也已經做好了准備。

現在,Intel宣布率先推出面向下一代先進封裝技術的玻璃基板,計劃在未來幾年內推出相關產品,可在單個封裝內大大增加電晶體數量、提高互連密度,使得合作夥伴與代工客戶在未來數十年內受益。

玻璃基板組裝晶片的一側

玻璃基板測試晶片

目前普遍採用的有機基板封裝預計會在2020年代末期達到電晶體縮微能力的極限,因為有機材料耗電量比較大,存在縮微、翹曲的限制。

相比之下,玻璃具有獨特的性能,比如超低平面度(也就是極為平整)、更好的熱穩定性和機械穩定性。

使用玻璃材料製成的基板,具有卓越的機械、物理、光學特性,可以在單個封裝中連接更多電晶體,提供更高質量的微縮,並支持打造更大規模的晶片,也就是系統級封裝。

玻璃基板測試單元

Intel CEO基辛格展示玻璃基板測試晶圓

Intel表示,玻璃基板更高的溫度耐受可使變形減少50%,便於更靈活地設置供電和信號傳輸規則,比如無縫嵌入光互連、電容、電感等器件。

同時,玻璃基板極低的平面度可改善光刻的聚焦深度,整體互連密度有望提升多達10倍,還能實現非常高的大型晶片封裝良率。

Intel的目標是到2030年實現單個封裝內集成1萬億個電晶體,玻璃基板將是推動這一目標落地的強有力支持。

來源:快科技

Intel四大先進封裝技術:既能蓋「四合院」 也能建「摩天樓」

隨著半導體製程工藝提升越來越困難,先進封裝技術的重要性則愈發凸顯,成為延續摩爾定律的關鍵。

Intel就一直在深入研究各種先進封裝技術,部分已經得到廣泛應用,比如EMIB、Foveros,部分已經准備就緒,比如Foveros Omni、Foveros Direct。

此前,

現在,Intel通過形象的動圖,詮釋了幾種封裝技術的原理和特點。

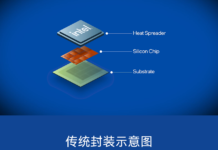

其實,處理器雖然封裝最開始的作用只是防水、防塵和散熱,但隨著製程技術逐漸逼近物理極限,為了滿足越來越高、越來越復雜的算力需求,同時提高能效比,追求可持續發展,先進封裝正變得越來越關鍵。

Intel的先進封裝技術,一方面能夠提升晶片互連密度,在單個封裝中集成更多功能單元,目標是到2030年在單個設備內集成1萬億個電晶體。

另一方面,它們可以滿足Intel自家產品、代工客戶產品的異構集成需求,讓不同供應商、不同工藝打造的芯粒(Chiplet)更好地協同工作,提高靈活性和性能,降低成本和功耗。

一、EMIB

意思是“嵌入式多晶片互連橋接”,原理就像蓋四合院,把不同的晶片放在同一塊平面上相互連接。

傳統的2.5D封裝是在晶片和基板間的矽中介層上進行布線,EMIB則是通過一個嵌入基板內部的單獨的晶片完成互連,可將晶片互連的凸點間距縮小到45微米,改善設計的簡易性,並降低成本。

二、Foveros

3D封裝技術,原理上也不復雜,就是在垂直層面上,一層一層地堆疊獨立的模塊,類似建摩天大樓一樣。

就像大廈需要貫通的管道用於供電供水,Foveros通過復雜的TSV矽穿孔技術,實現垂直層面的互連。

Foveros最早用於Lakefiled處理器,目前正在和EMIB聯手用於各類產品,最典型的就是Ponte Vecchio GPU加速器,使用了5種不同工藝、47個不同芯粒。

三、Foveros Omni

下一代封裝技術,可實現垂直層面上大晶片、小晶片組合的互連,並將凸點間距繼續縮小到25微米。

四、Foveros Direct

使用銅與銅的混合鍵合,取代會影響數據傳輸速度的焊接,把凸點間距繼續縮小到10微米以下,從而大幅提高晶片互連密度和帶寬,並降低電阻。

Foveros Direct還實現了功能單元的分區,使得模塊化設計配置靈活、可定製。

,Intel還展示了最新的混合鍵合(hybrid bonding),將互連間距繼續微縮到驚人的3微米,實現了准單片式的晶片。

也就是說,整合封裝後的互聯密度、帶寬都非常接近傳統的單片式晶片,不同芯粒之間連接更加緊密。

來源:快科技

晶片成本更低 三星開發新一代低溫焊接工藝 2025年量產

當代電子產品中除了要使用各種晶片之外,還要把晶片焊接在PCB上,傳統方式是焊接,但是高溫焊接的成本更高,三星正在研發新一代低溫焊接技術。

據韓國媒體報導,三星電子已開始開發用於下一代高科技封裝的低溫焊接技術,計劃到2025年完成技術開發並實現量產。

據悉,焊料是一種用於連接封裝基板和半導體晶片管芯的材料。

與需要200°C或更高溫度的傳統焊料不同,使用低溫焊料可以降低封裝工藝成本和不良率。

根據國際電子生產商聯盟的預測,到2027年,採用低溫焊接工藝的產品市場份額將增長至20%以上,低溫焊接工藝將成為電子產品焊接工藝的新趨勢。

同時,低溫錫膏焊接工藝也為更多產品集成化拓展了更大的設計自由度和想像空間,將成為助力集成電路產業創新,促進綠色低碳發展的催化器。

不過低溫焊也引發過爭議,因為焊料溫度低,消費者認為容易引發元件脫落,導致各種故障,此前已經有筆記本品牌遭遇過這方面的質疑。

來源:快科技