Tag: 晶圓

芯片代工商DB HiTek調漲2021年代工價格 最低10% 最高20%

12月22日消息,據國外媒體報道,從今年下半年開始,就不斷出現8英寸晶圓代工商產能緊張、考慮提高2021年代工報價的消息,而上周,有報道稱台積電將取消2021年12英寸晶圓代工折扣,變相漲價,晶圓代工漲價的趨勢,從8英寸晶圓延伸到了12英寸晶圓。

而外媒最新的報道顯示,韓國芯片代工商DB HiTek,已決定提高2021年的代工價格。

外媒在報道中表示,DB HiTek已經通知他們的客戶,他們將提高2021年的芯片代工價格,最低上調10%,最高上調20%。

從外媒的報道來看,DB HiTek上調芯片代工報價,也招致了部分客戶的不滿,但最終都接受了漲價,因為他們並沒有其他的選擇,DB HiTek也已同客戶簽訂了2021年的全部芯片代工協議。

一名消息人士表示,DB HiTek此次上調2021年的芯片代工報價,是因為目前全球對芯片代工有強勁的需求,他們的工廠目前也在滿負荷運行。

DB HiTek成立於1997年,在芯片代工的技術和規模方面,雖然同台積電和三星差距明顯,但也是全球重要的芯片代工商之一。官網的信息顯示,DB HiTek是目前全球前十大芯片代工商之一,有兩座世界級的晶圓代工廠。來源:快科技

台積電晶圓優惠價全部取消漲價狂潮不可避免

作為天字一號代工廠,台積電憑借強大的技術、產能實力,掌握着絕對的話語權,一舉一動也會對整個半導體行業產生巨大影響。

據媒體報道,台積電已經取消了針對大客戶的優惠,今後購買晶圓將不再享受任何折扣!

在以往,如果大客戶從台積電大規模訂購晶圓,比如幾萬塊、幾十萬塊,會享受最多3%的優惠價,高通、蘋果、AMD、NVIDIA等等巨頭都是如此。

但這些都已經成為過去式,無論大小客戶,無論采購多少晶圓,都必須向台積電支付全價。

具體原因雖然沒有明確解釋,但眼下的行業形勢已經可以說明一切。

一方面,PC電腦、遊戲主機、電視、智能手機、汽車等各個領域對於芯片的需求都在急劇增長,導致了嚴重的供需不平衡局面,因此不只是台積電,包括聯電、中芯國際等代工廠都遇到了空前的供不應求,自然可以隨時坐地起價,300mm晶圓、200mm晶圓莫不如此。

另一方面,台積電在7nm、5nm等先進工藝方面根本沒有敵手,三星也是勉強競爭,這就讓台積電形成了某種程度的壟斷,如何定價也都在自己的一念之間。

晶圓漲價,必然會增加相應芯片的成本,最終產品的價格水漲船高也不可避免,就看各家如何應對了。

作者:上方文Q來源:快科技

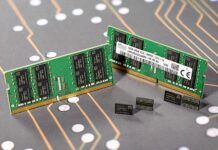

記憶體要漲價?美光回應晶圓廠突然停電 預計將在幾天內恢復產能

12月3日,存儲大廠美光位於台灣桃園的晶圓廠發生停電事件,停電時間約1個小時。據了解,此次發生停電事由並非外力(地震、火災)引起,該公司仍在積極了解停電主因。

據TrendForce集邦咨詢報道,對於此次停電事件,美光最新回應稱,桃園廠區12月3日發生跳電事件,廠區即時啟動安全防護機制。目前設備在復電後已正常營運,美光預計廠區將在幾天內恢復產能。

據悉,目前該廠的月產能為125K,占全球總DRAM月產能1,418K的8.8%,主要產品以DDR4(PC與server DRAM)及LPDDR4為主。

從產能來看,這次受停電沖擊的晶圓廠,占美光產出的30%以上,且該工廠是美光的服務器DRAM生產重鎮。

TrendForce集邦咨詢認為,在當前DRAM市況已經日益轉趨吃緊的態勢下,此次停電事件造成的影響不容小覷。

美光是全球第三大DRAM廠商,TrendForce集邦咨詢旗下半導體研究處最新數據,2020年第三季度,多數原廠的營收表現較上季小幅下滑,僅美光逆市上揚,推升全球DRAM廠自有品牌記憶體營收174.6億美元,季增長2%。

作者:朝暉來源:快科技

記憶體又想漲價?美光桃園晶圓廠突然停電

DRAM記憶體的價格這兩年起起伏伏,2020年整體上一直在走低,32GB單條記憶體甚至殺到了600元出頭,不過到了明年,很可能又會重新漲上去。

有網友戲言,DRAM記憶體廠商又該點一把火、停一次電、中一次病毒之類的了。

真是說什麼來什麼——12月3日,美國存儲巨頭美光位於台灣桃園的晶圓廠突然遭遇停電!

美光表示,廠區第一時間啟動了安全防護機制,確認所有員工安全無虞,但造成的影響正在評估確認中。

至於此次停電事件是否會造成產能損失,並導致記憶體價格上漲,還要進一步觀察,但是存儲廠商們屢屢在市場價格偏低的時候遭遇停電、中毒、火災、水災等各種意外,實在無法不讓「陰謀論」們浮想聯翩。

事實上,就在最近才傳出各路晶圓廠產能吃緊,紛紛開始漲價的消息,而作為DRAM記憶體芯片最大代工廠的力積電更是直言,受到5G、AI應用的推動,直到明年下半年,邏輯芯片、DRAM芯片都會缺貨到無法想象的地步。

作者:上方文Q來源:快科技

200mm晶圓大漲價中芯國際 雙方協商確定

8英寸200mm晶圓相比於12英寸300mm晶圓雖然看起來「落後」很多,但仍有廣泛的市場應用,產能在近來也是越發緊張。

消息稱,受居家辦公、5G的強勁需求推動,大多數代工廠的200mm晶圓價格都上漲了至少20%,緊急訂單甚至要漲價40%,台積電、三星、聯電、中芯國際、格芯莫不如此。

對此,中芯國際在與投資者交流時表示,現有客戶訂單將按已簽訂合同進行,新客戶、新項目則由雙方協商確定價格,公司也會通過優化產品組合,提昇平均晶圓價格。

對於美國早先下達的出口管制,中芯國際表示,目前公司正常運營,並和美國相關政府部門等進行了積極交流與溝通,但具體細節不方便透露。

同時,中芯國際強調目前沒有看到明顯的客戶轉單現象,與客戶保持積極溝通、緊密配合的合作夥伴模式,盡量滿足客戶的需求。

今年第三季度,中芯國際的季度收入首次突破10億美元,同時客戶需求強勁,產能利用率已經接近滿載,預計全年收入可增長至少24-26%,毛利率也將高於去年。

作者:上方文Q來源:快科技

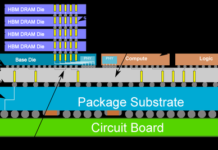

台積電量產第六代CoWoS晶圓封裝 CPU可集成192GB記憶體

據媒體報道,作為全球一號代工廠,台積電已經開始大規模量產第六代CoWoS晶圓級芯片封裝技術,集成度大大提高。

我們知道,如今的高端半導體芯片越來越復雜,傳統的封裝技術已經無法滿足,Intel、台積電、三星等紛紛研發了各種2.5D、3D封裝技術,將不同IP模塊以不同方式,整合封裝在一顆芯片內,從而減低製造難度和成本。

CoWoS的全稱為Chip-on-Wafer-on-Substrate,是一種將芯片、基底都封裝在一起的技術,並且是在晶圓層級上進行,目前只有台積電掌握,技術細節屬於商業機密。

它屬於2.5D封裝技術,常用於HBM高帶寬記憶體的整合封裝,比如AMD Radeon VII遊戲卡、NVIDIA V100計算卡都屬於此類。

CoWoS封裝結構簡圖

Radeon VII集成封裝了四顆HBM

台積電當然也不會披露第六代CoWoS的細節,只是說可以在單個封裝內,集成多達12顆HBM記憶體。

最新的HBM2E已經可以做到單顆容量16GB,12顆封裝在一起那就是海量的192GB!

不知道哦什麼樣的芯片需要這麼大的整合記憶體……

- THE END -

轉載請註明出處:快科技

#台積電#晶圓

責任編輯:上方文Q作者:上方文Q來源:快科技

Intel首席架構師為三星站台 5nm外包有戲

Intel曾經為公司確立了六大支柱,然而隨着閃存業務賣給SK海力士,記憶體和存儲這一支柱已經是蒙上陰影。

而被Intel比作基石支柱的製程和封裝,似乎也要有所動搖了。

Intel在最新財報會議上已經明確表態正在考慮是否將晶圓外包生產,以降低成本、同時挽救自研工藝反復推遲落後的窘境。

日前高級副總裁、首席架構師、架構/圖形/軟件事業部總經理Raja Koduri宣布參加10月28日三星舉辦的高級製造論壇活動(1000X More Compute for AI by 2025),再度讓外界猜測Intel已經想得很明白了。畢竟,去年他還親自造訪三星晶圓工廠。

不過,CEO司睿博強調,Intel沒有決定哪種芯片外包,外包給哪位客戶。從Raja的角度,起碼代表了三星外包Intel顯示芯片的可能性。

為了打消疑慮,司睿博強調Intel不會放棄先進工藝,暗示外包僅僅是彌補7nm延期的短期行為。從市場供求來看,台積電可能看不上Intel的短期單子,三星的客戶則沒有那麼滿載,且價格也稍便宜點。

另外,Intel即便外包,針對的也是2023年之後的產品。

- THE END -

轉載請註明出處:快科技

#Intel#三星#晶圓

責任編輯:萬南作者:萬南來源:快科技

台積電5nm代工價曝光 一片晶圓比7nm幾乎貴了一倍

隨着蘋果A14處理器的推出,台積電的5nm產線已經滿載,正馬不停蹄地趕工中,畢竟除了iPad Air 4,後續還有iPhone 12系列,年底前甚至還有5nm Apple Silicon(A14X?)。

下面來探討一個趣味問題,找台積電代工5nm,需要多少錢?

半導體業內人士chiakokhua在最新Blog網誌中,以一顆類似NVIDIA P100規模的芯片(面積610mm2、907億顆晶體管)為參照,匯總了它在台積電工藝節點下的晶圓和芯片銷售價格。

簡單來說,5nm晶圓單片的代工銷售價約是16988美元,對比7nm,漲幅超80%。

當然,因為晶體管密度大增,同是300mm(12寸)晶圓能切割出來的芯片增多,故換算到單顆芯片的代工價,其實只有238美元,比7nm的233美元只貴了5美元。

考慮到5nm用於商業宣傳上的利好效應、15%的性能提升、30%的功耗下降,這5美元感覺還挺超值。

5nm晶圓之所以貴,主要是工藝復雜,EUV多達14層,每一層都要動用ASML的Twinscan NXE光刻機,這台設備單價超1.2億美元。

另外,目前是5nm大規模量產的初期,良率在逐漸拉升,後期成本會慢慢降下來。

比較極端的例子是,90nm的晶圓可是只要1650美元,可真要做907億顆晶體管規模的芯片,單價需要2433美元。

作者:萬南來源:快科技

Cerebras將7nm製程引入到其晶圓級晶片,現可擁有2.6萬億電晶體、85萬個核心

Cerebras Systems去年的這個時候發布了一款晶圓級深度學習晶片Cerebras WSE(Wafer Scale Engine),尺寸達到了215×215平方毫米。幾乎占據了一整個晶圓的大小。這整個晶片擁有1.2萬億電晶體,40萬個核心,晶片尺寸達到了46225平方毫米,比當前最大的GPU核心要大56倍,現在Cerebras繼續在刷新著記錄。

在今年的Hot Chips大會上,Cerebras表示現在可以實現整個晶片擁有2.6萬億電晶體,85萬個核心,相比之前的規格增加了一倍有餘。然而實現方式其實很「簡單」,因為去年的那款晶片還是採用的台積電16nm工藝進行製造,現在只需換成台積電最新的7nm製程工藝,就可以實現如此壯舉。該公司表示,它已經在實驗室中運行了新款晶片。

當然,這第二代的新款晶圓級晶片仍將具有與第一代相同的晶片面積,畢竟,它受到晶圓尺寸的限制。此外,預計該公司還將增加晶片內置的記憶體容量並加強晶片互連速率,以提高晶片內數據傳輸的帶寬。去年的第一代晶片具有9PB/s的記憶體帶寬,並且這樣一個晶片的TDP為15KW。

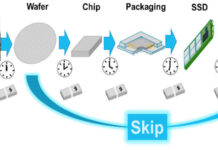

晶圓級晶片除了像Cerebras這樣製作計算晶片的應用外,也有應用於存儲方面的研究。鎧俠(前東芝存儲)正在進行的新研究就是——通過跳過傳統快閃記憶體和SSD製造方法過程中所有切割,組裝,封裝等操作,直接生產晶圓級的SSD ,這樣可以極大地降低製造成本和交貨時間,並且得到高性能的大量數據存儲解決方案。

不過雖然鎧俠提出了「晶圓級固態硬碟」的概念,但是還處在早期開發階段,距離實際上市和應用還很早。目前受矚目的晶圓級晶片還是Cerebras WSE,而關於第二代Cerebras WSE的更多信息,還是得到該公司宣布最終產品時才能知道。 ...

Intel首秀Tiger Lake 11代酷睿晶圓 10nm++、架構翻天覆地

日前的2020年度架構日上,Intel首次公開介紹了,以及所用的,可以理解為10nm++版本。

HotChips 2020半導體大會上,Intel又一次公開講解了Tiger Lake的架構設計,並第一次亮出了Tiger Lake的晶圓:

唯一可惜的,這次是線上會議,晶圓也只能通過視頻欣賞一下,看不到近處細節,不能數一數一塊晶圓能產出多少芯片,自然無法估算大致面積。

Tiger Lake架構、10nm SuperFin工藝的具體特點就不重復了,只看一張Tiger Lake架構的整體圖:

其中,標注藍色的部分是全新增加的,黃色是在Ice Lake基礎上升級的,灰色部分則是和Ice Lake完全一致,而這部分是最少的,而且都是一些無關緊要的模塊,進一步驗證了Tiger Lake架構的變革之大。

新增部分:1.25MB每核心二級緩存、12MB三級緩存、Xe GPU核顯、多媒體引擎、顯示引擎、32GB LPDDR5-5400記憶體支持(後期升級)、IPU6圖像處理單元、PCIe 4.0(移動平台第一次)、USB4、Thunderbolt 4。

升級部分:32GB LPDDR4X-4267記憶體、一致性緩存結構、顯示輸入輸出、USB Type-C輸出、高斯網絡加速器GAN 2.0、電源管理、FIVR(全集成電壓穩壓器)、調試與時鍾模塊。

不變部分:64GB DDR4-3200記憶體、SGX、OPIO。

作者:上方文Q來源:快科技

鎧俠正在研究晶圓級固態硬碟,可達到數百萬IOPS的性能

目前傳統的SSD生產過程是將一片整個的晶圓進行切片,然後封裝,這樣才得到我們常見到的快閃記憶體顆粒與主控晶片,將他們整合在一塊PCB板上就是目前我們見到的SSD。作為生產過程,這些中間的每一步都需要花錢,於是在最近的「 2020年技術與電路研討會(VLSI 2020年研討會)」上,鎧俠(前東芝存儲器)的首席工程師大島茂雄提出了他們團隊正在進行的新的研究——跳過中間步驟,將一整片晶圓直接變成可用的SSD。

據mynavi報導,鎧俠在其內部引入了稱為「晶圓級固態硬碟」的技術概念。通過跳過傳統快閃記憶體和SSD製造方法過程中所有切割,組裝,封裝等操作,直接生產晶圓級的SSD ,這樣可以極大地降低製造成本和交貨時間,並且得到高性能的大量數據存儲解決方案。該技術概念旨在利用「超級多探測技術」,探測和並行操作單個晶片中的數百個晶片。在超級計算機中堆疊和安裝這種具有超級多探測技術的晶圓級固態硬碟將實現數百萬IOPS的巨大性能。

這種晶圓級的晶片在去年其實已經有出現,就是Cerebras Systems推出的晶圓級深度學習晶片,其晶片面積達到46225平方毫米,如果你對這個數據沒有概念的話,作為對比,CPU中的核心裸片大小一般在200平方毫米以下,而GPU核心的大小也沒有超過1000平方毫米的。官方稱這片晶片的尺寸比當時最大的GPU核心要大56倍,整個晶片擁有1.2萬億電晶體。

目前雖然鎧俠提出了「晶圓級固態硬碟」的概念,但是還處在早期開發階段,距離實際上市和應用還很早。並且,即使實際應用,最初也是用在商業領域,比如需要大量數據存儲的伺服器等。 ...

前十大晶圓代工廠商營收排名 台積電一騎絕塵 中芯國際第5

當下,晶圓代工廠成了香餑餑。近日,集邦咨詢旗下拓墣產業研究院公布了2020年第二季度全球前十大晶圓代工廠營收排名。其中,台積電穩居第一,中芯國際排名第五。

報告顯示,今年第二季度,台積電營收高達101元美元,較去年同期大漲30.4%。三星排名第二,營收36.78億美元,同比增長15.7%;格芯(GlobalFoundries)位列第三,營收14.52美元,同比增長6.9%。

此外,聯電、中芯國際、高塔半導體、力積電、世界先進、華虹半導體、東部高科躋身前十。以下為具體排名:

報告稱,台積電受惠5G手機AP、HPC和遠程辦公教學的CPU/GPU需求推升先進製程營收表現,加上成熟製程產品需求穩定,預估第二季營收年成長超過30%。

針對華為禁令的影響,考量其他客戶包括AMD、聯發科、英偉達、高通等訂單已有規劃,應能減少稼動率下滑幅度(ps. 指一台機器設備實際的生產數量與可能的生產數量的比值)。

三星則受惠高通7系列中高端5G芯片客戶採用率良好,7nm的需求狀況保持穩定,CIS(CMOS影像感測器)、DDIC(顯示器驅動IC)等則預期5G手機滲透率增加而擴大供給。另外擴充EUV生產線,拓展移動業務以外的應用,預估第二季營收年成長達15.7%。

報告提到,中芯國際的NOR Flash、eNVM等12寸晶圓,以及PMIC(電源管理IC)指紋識別芯片與部分通用MCU等8寸晶圓需求支撐營收表現,預估第二季年成長達19%。然而華為禁令可能帶來不確定性,恐影響稼動率表現。

作者:朝暉來源:快科技

3nm/5nm已完工 台積電加速推進2nm

據報道,全球第一大晶圓廠台積電(TSMC)已開始加快下一代2nm節點的研發。

台積電最近剛剛宣布,他們將在2020年第四季度開始生產5nm的產品。可能是為了在與Intel和三星等競爭對手中取得優勢,台積電正以極快的速度迭代新節點。

台積電的資金支出似乎非常明智,研發預算規模達到了近160億美元,今年5nm投入批量生產後,更精密的未來節點也已經在准備中。

具體來說,3nm節點將於2021年上半年投入試生產,而批量生產應於2022年開始。就2nm節點而言,台積電最近為2nm節點購買了更昂貴的極紫外(EUV)光刻機。由於這些EUV機器的高成本,台積電今年的資本支出將不會縮減。

至於2nm的時間線,我們不知道什麼時候台積電將開始試產,因為該節點仍處於開發階段。

如此緊密的節奏,想必會讓蘋果、AMD、高通等客戶加強與台積電的合作以保證製程領先優勢。

作者:萬南來源:快科技

太空也能建晶圓廠?美國成功試驗宇宙EUV光刻技術

2020年5月31日,美國太空計劃創造了歷史,SpaceX DM-2龍飛船(Crew Dragon)上的NASA宇航員羅伯特·本肯(Robert Behnken)和格拉斯·赫利(Douglas Hurley)抵達國際空間站(ISS),這是商業航天器首次將宇航員運送到國際空間站。

國際空間站是企業、政府和大學的研究實驗室。一段時間以來,國際空間站的宇航員已在該實驗室為各個組織進行了大量創新實驗。

例如,最近在國際空間站上進行了世界上第一個基於的EUV光刻實驗,可能為太空高級芯片的製造奠定基礎。

圖片來源:flickr

2019年11月2日,諾斯羅普·格魯曼公司的天鵝座(Cygnus)飛船從弗吉尼亞州的瓦羅普斯飛行研究所 (Wallops Flight Facility)發射升空。航天器攜帶來自Astrileux( 一家為製造7nm以下集成電路提供光學技術的公司)的有效載荷進入國際空間站。有效載荷是由太空科學發展中心(CASIS)和納米機架合作進行的此外,該航天器還載有20多種其他有效載荷。

去年11月,國際空間站的宇航員利用來自Astrileux的有效載荷,在國際空間站的外部平台上進行了光刻實驗。實驗圍繞Astrileux的新EUV光學鍍膜技術進行,目的是確定是否有可能使用Astrileux的EUV塗層捕獲太陽EUV輻射。這些材料構成了波長為13.5nm的EUV光刻工具的光學器件和反射鏡的基礎。

實驗證明,能用Astrileux的EUV塗層捕獲太陽EUV輻射。有朝一日,來自Astrileux的材料能夠成為一類新型的太空儀器。它還為未來基於EUV的空間光刻技術奠定了基礎,該技術使用太陽輻射的能量作為光源。

國際空間站最初於2000年投入使用,它是一個模塊化的太空實驗室,是美國、俄羅斯、日本、歐洲和加拿大的航空航天機構之間的合作。在國際空間站上,宇航員進行天文學、宇宙學、氣象學和物理學方面的科學實驗。

製作芯片和組件是太空中另一個有趣的話題。「實現人類在天空中長期生存這個目標,需要建造一個電子製造的生態系統,以便為國際空間站上的本地化,自我維持社區提供支持,「 Astrileux首席執行官Supriya Jaiswal說。「工作中的宇航員能夠根據需要快速對電子產品進行原型製作,從而在國際空間站上創造新的功能,包括增強計算能力和建造新的智能設備的能力,以及快速修復可能發生在高風險操作中的陳舊或被毀壞的電子設備。」

很難想象一個有大型EUV設備的工廠將在國際空間站甚至在月球或火星上建造。但是在將來,在太空中發展小型晶圓廠或微型晶圓廠是可行的。

為此,航天器或太空殖民地將需要3D打印機和fab工具,以及對晶片進行圖形化(pattern)的光刻技術。這就是需要與Astrileux、太空科學發展中心以及納米艙(NanoRacks)合作的地方。太空科學發展中心是國際空間站的美國國家實驗室(美國政府資助的實驗室)的管理者。

納米艙這家航空航天公司在國際空間站的美國國家實驗室安裝了兩個研究平台。根據納米艙的說法,每個平台最多可容納16個立方體衛星(cubesat)外形尺寸的有效載荷。每個立方體衛星的有效載荷為一個四英寸的立方體。

為了進行實驗,Astrileux設計了有效載荷,並合並到納米艙的立方體衛星中。立方體衛星包括Astrileux有效載荷的內部和外部組件。

去年11月,國際空間站的宇航員將Astrileux的有效載荷安裝在氣閘中,並自動裝載到外部平台上,然後實驗被激活。立方體衛星的一部分暴露在陽光下,使Astrileux的EUV塗層捕獲足夠的太陽輻射。該項目研究了EUV材料在極端輻射環境下如何能經受住降解。

在實驗中,Astrileux的材料成功地展示了EUV的波長范圍(10nm-20nm)。Jaiswal說:「 Astrileux創造了可以在極端輻射環境中生存的新型EUV光學塗層,並可以有效捕獲13.5nm和其他EUV波長的EUV輻射。「

鑒於這一結果,有朝一日,這些材料也會有新的應用。首先,它可以為能夠捕獲EUV輻射的新型空間儀器鋪平道路。Jaiswal說:「 Astrileux的新型EUV光學器件為空間探索、太陽輻射成像、望遠鏡、星系統和太空系統中使用的光學系統的新設計奠定了基礎。」

還有其他一些新的和未來的應用。 「該實驗的目的是為7nm及以下的太空電子製造奠定基礎。「 賈伊斯瓦爾說:「 Astrileux有效載荷在繞地球飛行時測量並捕獲13.5nm光刻波長下的EUV太陽輻射。通常,具有強大光源的EUV光刻工具用於以所需的晶圓產量對晶圓進行圖形化。但是,這種有效載荷可以測量並捕獲可用於對硅晶片進行構圖的自然太陽EUV輻射。」

傳統的EUV光學器件可能需要花費100天以上的時間來對單個晶片進行圖形化,而Astrileux的光學器件最終可以將圖形化時間減少到不到10個小時。反過來,這使得在空間中的小型社區中進行晶圓圖形化和製造成為可行的概念。

同時,在地球上,一些鑄造廠已將EUV光刻技術投入7nm和5nm的生產,並進行了3nm的研發。Astrileux的新型EUV塗層也是生產工廠中EUV光刻掃描儀的理想選擇。

本文編譯自https://semiengineering.com/manufacturing-bits-june-2-2/

來源:快科技

美國熱情邀請 台積電欲拒還迎 赴美建廠尚無具體計劃

為了防止被卡脖子,美國特朗普政府正在極力拉攏全球頂級半導體企業,如Intel、三星、台積電去美國建最先進的晶圓廠,其中Intel作為美國公司,對此很積極,而三星、台積電的態度就有些耐人尋味了。

目前三星、台積電分別在美國奧斯汀、華盛頓州各有一座晶圓廠,不過規模並不大,主要是研發、測試,工藝也不是最先進的了,無法滿足美國政府的要求。

除了在南京有一座16nm工藝的晶圓廠之外,台積電的主力都在本地,包括最先進的7nm及5nm工藝,目前斥資高達200億美元的3nm工廠項目也是在台南,沒有在海外建廠的意思。

對於美國政府的熱情要約,台積電之前多次表態,內部持續評估海外建廠的可能性,美國是其中一個選擇。

但是台積電的態度也是堅定的,目前還沒有做出決定,需要綜合考慮。

此前台積電針對美國建廠提出了三個條件,分別是符合經濟效應、成本有優勢、人員及供應鏈要完備,只有這些要素滿足了,才有可能去美國建廠。

對半導體工廠來說,資金、技術、人力及客戶都是重要因素,建廠的決定不是隨便就能做出的,否則動輒上百億美元的投資很難收回。

作者:憲瑞來源:快科技

點沙成金 Intel處理器製造全過程揭密

如今能獨立設計、製造尖端半導體芯片的企業屈指可數,Intel當屬各種翹楚,可以在不超過一個指甲蓋大小的面積內封裝數十億個微小的電子開關。這是人類最復雜的壯舉之一。

最近,Intel特意製作了一段動畫視頻(戳這里),展示了一顆芯片從概念到客戶手中的整個旅程,堪稱「點沙成金「。

晶體管是所有現代電子產品的核心,是比頭發絲還要細微上萬倍的微型開關,控制着電子在電路中的流動。

在處理器整個加工過程的開始,需要將富含硅的沙礫熔化,並冷卻形成固體,然後切割成晶圓。

純淨的晶圓進入工廠後,就開始了復雜而漫長的加工旅程。這些晶圓將被裝載到前開式晶圓傳送盒(Foup),並沿着一條數百公里長的軌道,運輸到一個個加工環節中去。

晶片需要經歷一系列重要步驟,如光刻、離子注入、蝕刻,為關鍵的晶體管形成過程做好准備。Intel全球首家推出了FinFET三維晶體管,而製造它首先需要建造一個鰭狀的通道。

Intel設計了多項創新技術,克服持續擴大集成電路規模所面臨的障礙,其中之一就是名為「gate last」(後柵極法)的突破性製造方法。

它採用先建造臨時柵極、再將其移除的方法,精確放置介電質材料和金屬柵極,能讓柵極包裹鰭片,用以控制通過通道的電子流。

另一項發明則是將晶體管接觸層移動到有源柵極的正上方,為此需要讓柵極材料凹陷並填充絕緣介電材料,以防止發生短路。

接下來,要對柵極附近的電介質進行蝕刻、填充金屬、凹陷加工並加頂,以實現允許高密度接觸層幾何圖形的全新自對准工藝,然後選擇性地對介電材料進行蝕刻,僅暴露所需部分,以連接到第一條金屬線。

這一工藝是通過創新的通孔蝕刻和沉積方案完成的,可實現「有源柵極上接觸」。

最後,添加數十層金屬互連線來完成電路。

經過1000多道復雜的工序後,最終才能進行晶圓的切粒和封裝,得到我們熟悉的處理器。

Intel強調,不斷創新的處理器封裝方式已經成為先進計算架構的關鍵特性,2D和3D封裝技術實現了新的封裝規格,並進一步提升了性能和能效。

作者:上方文Q來源:快科技

格芯與環球晶圓達成12英寸SOI晶圓合作協議 將用於RF射頻芯片

日前Globalfoundries格芯宣布與全球第三大硅晶圓供應商環球晶圓簽署合作備忘錄,雙方未來將進一步合作,由環球晶圓為格芯供應12英寸的SOI晶圓。

環球晶圓目前已經有研發、生產8英寸SOI晶圓,這次合作為雙方合作開發、供應12英寸SOI晶圓鋪平了道路,格芯有望獲得穩定的12英寸SOI晶圓。

SOI是什麼?它的全稱是Silicon-On-Insulator,也就是絕緣體上硅,在硅晶圓基體與襯底之間加了絕緣層,隔離開來,最早是IBM開發的,也是IBM的特色工藝技術之一。

SOI的原理很復雜,大家只要知道SOI工藝具備性能更高、功耗更低等優點就行了,此前業內有個說法就是具備SOI技術的工藝相當於提升了半代水平。

在AMD自己製造CPU的年代里,他們也是SOI工藝的擁躉,32nm SOI工藝時代AMD的推土機處理器就實現了8核5GHz的記錄,SOI工藝也是有功勞的。

格芯從AMD分離出來之後,32nm SOI工藝也用了很長時間,但是種種問題導致產能不行,AMD最終在28nm節點放棄了SOI工藝,轉向傳統的Bulk工藝了。

時至今日,在高性能CPU代工上,格芯依然有少量SOI工藝生產,比如IBM的Power 9及改進型處理器,使用的就是14nm SOI工藝,最新的Z15大型機上實現了12核5.2GHz的提升,說明SOI工藝還是有潛力的。

不過在格芯2018年宣布無限期擱置7nm及以下節點之後,他們的SOI工藝應該沒可能在用於AMD的處理器了,這次與環球晶圓的合作也主要是用於RF射頻芯片,應該是用於他們的22nm、12nm FD-SOI工藝生產線中。

根據格芯所說,他們打算將其領先的RF SOI技術,應用於環球晶圓擴產供應的12吋的SOI晶圓上,經由技術優化,為目前以及下一世代的移動設備和5G應用,提供低功耗、高效能和易整合的解決方案。

作者:憲瑞來源:快科技

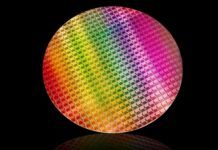

晶圓為什麼是圓形的?

那麼晶圓為什麼是圓形而不是矩形的呢?特別是我們見到的CPU和GPU裸Die都是矩形,如果晶圓不是圓形而是矩形豈不是理論上可以完全無浪費的切割成小片,不是更好嗎?

這需要從晶圓的製造過程說起。

在將二氧化硅礦石與炭混合經由加熱發生氧化還原反應之後,就可以得到粗硅了,但是這時候得到的粗硅純度還不能用於製作集成電路。接下來把粗硅經鹽酸氯化並經蒸餾後則可以進一步得到純度更高的多晶硅,再接下來就有一個很重要的獲取單晶材料的晶體生長方法了,它被稱為柴可拉斯基法,是目前主要的獲取單晶材料的晶體生長方法,利用它可以將多晶硅變成單晶硅。

做法是將前面得到的多晶硅熔解,將晶種(或稱「籽晶「)置於一根精確定向的棒的末端,並使末端浸入熔融狀態的硅。然後,將棒緩慢地向上提拉,同時進行旋轉。對棒的溫度梯度、提拉速率、旋轉速率進行精確控制,那麼就可以在棒的末端得到一根較大的、圓柱體狀(確切的說是像兩頭削尖了的鉛筆的形狀)的單晶硅晶棒。

硅晶棒再經過切片、研磨、拋光後,即成為集成電路芯片的基本原料——硅晶圓片,就是「晶圓」。它經由圓柱體切片而來,所以是圓形。

晶圓是圓形主要是因為集成電路芯片需要單晶硅,而實現單晶硅主要靠柴可拉斯基法,大家可以記住這個方法的名稱,它得名於波蘭科學家揚·柴可拉斯基,他是於1916年研究金屬的結晶速率時,發明了這種方法。現在,柴可拉斯基法已經演變為鋼鐵工廠的標準製程之一。

來源:快科技

富士通A64FX ARM處理器晶圓展示 近距離感受52核心

除了持續統治移動領域,ARM架構也在一直嘗試進入企業級領域,包括服務器、數據中心、超級計算機等。亞馬遜、Ampere、富士通、Marvell、高通、華為等都陸續開發了各自的高性能ARM處理器,比如亞馬遜剛剛發布的64核心Graviton2,還有各種協處理器、加速器。

富士通A64FX就是其中一個典型代表,去年就已公布,並將進入日本的Fugaku/Post-K超算,明年投入使用,有望在超算TOP500榜單上位居前列。

近日,富士通還罕見地公布了它的晶圓,一起來感受下:

如果你對芯片結構有所了解,可以很清晰地看到總計52個核心,其中兩端各有一排10個,中間部位有兩排各12個,它們之間還分散着8個,以及分布多處的緩存。

富士通A64FX採用台積電7nm FinFET工藝製造,集成87.86億個晶體管,但只有596個信號針腳,內部集成52個核心,包括48個計算核心、4個輔助核心(都完全一致),基於ARMv8.2-A指令集,支持SVE 512位寬度SIMD,峰值性能2.7TFlops。

所有核心分為四組,每組13個,共享8MB二級緩存。

互連總線採用6D/Torus Tofu,雙鏈路、10個端口、帶寬28Gbps。輸入輸出支持16條PCIe 3.0。外部搭配四組共32GB HBM2記憶體,峰值讀寫帶寬1TB/s。

文章糾錯

作者:上方文Q來源:快科技

三星記憶體生產設備污染發生在器興工廠 專家 損失遠超10億韓元

關於三星記憶體工廠設備污染一事,更多的細節浮出水面。

時間節點目前有兩種說法,上上周和數周前,地點據韓媒披露位於三星器興(Giheung)工廠,事發原因是8英寸晶圓生產設備受到污染。

三星發言人已經對外確認傳言為真,但強調目前生產狀況正常,此次意外的損失預計在10億韓元左右(約合601萬元人民幣)。

不過,一些專家稱,三星的實際損失遠遠大於這個數字,而且官方並未統計出來。

事實上,今年初,三星的第一代1x nm記憶體也被在工廠階段查出質量問題。

外界一方面擔心三星半導體業務,另外猜測此次意外會否干擾到記憶體的價格走向。

資料補充:器興廠是三星的功勛DRAM工廠,當年三星聖克拉拉團隊逆向工程(參考美光)設計的256Kb DRAM就是在這里投產,採用2微米工藝,奠定了代際突破的基調,使得三星在1993年成為全球最大存儲器芯片廠商。

作者:萬南來源:快科技

Intel中國科普 製造芯片時 工人們為何要統一身穿「兔子服」?

含硅的礦石到了Intel,最終被改造為我們當前用的處理器、記憶體等芯片。

今日上午(10月13日),Intel中國官微發布科普趣味視頻,話題是「製造芯片時,研究員們為什麼要統一着裝?「

簡單來說,在製造芯片時,為防止衣物絨毛磨損芯片,Intel從1973年起就要求研究員們統一服裝。

據悉,Intel實驗室製造線的統一着裝名為「兔子服(Bunny Suit)」,如今的樣式已經很像是太空服,極具科幻感。自1973年誕生以來,「兔子服「已經成為半導體晶圓工廠中工人們高科技創新裝備的代名詞。當然,它也經歷了很長的發展歷程。

在「兔子服「之前,1969年的加州山景城Fab 1中,早期的無塵服標準僅僅是一套工作服和發套。1973年在加州利弗莫爾的Fab 3,是Intel第一個需要員工身着「兔子服」的基地。有員工回憶,好奇的同事會藉口去工廠參觀,以體驗新奇的「兔子服「。

1989年啟用的聖克拉拉D2 Fab中,空氣淋浴器開始亮相,它們被設計用於清潔比手術室還要干淨數千倍的芯片製造無塵室員工。90年代「兔子服」增加了更高級的面罩,還因在奔騰II MMX處理器廣告中而被世人熟知。

進入21世紀,「兔子服「變得更加先進。

作者:萬南來源:快科技

7nm工藝將貢獻25%營收,但台積電12英寸產能還是過剩

在高通與蘋果達成和解協議之後,高通將會再次為蘋果供應手機芯片,除了未來的5G基帶芯片之外,4G芯片顯然也會重新進入蘋果供應鏈,這意味着高通未來的芯片訂單會大漲,這對台積電來說是個機會,再加上AMD、海思、聯發科等公司的訂單,台積電的7nm工藝訂單未來無虞。根據台積電此前的說法,今年7nm工藝訂單帶來的收入將達到全部代工晶圓業務收入的25%,成為絕對的主力。但是從另一方面來說,7nm產能滿載了,台積電其他工藝訂單低迷,特別是12英寸晶圓產能,今年依然有過剩的可能。

Digitimes援引供應鏈消息人士的話稱,盡管台積電7nm工藝的訂單增加,但台積電其他先進工藝的的訂單依然低迷,這導致2019年12英寸晶圓的產能有過剩的風險。在這其中,Q2季度7nm訂單增長主要是來自華為海思、AMD,但是因為PC及消費電子客戶持續調整庫存,其他工藝的12英寸訂單進展緩慢。

消息人士指出,台積電的7nm訂單主要是受即將到來的5G、AI應用的推動,但移動設備、PC電腦、筆記本電腦及消費電子行業的其他客戶還在消化過剩的庫存。

台積電預計Q3季度7nm訂單還會繼續加強,產能利用率可能達到100%滿載,主要客戶來自蘋果、海思、AMD、高通、NVIDIA及聯發科等。

台積電預測今年7nm工藝帶來的營收會大幅增長,全年占比可達25%。此前台積電公布的Q1季度數據中,7nm工藝貢獻了22%的營收,10nm工藝貢獻了4%的營收,20nm貢獻了1%的營收,28nm貢獻依然高達20%,只不過除了7nm之外,28-10nm工藝都在不同程度地下滑。

來源:超能網