Tag: 3納米

性能提升24% 蘋果M3處理器更強了:升級台積電N3E工藝

快科技4月10日訊,晶片行業的製程競賽,將在今年被拉到3nm。

據CT報導,相關法人透露,蘋果新款MacBook Air、iPad Air/Pro等,都將採用台積電3nm N3E工藝量產,分別在今年下半年和明年上半年對外亮相。

筆記本和平板上自然是M3處理器,而N3E則是台積電第二代3nm,對比N5同等性能和密度下功耗降低34%、同等功耗和密度下性能提升18%,或者可以將電晶體密度提升60%。

此前爆料顯示,M3處理器單核比M2 Max(12核)提升24%、多核提升6%。

就目前的進度來看,同樣是3nm,M3不太可能會早於A17處理器,也就是說15寸MacBook Air會在iPhone 15系列之後登場,這或許意味著其無緣在6月6日的蘋果WWDC開發者大會上首秀。

來源:快科技

晶片報廢率80%的3nm可憐蟲:這下有救了

去年底台積電宣布3nm量產,預計今年年中之後在終端層面開始大規模應用。

隨後有業內專家透露,台積電3nm的良率可達80%,非常可觀。

然而,提前半年投產3nm的三星,則有些尷尬,據說良率僅20%。這個表現,難怪沒有大廠敢下單。

雖說三星上馬了GAA電晶體,技術難度高算是情有可原,然而和台積電差距這麼大顯然不是長久之計。

據DT報導,三星正在調整的一個優化方案是,在3nm EUV光刻中引進穿透率達90%的掩模保護膜,供應商是本土公司S&S Tech。

EUV光刻與此案的ArF(氟化氬)曝光設備不同,光反射到鏡子後,再到晶片,因此光源損失很大。要想使光源損失降到最低,必須使用穿透率超過90%的EUV用保護膜,從而保護光罩。

三星這一調整,能否有效提高3nm GAA晶片的良率,還有待檢驗。

來源:快科技

第一代沒人用 台積電第二代3nm工藝首顆晶片流片

日前,Alphawave公司宣布,其成為台積電N3E工藝首批流片的客戶。相關產品會在本周晚些時候的台積電OIP論壇上公布詳情。

據悉,這是一款DSP PHY串行控制晶片,IP核是ZeusCORE100,涵蓋支持了800G乙太網、OIF 112G-CEI, PCIe 6.0和CXL3.0等多項前沿標準,致力於服務下一代數據中心伺服器。

回到工藝本身,N3E實際上是台積電的第二代3nm,性能相比5nm提升18%,功耗降低34%,密度增加70%,大規模量產時間預計在明年二季度到三季度。

台積電的第一代3nm因為沒有客戶已經實質上被放棄,N3E無論在良率、參數指標上都更加優秀。

當然,除了大家不熟悉的Alphawave,N3E未來還大機率會用於蘋果的A17晶片等產品上。

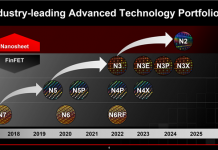

據悉,台積電在3nm上准備了至少5種工藝,之後還有N3P、N3X和N3S。

來源:快科技

台積電3nm:卡殼了

10月19日消息,據媒體報導,在將3nm製程工藝的量產時間由外界預計的9月底推遲到四季度晚些時候之後,當前全球最大的晶圓代工商台積電,將再次將這一先進位程工藝的量產時間推遲3個月。

台積電將3nm製程工藝的量產時間再度推遲3個月,是由韓國率先開始報導的。如果再推遲3個月,量產時間就將推到明年。

在上周四的三季度財報分析師電話會議上,台積電CEO魏哲家曾談到3nm製程工藝的量產事宜。當時他表示他們正推進在四季度晚些時候,以可觀的良品率量產,在高性能計算和智慧型手機應用的推動下,他預計產能在2023年將穩步提升。

但媒體在報導中提到,此前有報導稱台積電的3nm製程工藝在9月底前後就將量產,魏哲家透露的四季度晚些時候,較他們的預計已有推遲。

對於3nm製程工藝的量產時間由媒體預計的9月底推遲到四季度晚些時候,韓媒稱主要是因為設備的交付出現了問題,導致他們的供應能力,無法滿足客戶的需求。

但在最新的報導中,媒體並未披露台積電3nm製程工藝量產時間再度推遲的原因。

據悉,三星已經在6月30日投產3nm GAA(全環繞柵極電晶體)晶片,7月25日正式發貨。

來源:快科技

3nm加持 比AMD Zen4更先進的蘋果M2 Pro處理器要投片了

Intel 14代酷睿Meteor Lake似乎遇到了一些問題,導致原定讓台積電3nm代工核顯模塊的計劃延期。

一方面,台積電放緩了3nm擴產進度,另一方面,Intel騰退的這部分3nm,自然被蘋果笑納。

最新消息稱,蘋果確定會是年內第一家投片台積電3nm的企業,首款產品可能是M2 Pro處理器。明年,蘋果還有A16、M2後續增強版以及M3要交給台積電3nm代工。

此前,搭載M2處理器的MacBook Pro以及MacBook Air已經上市發貨,按照蘋果的說法,M2依然是5nm工藝,但蘋果重新設計內部架構後,電晶體規模更大,CPU性能提升18%,GPU提升35%。

M2標準版採用8核CPU+10核GPU+16核NPU設計,和M1時代的家族改進類似,M2 Pro/M2 Max主要會顯著增加圖形單元規模,可能最大12核CPU+38核GPU。

來源:快科技

Intel突然叫停3nm代工:台積電被打了個措手不及

規劃中的Intel 14代酷睿Meteor Lake處理器將採用多晶片堆疊設計,其中CPU計算單元由Intel 4nm工藝製造,核顯部分則是台積電操刀。

然而,來自調研機構TrendForce的最新報導稱,原本作為台積電3nm第一批客戶的Intel,因為產品設計和工藝驗證問題,量產時間從今年下半年推遲到明年上半年後,再度延期到了明年底。

也就是說2023年前,Intel幾乎取消了對台積電的3nm投片,只有少量驗證晶圓單子。

這一意外情況打亂了台積電的生產計劃,如果不是因為其3nm工藝本身出了什麼岔子,那就意味著蘋果不僅將首發台積電3nm,而且會是今明兩年的唯一客戶,對應產品包括M系列晶片、A17仿生晶片等。

對於台積電來說,3nm成本巨大,Intel的突然叫停,不得不讓自己考慮放緩擴產計劃,從而攤薄成本壓力。他們一方面要通知設備供應商調整2023年的意向訂單,一方面也將削減資本支出。

由於AMD、聯發科和高通的3nm產品都安排在2024年,台積電的3nm屆時才能步入正軌,包括取得可觀的營收利潤等。

來源:快科技

被騙好久:2nm/3nm晶片的牛皮吹破了

8月2日消息,英特爾、三星和台積電都在吹噓他們能在一個小小的晶片上塞進多少電晶體,但就事實而言,這種宣傳中的納米級尺寸幾乎沒有任何意義。業內專家稱這種說法都是無稽之談,事實上的晶片“節點”尺寸遠大於廠商們宣傳的數值。

製造用於智慧型手機、電視和其他電子產品的晶片廠商們總喜歡吹噓自家產品的強大算力。他們還誇口說,完成所有復雜工作的晶片體積正在不斷縮小。

對於晶片製造商來說,晶片電晶體的日趨小型化標志著處理速度不斷提高或能源消耗不斷降低,有助於贏得利潤豐厚的合同。

但是,關於晶片小型化的競爭導致市場一片混亂。多少納米的晶片往往與與電晶體大小有關。多年來,人們普遍認為數字越小,晶片就越好。

三星最近開始批量生產所謂的業內首款3納米晶片,公司高管舉起三根手指慶祝這一時刻。但如果問問台積電和英特爾的看法,他們可能會建議三星高管們再多舉起一根手指,甚至更多。

與台積電關系密切的一家研究機構咨詢總監楊瑞麟(音譯)說:“請不要把注意力放在數字3上。”

與此同時,哈佛商學院教授史兆威(Willy Shih)說,僅從數字上看,目前還不能確定三星的3納米晶片一定優於台積電的4納米晶片。他說,晶片計算性能和能耗等因素都需要進行比較。

“這是營銷炒作的勝利,”他在談到晶片行業的納米尺度時說。

三星拒絕就自家晶片與台積電產品的對比發表評論。公司表示,其生產最新晶片是在之前使用5納米製程工藝技術基礎上進行了改進。

半導體行業的宣傳和其他行業的營銷噱頭沒什麼兩樣,比如現代服裝尺寸上的變化就是如此,腰圍34英寸的男性如今能穿上標記為“32”的褲子,女裝的8碼可能是昨天的16碼。

晶片行業過去常常聯合起來創建通用的測量標準。幾十年來,這種標準一直遵循著摩爾定律。晶片“節點”在小型化方面不斷突破,將原本冰箱大小的電腦最終縮小為筆記本電腦、智慧型手機和手錶。

讓問題更加復雜的是,過去幾十年,從事尖端晶片生產的公司數量從幾十家減少到了三家,它們分別是台積電、三星和英特爾。

誰都想在原本參與者不多的市場中再多分一杯羹,何況在彼此之間幾乎沒有什麼可合作的領域。最先進的晶片已經把電路縮小到幾個原子的大小。

在這個小型化的世界里,晶片製造商用納米為單位來彰顯自家技術實力。這個數字指的是電晶體中關鍵部件柵極的長度,用來調節電流大小。更小的柵極意味著更小的電晶體,更小的電晶體意味著單個晶片上可容納的電路更多。

隨著納米數越來越接近於零,對柵極尺寸的估計變得越來越離譜。納米命名法現在簡直成了一家晶片廠商願意在多大程度上歪曲事實的標準。

在技術方面落後於台積電和三星的英特爾去年對所有高端晶片都進行重新命名,10納米晶片成為了“英特爾7”。執行長帕特·蓋爾辛格(Pat Gelsinger)當時承認,包括英特爾在內的這類行業標簽“不再涉及任何具體的衡量標準”。

蘋果公司在推出iPhone 6S系列智慧型手機時,就通過台積電和三星製造自家設計的SoC組件,這就是其智慧型手機的中央處理器。

三星向蘋果提供的是14納米晶片,台積電提供的晶片尺寸是16納米。iPhone 6s發布後,技術評測人員在對性能進行對比測試後得出結論,內置台積電晶片的iPhone性能反而略好,手機發熱現象更少,電池能耗表現更好。蘋果目前只在iPhone中使用台積電代工的晶片。

據知情人士透露,這場競爭暴露出晶片行業幾乎不為人知的秘密。事實上,台積電和三星的晶片都不符合標稱。知情人士說,這兩種晶片的尺寸都在30納米左右。

“如果他們在上數學課,我會用尺子敲打他們所有人的手,”曾為英特爾(Intel)和高通(Qualcomm Inc.)等晶片製造商提供咨詢服務的半導體和計算機專家大衛·坎特(David Kanter)說。

一些晶片專家建議創建一個新的系統,用性能、功耗降低程度或成本價格等其他指標來取代納米數字。電氣與電子工程師協會(IEEE)下屬雜誌在2020年發表的一篇文章標題中這樣描述:“節點是無稽之談。”

史丹福大學電子工程教授黃漢森(Philip Wong)提出的解決方案引起業界關註:“LCM密度度量”,因其對邏輯、存儲和連接的衡量而得名。

“我承認,”他說,“這不該是隨口一說的。”

2020年4月,IEEE國際設備與系統路線圖主席敦促晶片製造商“回歸現實”。他提議用三變量度量法來取代納米,用以描述晶片特點。包括英特爾前首席科學家在內的許多人都呼籲清理“節點命名混亂”。

但在晶片市場,對節點尺寸的痴迷仍然很重要。英特爾計劃在2024年推出“英特爾3”,旨在縮小與競爭對手的差距。三星和台積電則計劃在2025年前推出2納米晶片。

來源:快科技

中國廠商成3nm「小白鼠」:三星自家晶片兩年後才用

6月30日,三星代工廠和半導體研發中心的職員齊聚一堂,慶祝公司成為世界首家大規模投產3nm晶片的半導體企業。

雖然三星上馬的是取代FinFET的革命性GAA電晶體,雖然三星把3nm看得無比重要,可BK的報導稱,三星3nm的首家客戶居然是來自中國的一家名為PanSemi(上海磐矽半導體技術有限公司)的礦機晶片企業。

考慮到當前虛擬貨幣慘淡的行情,這筆訂單的量級肯定不會大到哪兒去,對於檢驗3nm GAA的成色也不具備充分說服力。

另一個有趣的細節是,報導稱,三星自家晶片准備在2024年才用3nm,而且是第二代,這就不禁令人質疑,合著你三星搶首發不過是噱頭,今明兩年下單的客戶更是要當「小白鼠」不成?

此外,對於三星3nm GAA量產,台積電的態度似乎雲淡風輕,甚至有業內人士稱,台積電居然打算推遲自家3nm的量產計劃,可以說毫不把對手放在眼里。

圖為三星慶祝3nm GAA量產

來源:快科技

終結FinFET電晶體 台積電正式公布2nm:功耗降低30%

6月17日早間消息,台積電在今日舉辦的2022技術論壇上,首度推出下一代先進位程N2,也就是2nm。

技術指標方面,台積電披露,N2相較於N3,在相同功耗下,速度快10~15%;相同速度下,功耗降低25~30%,開啟高效能新紀元。

就縱向對比來看,2nm之於3nm的提升,似乎不如3nm之於5nm,包括但不限於性能、功耗、密度等所有核心參數。

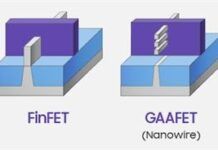

在微觀結構上,N2採用納米片電晶體(Nanosheet),取代FinFET(鰭式場效應電晶體),外界普遍認為,納米片電晶體就是台積電版的GAAFET(環繞柵極電晶體)。

台積電還表示,N2不僅有面向移動處理器的標準工藝,還會有針對高性能運算和小晶片(Chiplet)的整合方案。

時間節奏方面,N2將於2025年量產。

另外,根據台積電最新技術路線圖,第一代3nm(N3)定於下半年量產,3nm也會比較長壽,後續還有N3E、N3P和N3X。

來源:快科技

蘋果留了一手 M2 Pro、M2 Max處理器曝光:3nm性能怪獸

本周的WWDC上,蘋果發布了M2晶片,並搭載於新MacBook Air和13寸MacBook Pro上。

不過,M2雖然性能強悍,可依然是台積電5nm(第二代),這一方面證明蘋果設計開發M2時間很早,另一方面也給M2未來升級疊代的款式買下伏筆。

一名高級分析師Jeff Pu稱,蘋果將在年底前推出M2 Pro處理器,升級到台積電3nm製程工藝。M2 Pro的CPU核心將增加到12核,GPU也會更強大。

當前的M2設計為最高8核CPU+10核GPU,CPU性能提升18%,GPU性能提升了35%。

M2 Pro預計會用於新Mac mini和14寸MacBook Pro,至於M2 Max,最高12核CPU+38核GPU,預計將用於Mac Pro上。

有趣的是,昨天業內人士手機晶片達人還搶先偷跑了M3晶片,同樣3nm工藝,代號Palma,只是要等到明年三季度才能流片了。

來源:快科技

宇宙原始黑洞僅有原子大小:半徑大約只有0.23納米

9月22日消息,據媒體報導,自古以來,人類就想解釋宇宙中最難以預測、最令人不安的現象,盡管人類歷史所有文明都持續不斷地進行天文學研究,但是一些「不可預測」的天文事件,例如:彗星或者日食,被認為是「不幸的預兆」或者「神靈的暗示行為」。

1066年,諾曼公爵威廉推翻撒克遜國王哈羅德二世政權,當時這一重大歷史轉折點被歸因於一顆彗星(之後被命名為「哈雷彗星」)帶來的壞兆頭;公元939年,萊昂國王拉米羅二世率領軍隊與Caliph Ad al-Rahman在西曼卡斯(現今西班牙巴利亞多利德地區)作戰,突然出現的日全食引起了雙方軍隊的恐慌,使戰鬥推遲了數天。

那麼,人類祖先對宇宙中存在的天體會做出怎麼的反應呢?例如:黑洞會吞噬所有事物,包括光。雖然迄今科學家已經觀測到最大的黑洞,並拍攝到該黑洞的照片,同時,科學家在近期研究中還展示了微型黑洞——鉀原子大小的黑洞,半徑約0.23納米(相當於1米的2.3億分之一)。這些原子大小的黑洞形成於大爆炸初期,甚至可能構成宇宙中所有暗物質的總和。

拍攝黑洞

2019年,位於全球不同地區的8個射電望遠鏡拍攝到第一張巨大黑洞照片,該黑洞的質量相當於太陽的65億倍,位於梅西耶87星系中心,距離地球大約5500萬光年(相當於9.5萬億公里的距離)。

如果所拍攝的天體能捕獲光線,它就無法被相機記錄下來,畢竟相機是基於光線變化成像的,但是研究人員可以有其他的選擇,我們可能不觀察物體自身,而是觀察黑洞吞噬的恆星殘骸,從而證實黑洞的存在。

這些恆星物質以超快速度環繞黑洞周圍,當它的溫度達到100萬攝氏度時,其亮度就可以被探測到,環繞黑洞的物質盤被稱為「吸積盤」,被認為是黑洞邊緣,一旦吸積盤通過,任何事物都無法逃脫,我們將它稱為「黑洞視界」。

原始黑洞

宇宙中黑洞的重要部分是由恆星在其最後生命階段消耗所有燃料的引力坍塌所導致的,它們被稱為「恆星黑洞」,事實上,並不是所有恆星在生命末期都會演變成為黑洞,當恆星核心質量低於2-3倍太陽質量時,恆星黑洞就無法形成。

也就是說,存在一個恆星質量最小閾值,低於該質量,恆星就不會坍縮形成黑洞,舉個例子,太陽在生命末期無法演變成一個黑洞,但是其他大質量恆星,像紅色超巨星參宿四,將不可避免地變成黑洞。

同時,還有其他一些黑洞被稱為「原始黑洞」,正如它們的名稱所示,這些黑洞是在大爆炸最初時刻形成的,也就是宇宙誕生之初的時期,理論上原始黑洞可以擁有任何等級的質量,它們的大小從亞原子粒子至半徑數百公里不等。

至於黑洞,超大質量黑洞幾乎不釋放輻射,而最小質量黑洞釋放的輻射最多,但是該現象是如何實現的呢?超大質量黑洞幾乎不釋放輻射,卻能捕獲一切事物,甚至包括光。

上世紀70年代中期,著名物理學家史蒂芬·霍金給出了答案,他假設在黑洞視界附近的量子效應可能會產生從黑洞逃逸的粒子,也就是說,不通過任何其他方式增加質量的黑洞將逐漸失去質量,最終蒸發消失。同時,霍金於1974年提出了黑洞輻射的概念,該概念是指以量子效應理論推測出的一種由黑洞散發出來的熱輻射。該理論能說明如何降低黑洞的質量而導致黑洞蒸散的現象。

黑洞輻射理論對於低質量黑洞更為明顯:一個100萬倍太陽質量的超大質量黑洞的蒸發時間比宇宙當前的年齡更長,然而,質量僅1000噸重量的黑洞會在46秒內蒸發消失。在黑洞蒸發的最後階段,它們會爆炸並產生大量伽馬射線(一種比X射線更強的輻射)。

捕獲原子大小的原始黑洞

那麼,在原子大小的黑洞完全蒸發之前,如何證明它們的存在呢?在近期對原子大小黑洞的研究中,科學家提出一種天體物理學假設,即這些微型黑洞可能被某個超大質量黑洞捕獲,當原子大小的黑洞接近特大質量黑洞時,從地球角度可探測到的黑洞輻射比例逐漸減少,直到縮小至一束光大小。

來源:cnBeta

應用材料突破邏輯晶片布線方法 可擴展到3納米節點上

全球最大的半導體設備和服務提供商應用材料(Applied Materials, Inc.)今天宣布,已經成功設計了先進邏輯晶片布線的新方法,使其能夠擴展到3納米節點及以上。雖然尺寸縮小有利於電晶體的性能,但在互連布線方面卻恰恰相反:較小的導線具有較大的電阻,從而降低了性能並增加了功耗。如果沒有材料工程方面的突破,從 7 納米節點到 3 納米節點,互連通道的電阻將增加 10 倍,從而抵消了電晶體擴展的好處。

應用材料公司已經開發出了一種全新的材料工程解決方案--Endura Copper Barrier Seed IMS。它是一種集成材料解決方案,在高度真空環境下將 ALD, PVD, CVD, copper reflow, Surface treatment, interface engineering 和...

知情人士 台積電3nm工藝月產能在2023年將提升至10萬片晶圓

9月25日消息,據國外媒體報道,在芯片製程工藝方面走在行業前列的台積電,正在研發更先進的3nm和2nm工藝,其中3nm計劃在2021年風險試產,2022年下半年大規模投產。

在明年就將風險試產的情況下,外界也比較關注台積電3nm工藝投產之後的產能狀況。

知情人士透露,台積電目前正在按計劃推進3nm工藝在2022年下半年大規模投產,設定的產能是每月5.5萬片晶圓。

但知情人士也透露,5.5萬片是投產初期的月產能,隨後就將逐步提升,2023年的月產能將提升到10萬片晶圓。

在最近兩個季度的財報分析師電話會議上,台積電CEO魏哲家都有談及3nm工藝,但兩次透露的都是量產時間及性能提升方面的消息,並未公布3nm工藝將在那一座工廠投產。

在8月份的台積電2020年全球技術論壇期間,他們也未透露3nm工藝方面的更多消息,因而目前還不清楚台積電將在哪一座工廠或哪些工廠,利用3nm工藝為相關的客戶代工芯片。來源:快科技

台積電確認正研發3nm和4nm工藝 功耗降低30%、2022年量產

在台積電第26屆技術研討會上,台積電不僅確認5nm、6nm已在量產中,且5nm還將在明年推出N5P增強版外,更先進的3nm、4nm也一並公布。

3nm是5nm的自然迭代,4nm理論上說是5nm的終極改良。

技術指標方面,3nm(N3)將在明年晚些時候風險試產,2022年投入大規模量產。相較於5nm,3nm將可以帶來25~30%的功耗減少、10~15%的性能提升。

4nm(N4)同樣定於明年晚些時候風險試產,2022年量產。對於台積電N5客戶來說,將能非常平滑地過渡到N4,也就是流片成本大大降低、進度大大加快。

當然,台積電不是唯一一家3nm廠商,三星的雄心更大,明年就想把3nm推向市場。而且在核心技術方面,三星的3nm將改用Gate-All-Around(GAA,環繞柵極晶體管),台積電則是堅守FinFET(鰭式場效應晶體管)。

三星比較雞賊,3nm對比的是7nm,號稱可將核心面積減少45%,功耗降低50%,性能提升35%。

作者:萬南來源:快科技

投資200億美元與三星決戰 台積電3nm技術論壇延期

由於受到全球疫情影響,台積電宣布原本4月29日在美國舉行的技術論壇延期,這次論壇本來是要公布台積電3nm技術的。

台積電去年宣布投資200億美元推進3nm工藝,目前已經在前期的建廠准備中,預計最快2022年量產,比之前預告的2023年量產要提前一年。

在3nm節點上,三星已經搶先一步,去年就宣布了3nm GAE工藝,將在3nm節點放棄FinFET晶體管,轉向GAA環繞柵極晶體管工藝,比7nm工藝,3nm GAE工藝號稱可將核心面積減少45%,功耗降低50%,性能提升35%。

台積電的3nm很可能沒三星這麼激進,之前的消息稱3nm節點會繼續用FinFET工藝,在第二代3nm或者2nm節點才會升級到GAA晶體管技術。

原本3nm工藝的秘密會在4月29日的台積電美國技術論壇上揭秘,不過現在要推遲到8月24日了,在聖克拉拉舉行技術論壇,8月25日則會緊接着舉行開放創新平台論壇。

作者:憲瑞來源:快科技