Tag: PCIe 5.0

全球首個 Microchip推出PCIe 5.0交換機

數據分析,自動駕駛和醫療診斷等應用正在推動對機器學習與超大規模計算基礎架構的需求。據techpowerup消息,Microchip今天宣布推出全球首個PCIe 5.0交換器解決方案——Switchtec PFX PCIe 5.0系列,它的出現使密集計算,高速網絡和NVMe存儲的互連性能提高了一倍。

圖形處理單元(GPU),中央處理單元(CPU)和高速網絡適配器持續推動對高性能PCIe基礎架構的需求。Microchip推出了世界上首個PCIe 5.0交換機,使PCIe Gen 4互連鏈路速率提高了一倍,最高支持32GT/s,以支持要求更苛刻的下一代機器學習平台。

Switchtec PFX PCIe 5.0交換機系列包括高密度,高可靠性的交換機,支持28通道至100通道以及多達48個非透明橋(NTB)。Switchtec技術設備支持高可靠性功能,包括熱插拔和意外插入以及安全啟動身份驗證。PCIe 5.0數據速率為32GT/s,信號完整性和復雜的系統拓撲構成了重大的開發和調試挑戰。

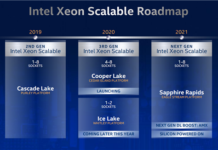

Debendra Das Sharma博士說:「英特爾即將推出的Sapphire Rapids Xeon處理器將實現PCIe 5.0和Compute Express Link,運行速度達到32GT/s,以提供客戶需求的低延遲和高帶寬I/O解決方案。」

來源:遊民星空

PCIe 5.0時代來了Microchip全球首發切換開關

PCIe 4.0已經逐漸普及,PCIe 5.0即將登場,PCIe 6.0躍躍欲試……PCIe標準這幾年的步伐不可謂不快。

眼下,PCIe 5.0標準還沒有正式出爐,但是各方面的支持已經逐步啟動,處理器方面Intel下一代至強Sapphire Rapids已確認支持,Intel Alder Lake 12代酷睿、AMD Zen4架構也都有極大概率。

其他生態配件方面,IC廠商Microchip是相當積極,去年底首先發布了PCIe 5.0重定時器(Retimer),現在又搶先帶來了PCIe 5.0切換開關(Switch),依舊隸屬於Switchtec PFX系列產品線。

目前,Microchip也是唯一能提供這兩種PCIe 5.0方案的廠商。

為什麼重定時器、切換開關如此重要?因為隨着PCIe的不斷演化,速率每一代都在提高,但代價是不斷犧牲傳輸距離和范圍(類似Wi-Fi/5G頻段越高速度越快但距離越短)。

PCIe 5.0如果不依賴中繼器(Repeater)等的輔助,要想跑出全速率,就只能在CPU近距離范圍內內部署少數幾個設備,在服務器、數據中心里完全不夠用。

Microchip連續推出的PCIe 5.0重定時器、切換開關,就能讓平台在更大的范圍、更遠的距離部署更多的PCIe 5.0設備,而且都能保持高速率傳輸。

新發布的PCIe 5.0切換開關支持28條至100條不等的PCIe 5.0通道,可以拆分到最低x2、x1通道配置,並支持最多48個非透明橋(NTB)。

該方案初期主要面向機器學習加速器、高速網卡等對於多通道高速PCIe有迫切需求的設備。

Microchip PCIe 5.0切換開關現已送樣給特定客戶,包括100通道的開發板套件。

作者:上方文Q來源:快科技

不只16核24線程 Intel 12代酷睿PCIe 5.0安排上了

2021年是Intel CPU的一次爆發,1月初會發布11代酷睿桌面版,代號Rocket Lake-S,14nm 8核16線程,年底的時候則會有12代酷睿,代號Alder Lake-S,

16核24線程這樣奇特的配置源於Alder Lake的架構,將會首次使用大小核設計,類似ARM的big.LITTLE那樣,內部由8個高性能大核、8個低功耗小核組成,其中大核支持SMT超線程,所以是24線程。

除了架構上的大改,Alder Lake的IO技術也會大升級,Intel這一次不會保守了,先進技術一次補足,記憶體會升級到DDR5,同時還有最新的PCIe 5.0,如果AMD的Zen4來得晚一點,那Alder Lake可能就是首發PCIe 5.0了。

最新消息顯示,Alder Lake處理器至少會有一條PCIe 5.0 x8通道,還有2個PCIe 4.0 x4通道,前者可能是用於顯卡,速度等效於PCIe 4.0 x16了,性能足夠未來的顯卡使用。

PCIe 4.0通道則有可能是給磁盤、網卡等設備用的,畢竟明年出PCIe 5.0 SSD的可能性不大,PCIe 4.0硬盤還會是高端的主流。

作者:憲瑞來源:快科技

SSD性能再次翻倍 群聯表態明年推出PCIe 5.0主控

去年AMD的銳龍3000處理器及X570平台發布時,首發了PCIe 4.0,這是首次由AMD帶領業界推出PCIe生態,群聯也在當時同步推出PCIe 4.0主控,使得SSD性能超過了5GB/。

前不久,,主控PS5018-E18,讀寫、性能雙雙超過7GB/,最高7.4GB/,是目前唯一讀寫性能雙雙達到7GB/的SSD主控。

對於未來的PCIe硬盤發展,群聯董事長潘建成日前在采訪中談到了他們的路線圖。

首先是主控工藝,目前還是28nm工藝的,12nm工藝的主控已經量產,就是PS5018-E18這一款,本季度正在客戶驗證中。

到了2021年,群聯也會推出PCIe 5.0標準的SSD主控,其性能會比PCIe 4.0再次翻倍。

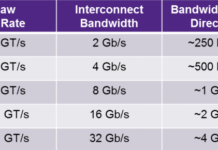

根據PCIe 5.0的技術標準,x1通道將達到32Gbps的速度,PCIe 5.0 x4就有128Gbps的帶寬,折合16GB/的速度。

作者:憲瑞來源:快科技

PCIe 4.0與NVMe碰撞 SSD再度挑戰速度極限

經過數十年的發展,用戶們所能接觸到的硬盤產品品類越來越豐富。

從早年的機械硬盤到SSD,在我們的認知中,硬盤的速度似乎在一直增長,而我們能夠獲得的最高速度上限也不斷地水漲船高。

速度的未來沒有上限,但是每一代的標準確實有它的極限,對速度的要求推動着廠商們不斷探索着硬盤的極限。

那麼制約硬盤速度的因素到底有哪些呢?考慮到當下機械硬盤的式微,本文就以固態硬盤為例進行探討。

SSD,全稱為Soild?State?Drive,也就是大家常說的固態硬盤,是當下普通用戶所能接觸的最為普遍的存儲設備之一。

它被廣泛地應用於PC產業,幾乎每一台筆記本電腦、整機在出廠時都已經搭配好了固定的存儲配置。

它主要包括以下幾個部分:控制器、記憶體、閃存顆粒等。這幾個部分各司其職,是作為SSD本質速度的保證。

從各自的功能來看,控制器主要提供外部主機接口、內部閃存管理接口,並通過內嵌的芯片來運行SSD固件,管理SSD的存儲地址空間、閃存物理空間,同時兼顧垃圾回收、磨損均衡等作用。

閃存是存儲信息的實體,閃存顆粒分布在SSD的電路板上,為SSD提供存儲空間。

但除此之外,對應的協議和標準也是決定SSD性能發揮的重要部分。

本文也將從控制器、閃存、協議以及接口四個方面淺談制約SSD速度的因素。

PCIe 4.0淺析

從定義上來講,我們通常所說的PCIe實際上是周邊設備高速互聯的英文縮寫,英文全名為Peripheral Component Interconnect Express。

PCIe標準主要用於連接顯卡、網卡、固態硬盤以及各種其他非CPU組件的統一接口標準,而PCIe標準同時也是目前我們能夠在PC上獲得的速度最快的鏈接標準。

PCIe接口的速度決定了所有這些外部組件與CPU的數據交換速度。

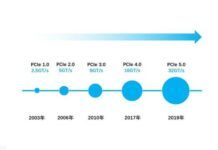

從PCIe標準出現到現在最新的標準已經來到了4.0時期。

理論上來說,PCIe 4.0 x 16接口最大帶寬(速率)是32GB/,不過固態硬盤用不到這個接口,SSD所能接入的PCIe 4.0×4接口的帶寬也能達到8GB/。

盡管此前被不少媒體唱衰,PCIe 4.0還是頂住了壓力。市場與廠商們的反映證明了PCIe 4.0並不會被拋棄,哪怕是行業巨頭英特爾對此響應平淡,一副極不情願的樣子。

此前有消息稱英特爾似乎有「跳過PCIe 4.0直接進入PCIe 5.0「之意,從目前的情況來看,PCIe 4.0仍是大家通往PCIe 5.0的必經之路。

最近一個時期,採用PCIe 4.0的設備突然多了起來,包括已經各種斷貨的剛剛發布的NVIDIA?RTX?30系列顯卡。

NVMe:PCIe接口的好搭檔

NVMe全稱Non-Volatile Memory express,即非易失性存儲器標準,這是一種建立在M.2接口上的專門為閃存類存儲設計的一種協議。

實際上NVMe標準誕生已經八年之久,而消費級NVMe產品廣泛上市才是近兩三年的事情。

2011年,NVMe標準正式出爐。

2017年5月,NVMe升級到1.3版本,而目前市場上符合NVMe 1.3標準的SSD可以說基本上是擁有最強性能的高端SSD。

支持1.3版本標準的固態硬盤在寫入壽命和讀寫速度上都有了全方位的提升,功耗也得到了更好的控制,更加符合高端玩家對硬盤壽命和速度的追求。

作為使用PCIe通道SSD的一種規范,支持NVMe協議的SSD具有低延時、速度快、功耗低以及兼容並行性好等優勢。

NVMe協議的優勢在於原生PCIe通道與CPU直連可以免去外置控制器與CPU通信所帶來的延時,同時大大提升了SSD的IPOS性能。

控制器:千軍易得一將難求

常用SSD的用戶一定深有體會——有一個好的控制器是多麼的重要。

主控,顧名思義是控制整個固態數的硬件,固件是儲存在主控中的軟件,主控負責運行這個固化的軟件,發出固件算法操作請求實際讀取、寫入和刪除數據、執行垃圾回收和耗損均衡算法等任務,以保證SSD的速度和整潔度。

根據SSD的運行原理,SSD由控制器將存儲單元連接到電腦,主控可以通過若干個通道並行操作多塊閃存顆粒,提高底層的帶寬。

這就意味着,能夠同時並行處理更多隊列的主控將使SSD擁有更快的速度。以三星剛剛發布的980 PRO為例,它所搭載的是三星自家全新的Elpis主控。

官方表示這款主控可同時處理128個I/O隊列,比起前代970 EVO Plus的Phoenix主控足足提高了四倍。

一個隊列可以包含64000個命令集,這意味着總共128個隊列可以處理超過800萬個命令。

為了在不損害功率效率的情況下滿足現代用戶對高性能的需求,基於極其精細的8nm工藝打造,三星用料很足。不少採用同樣品質顆粒的SSD往往就是輸在沒有足夠強大的控制器上。

閃存:承載數據的基礎

固態硬盤使用的NAND閃存顆粒主要有SLC、MLC、TLC、QLC以及3D?NAND(多層數存儲)。

作為新興閃存類型的3D?NAND擁有更強的存儲性能,它能在單位面積堆疊更多的存儲單元,在降低每bit成本上很有優勢。

從目前的市場反應來看,不少消費者談「TLC」色變。實際上,受到種種因素的限制,未來將會有更多的產品採用TLC甚至QLC顆粒。

要知道三星直到去年還在使用MLC顆粒做SSD,是時業界TLC顆粒的產品早已鋪開。

相較於SLC以及MLC,TLC飽受詬病的方面大都集中於它的讀寫壽命大大縮短。

根據三星關於NVMe SSD用戶的統計數據,有99%的用戶寫入少於156 TBW,有99.7%的用戶寫入少於600...

5nm Zen4要首發PCIe 5.0了?AMD表態 正在遷移生態

2019年的銳龍3000處理器升級了Zen2架構,同時還帶來了一項重要技術升級——首發了PCIe 4.0。在下一步AMD可能就首發PCIe 5.0了,官方表示正在遷移生態系統。

在以往的PCIe技術上,通常是Intel帶頭跟進,而在PCIe 4.0上AMD率先出招,在EPYC服務器、銳龍3000處理器上首發,而Intel之前的論調都是PCIe 4.0沒什麼用。

與PCIe 3.0相比,PCIe 4.0的速率提升到了16GT/,翻了一倍,對於PCIe 4.0技術的優勢,AMD給出了三個技術優點:

·速度更快,x16雙向帶寬達到了32GB/,是PCIe 3.0的兩倍。

·向下兼容,PCIe 4.0也能兼容PCIe 3.0設備。

·更多連接,PCIe 4.0帶寬高,1條頂2條,可以連接更多設備而不需要擔心性能下降。

不得不承認,AMD在PCIe 4.0上的首發雖然耗費了不少資源,但確實扭轉了形象,成為技術領導者了,PCIe 4.0硬盤現在主要就是用在AMD平台上了。

再往下就是PCIe 5.0,它的帶寬比PCIe 4.0再次翻倍,不過標志制定好了,現在還沒有x86支持。

AMD是否會再次首發PCIe 5.0?CTO Mark Papermaster日前在接受采訪時沒有明確回應,不過他們強調目前正在遷移生態系統以便支持PCIe 5.0。

此外,AMD不僅會改進現在開發中的核心(指的應該是Zen4了),IO、存儲控制器等單元也會針對PCIe 5.0進行改造。

毫無疑問,AMD的5nm Zen4處理器鐵定會上PCIe 5.0,不出意外還會有DDR5記憶體,全面升級。

當然,AMD是否能夠如期首發PCIe 5.0還不好說,因為Intel這邊也會加快進度,,就看兩家誰的進度更快了。

...

如何判斷電腦是否支持PCIe 4.0?一文看懂

很多大家已經了解了PCIe 4.0的概念,但是對於自己的電腦是否能支持PCIe 4.0還是有些疑惑,是不是只要一個支持PCIe 4.0的固態就能享受PCIe 4.0的帶寬呢?

那麼本次極速鯊課堂就給教大家如何判斷電腦是否支持PCIe 4.0。

首先從參數外的角度再給大家科普一下PCIe 4.0。我們都知道PCIe 4.0是一種總線協標準,但他不是單一種類硬件的技術表現,而是一種行業規范,跟手機的5G有點像。

廠商會根據這種規范去做出相應的產品,而生產出的產品只要能夠達到PCIe 4.0規范下帶寬的要求,那麼就可以說這款產品支持PCIe 4.0。

在電腦中,包括PCIe 4.0在內的PCIe通道都是由CPU管理的。

也就是說,如果你的電腦想要使用PCIe 4.0,那麼首先要滿足的條件就是CPU能夠支持PCIe 4.0。

如果你的CPU不支持PCIe 4.0,就算你用的固態支持PCIe 4.0,最後也達不到PCIe 4.0的速率,最多也只是PCIe 3.0的速率。

目前桌面端市場支持PCIe 4.0的CPU只有AMD的三代銳龍以及即將推出的Zen3處理器,英特爾暫時還沒有,不過英特爾預計在明年的新品上會推出支持PCIe 4.0的處理器。

所以現在就想體驗PCIe 4.0的用戶,只能選擇AMD的三代銳龍平台。

當然,光有個支持PCIe 4.0的CPU還不行,想要真正使用PCIe 4.0我們還需要一個載體,那個載體當然就是主板了。

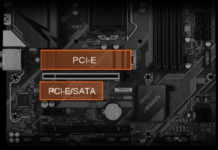

在主板上會用兩種接口來輸出PCIe 4.0,一個是M.2接口,另一種是顯卡插槽。

但與CPU一樣,也不是所有主板都支持PCIe 4.0,而是需要與三代銳龍相呼應的B450、B550、X470以及X570芯片組的主板才能支持PCIe...

Intel 10nm+++至強細節 56核心、DDR5記憶體、400W功耗

,Intel首款採用10nm工藝的至強服務器平台「Ice Lake-SP「,發布時間從原定的今年第四季度推遲到了明年第一季度。

它和已發布的Cooper Lake都隸屬於第三代可擴展至強,分別面向單路/雙路、四路/八路市場,最多38核心76線程、八通道DDR4-3200記憶體、64條PCIe 4.0,熱設計功耗最高270W。

,官方此前已確認它將在2021年晚些時候推出,

今天,外媒AdoredTV獨家拿到了Sapphire Rapids的詳細參數。

有意思的是,曝光後很快被Intel查了水錶,以「不准確」為由要求撤掉,但不解釋具體哪里不准確,AdoredTV因此拒絕撤稿。

Sapphire Rapids將採用最新的10nm+++工藝,也就是剛發的Tiger Lake 11代移動版酷睿那一套,融入SuperFin晶體管技術。

CPU架構升級為Golden Cove,也就是和Alder Lake 12代桌面酷睿同款,繼續提升IPC性能,並恢復支持Bfload16機器學習指令,強化AI人工智能。——Cooper Lake已支持該指令,但是接下來的Ice Lake又不支持。

核心數最多56個(112線程),但是很有可能還隱藏了4個核心,也就是總共應該有60核心120線程。

為什麼這麼做?很簡單,10nm+++工藝面對如此多核心,良品率暫時還上不去。

有趣的是,Sapphire Rapids將採用MCM多芯片封裝設計,內部同時整合最多4個小芯片,每一部分最多14核心(外加一個可能隱藏的),組成總計56核心,但不清楚是否會有AMD霄龍那樣的獨立的I/O Die。

同時封裝集成HBM2e高帶寬記憶體,配合4個小芯片最多4個堆棧,每個最大容量16GB,合計最多64GB,帶寬高達1TB/。

Sapphire Rapids將會首次支持PCIe 5.0總線,高端型號最多80條通道,其他型號最多64條,同時支持CXL高速互連總線協議。

另一個首發支持的是DDR5記憶體,頻率最高4800MHz,繼續八通道,但最大支持容量暫時不詳,同時繼續支持傲騰持久記憶體。

DDR5記憶體、HBM2e記憶體可以並行使用,支持緩存、混合多種模式。

熱設計功耗最高達到驚人的400W,部分型號300W。

相比之下,AMD霄龍的熱設計功耗最高為280W,Intel二三代可擴展至強普通型號最高250W,雙芯封裝的56核心則同樣是400W,不過現在是14nm。

Sapphire Rapids將在2021年底推出,對手將是AMD再下一代霄龍「熱那亞「(Genoa),Zen 4架構,同樣支持PCIe 5.0、DDR5,並採用台積電5nm工藝製造。

而下一代霄龍「米蘭」有望在今年晚些時候或明年初推出,7nm工藝,Zen 3架構,桌面銳龍5000系列的同門大師兄。

- THE END...

Intel 12代酷睿細節 大小16核心、DDR5記憶體、PCIe 5.0

Intel桌面處理器領域,Rocket Lake 11代酷睿還沒來,Alder Lake 12代酷睿就頻頻露面,Meteor Lake 13代酷睿甚至都已經上路了。

現在,NotebookChech披露了Alder Lake的大量細節,可謂從里到外煥然一新,不能不讓人期待。

從目前的資料看,Alder Lake至少有Alder Lake-S、Alder Lake-P兩個子系列,但不同於目前的S系列僅限桌面,這次可能也會橫跨移動版。

Alder Lake將採用大小核混合設計,類似手機上的ARM big.LITTLE,其中大核心代號Golden Cove(GLC),也就是現在Tiger Lake Willow Cove(WLC)的升級版,小核心代號Gracemont(GRT),也就是現在Tremont的升級版。

Intel此前也曾在Lakefield上做過實驗,結果確實能大大節省功耗、提高能效,只是性能發揮還有限,畢竟在PC領域還沒有過這種設計,無論硬件協調還是系統、軟件調度都需要深入優化。

Alder Lake-S系列將有最多8個大核、8個小核,熱設計功耗最高125W,三級緩存最多30MB;Alder Lake-P系列則是最多6個大核、8個小核,三級緩存最多24MB。

其中大核心都支持超線程技術,小核心不支持,也就是在用戶看來,Alder Lake-S會有最多16物理核心、24個邏輯核心。

有趣的是,Alder Lake-S系列可能也會用於筆記本,BGA整合封裝,熱設計功耗最高控制在65W。

目前還不清楚是否會有用於遊戲本的Alder Lake-H,又或者直接用Alder Lake-S來做遊戲本。

GPU核顯方面,Alder Lake會集成Xe...

從PCIe 3.0到PCIe 4.0 三星980 PRO的性能蛻變

隨着三星980PRO PCIe4.0 SSD的正式推出,關於PCIe4.0技術和產品成為了存儲行業時下最為熱門的話題。

那麼,PCIe4.0究竟代表着什麼?從PCIe3.0到PCIe4.0,三星品牌存儲又在產品端進行了哪些技術和體驗的創新和迭代?

想要解答以上問題,我們需要追根溯源,簡單回顧關於PCIe的歷史和變革,了解PCIe4.0帶來的時代意義和價值。

關於PCIe總線的演變

所謂的PCIe,全稱為PCI-Express。

它實質上是一種高速串行計算機擴展總線標準,類似的總線標準還有諸如早期的MCA、PCI都屬於這類協議。

只是隨着技術發展和需求的變化,擁有着高速串行、點對點雙通道、高帶寬傳輸等突出特點的PCIe協議,最終脫穎而出,成為了時下最為主流的計算機總線標準。

至於在接口形式上,PCIe主要有兩種,一種是尺寸較為小巧的M.2接口,另一種則是標準的PCIe插槽,二者全都集成在主板之上。

根據帶寬容量的不同,以及技術的迭代,以及應用層級方面,PCIe總線又出現了分支和進化。

先說帶寬,基於PCIe串聯計算機的容量大小,同一級別的PCIe插槽之間存在着性能差異。

以主流的PCIe3.0為例,簡單可以分為PCIe x1/PCIe x2/PCIe x4/PCIe x8/PCIe x16等不同帶寬,這些「x1/x2「等數字的背後,對應着接口性能差異。

以PCIe3.0 x1和PCle3.0 x16為例,PCIe3.0 x1的標準性能約為1GB/,而同樣是PCIe 3.0協議,X16的標準性能則高達16GB/。

再說說技術迭代,PCIe作為總線協議和標準,歷經多年的發展和變革,從起初的PCIe 1.0,逐步在性能上大跨步發展,直到今天的PCIe4.0的誕生。

技術的迭代帶來了恐怖的性能,根據官方提供數據,對比於初代的PCIe1.0帶寬(X1為250MB/),最新的PCIe4.0的帶寬(以X1為例)達到了2GB/,提升了近8倍。

最後在應用層面,由於PCIe高速串聯計算機,提供更高性能優勢,許多硬件產品都能,更都想通過PCIe總線的方式,進行串聯,以發揮硬件的最高性能。其中,顯卡和固態硬盤是其中的代表產品。

PCIe4.0 SSD存在的必然性

剛才說到固態硬盤和PCIe之間的聯系,是源於PCIe總線串聯計算機的巨大性能優勢。

其實在固態硬盤發展的早期,SATA接口才是行業的主流,一方面源於製程工藝,沒辦法開發出性能和功耗能夠完美契合的主控和顆粒產品;

另一方面,則是SATA接口的絕對性能能夠滿足人們日常的存儲需求。

隨着存儲需求的變化和製程工藝的突破,固態硬盤性能一日千里般的躍進和發展,傳統的SATA接口在協議上弊端逐漸顯現出來,最大理論性能600MB/,已然無法適配不斷狂奔的存儲需求和技術演進。

於是以三星品牌存儲為代表的存儲行業,開始引入PCIe 3.0接口,並推出了全新的NVMe傳輸協議,打破了接口協議的束縛,讓固態硬盤產品的性能達到了3.5GB/的標準。

然而技術的進步和存儲需求的徹底爆炸,PCIe3.0協議下、3.5GB/的絕對性能也漸顯頹勢,業界期待着帶寬更大,性能更強的PCIe協議的到來。

所以在需求和技術的雙重裹挾下,PCIe4.0以及隨之而來的高性能PCIe4.0固態硬盤開始嶄露頭角。

三星品牌存儲在PCIe4.0時代的創新

作為行業領先的存儲廠商,三星品牌存儲也在積極參與和擁抱PCIe4.0時代,並在產品和體驗上進行了多維度的創新,其中代表性產品便是不久前發布的三星980PRO PCIe4.0固態硬盤。

這是三星品牌存儲推出的首款全面支持PCIe4.0協議的高性能固態硬盤,熟悉三星存儲產品的朋友們都清楚,三星旗下存儲產品大致可以分為PRO/EVO/QVO三個序列,並根據定位和價格差異,依次遞減;

換句話說,能夠被冠以PRO序列的產品,可以說是三星品牌存儲旗艦中的旗艦了,這也從側面反映了三星品牌存儲對於PCIe4.0技術的重視程度。

除了產品定位的高標準高規格之外,就三星980PRO產品本身而言,三星也為之進行了諸多技術的創新和突破,筆者簡單將它分拆為三個維度的創新,即主控創新、閃存創新以及性能創新。

主控創新

PCIe4.0協議的到來,對於固態硬盤產品而言,尤其是主管固態硬盤內部數據處理,編譯以及運轉的主控芯片而言,是前所未有的挑戰。

協議帶寬的巨大提升,相對應的需要硬盤主控能夠同時並行和處理更多的數據指令,以滿足高吞吐,實現高效的數據傳輸。

為了應對PCIe4.0巨幅的性能提升,三星品牌存儲在三星980PRO上首次搭載了基於ARM架構的、重新設計和編譯的新一代主控芯片Elpis,Elpis源於希臘語,中文讀音「厄爾庇斯」,中文直譯則是「(希望)女神「。

Elpis主控採用三星自研的全新8nm製程工藝,全面支持PCIE4.0協議,同時能夠滿足下一代開發、計算等需求,更為關鍵的是,它能夠支持128隊列並行工作,支持128個I/O隊列同步進行數據處理。

相較於PCIe3.0時代,三星主流Phoenix主控支持的32隊列,提升了接近400%;

用一組更為直觀的數字來驗證三星新主控的強啊之處,根據設計製程,在單個隊列下,能夠處理超過64000命令集,這也就意味着三星Elpis主控內部的128個隊列,可以同步處理最高超過800萬個命令。

這樣的性能倍增,能夠滿足PCIe4.0協議下對於主控性能的苛刻需求,進而保證了三星980PRO的性能表現。

同時,Elpis主控芯片,還能夠完美兼容PCIE3.0,並且在性能上有着上佳的表現,甚至超過稱霸PCIE3.0世代的970EVO Plus和970PRO。

根據官方提供的數據,在PCIE3.0帶寬下,三星980PRO的最大連續讀取性能達到3500MB/,基本和970EVO Plus持平;

在最大連續寫入性能方面,達到了3450MB/,甚至超過了三星970EVO Plus的官方測試水平。

閃存創新

高帶寬帶來高性能的同時,對於存儲數據的顆粒體質,同樣有了更高的需求。大規模和高速率的讀寫,意味着用於存儲數據的閃存顆粒需要在體質和性能上有着可靠和穩定表現。

三星品牌存儲同樣為了進一步釋放PCIe4.0固態硬盤的全部性能,也首次在三星980PRO上應用了第六代三星V-NAND閃存顆粒。

這一代閃存顆粒突出特點在於,充分利用三星獨創的「通道孔蝕刻」技術。

通過建立一個由100多個層組成的導電晶片堆棧,然後從上到下垂直穿孔,形成均勻的三維電荷阱閃存(CTF)單元,從而實現了在9x層單堆棧結構基礎上增加了大約40%的存儲單元。

同時,在性能表現方面,三星在內部結構上進行了電路優化,進一步提升了閃存顆粒的速度表現。

根據官方數據,對比第五代V-NAND技術,其寫入操作的時間少於450微秒(μs),讀取操作的時間少於45μs。

性能創新

全新主控和全新顆粒的應用,讓三星980PRO能夠完美發揮PCIe4.0協議帶來的巨大性能優勢。

根據筆者實際測試,三星980PRO PCIe4.0 SSD最大順序讀取速度超過了驚人的7000MB/,最大順序寫入速度同樣超過了驚人的5000MB/。

要知道PCIe4.0 X4的理論性能為8GB/,而三星980PRO超過7000MB/,幾乎接近理論性能最大值。

當然了,除了絕對性能,三星980PRO還在智能緩存方面進行了拓展,讓普通用戶在日常使用中體驗到三星980PRO的極致表現。

所謂智能緩存技術,三星為之冠名為智能TurboWrite技術,這一技術能夠可自動識別用戶的工作負載,並指定合適的SLC緩沖區;

也就是說,在這項技術加持下,三星980PRO內部生成了由固定默認空間+智能區域形成動態緩存區。

根據容量和型號不同,動態緩存區容量大小也存在差異。就1TB型號980PRO PCIE4.0 SSD的而言,三星為此配備了6GB的默認緩存區,以及高達108GB的動態智能緩存區。

也就是說,用戶在0-114GB這個寫入區間內,可以完美體驗到三星980PRO的絕對性能表現;

而實際上,對於大部分的普通用戶而言,單次的寫入量遠遠達不到100GB的量級,所以這樣的技術對於用戶而言,十分有意義的。

寫在最後

行業領頭羊的態度往往主導和決定了產業發展態勢,作為存儲行業的先行者,三星980PRO PCIe4.0...

PCIe 5.0 SSD硬盤2022年問世 4倍性能、7nm芯片工藝

去年群聯聯合AMD在X570平台上首發了PCIe 4.0主控芯片,現在已經在高端SSD中開始普及。群聯表示,2022年PCIe 5.0技術的SSD主控問世,同時製程工藝也會從28nm微縮到7nm。

在Q2季度財報會上,群聯董事長潘建成公布了他們在PCIe 4.0市場上的進展,28nm製程的PCIe 4.0主控芯片已經出貨150萬顆,工藝也進一步導入12nm製程,目前的進度僅落後於業界一哥三星。

潘建成表示,群聯的12nm PCIe 4.0主控芯片將在8月份配合美國客戶首發,10月底開始量產,2021年還有至少4款定製版主控芯片問世。

再往後就要看下一代主控了,潘建成表示群聯未來的SSD主控將支持PCIe 5.0及Gen X,性能更強,能效更高。

同時,製程工藝也會大幅提升,從當前的28nm水平進入7nm節點,2021年導入,2022年正式推出。

與PCIe 4.0相比,,x1速率可達32GT/,x16帶寬可達64GB/,雙向帶寬128GB/。

用於SSD硬盤的話,通常是PCIe 5.0 x4,帶寬依然有16GB/,是目前PCIe 3.0硬盤的4倍多,PCIe 4.0硬盤的2倍多。

PCIe 5.0主控芯片最大的問題還要看生態系統,群聯搞定主控芯片不是問題,主要是AMD及Intel的處理器平台何時問世。

不出意外的話,2022年的時候AMD的Zen4處理器、,還有DDR5記憶體,與PCIe 5.0硬盤正好組成黃金搭檔。

作者:憲瑞來源:快科技

Intel對PCIe 4.0不再保守 PC及服務器全都上 PCIe 5.0明年上路

目前PC及服務器使用PCIe 3.0已經有八九年了,PCIe 4.0去年才隨着銳龍3000及EPYC 7002系列開始大規模落地,Intel之前對PCIe 4.0的態度比較保守,認為遊戲中沒多大用。今年不一樣了,,服務器中的Ice Lkae-SP也會升級到PCIe 4.0,下代PCIe 5.0也在路上了。

昨天Intel舉行了一次數據中心產品技術線上分享會,介紹了代號Cooper Lake的Intel第三代至強可擴展處理器、第二代傲騰可持久性記憶體等產品,多名Intel技術專家分享了Intel新一代處理器、記憶體在高性能計算、AI加速等方面的進展。

在之後的提問中,Intel技術專家也回應了有關PCIe 4.0的疑問,他確認了之前的傳聞,那就是Ice Lake-SP架構的新一代至強就會支持PCIe 4.0。

不僅很快推進PCIe 4.0,Intel技術專家還提到明年會支持更新的PCIe技術,這顯然是在指最新的PCIe 5.0了。

根據Intel之前公布的路線圖,下一代至強可擴展處理器就是10nm工藝的Ice Lake-SP了,該架構使用了全新的CPU內核Sunny Cove,去年已經在輕薄本處理器Ice Lake-U中應用。

至於支持PCIe 5.0的下下代至強處理器,,將支持1-8路CPU插槽,支持下一代深度學習加速指令AMX(高級矩陣擴展),大大提升AI訓練、推理性能。

除了PCIe 5.0之外,Sapphire Rapids(藍寶石激流)應該還會上DDR5記憶體支持,新一代平台技術規格要全面升級。

在此之前,Intel的11代酷睿Rocket Lake已經被曝光上了PCIe 4.0硬盤,如此一來Intel今年底到明年就會全面應用PCIe 4.0,PC及服務器市場都沒落下。

作者:憲瑞來源:快科技

鎧俠展示全新SSD形態 迎接PCIe 6.0、功耗可達28W

SSD的形態多種多樣,消費級市場上的SATA、PCIe、M.2大家都非常熟悉了,企業和數據中心領域還有U.2、SAS、E1.L、E1.S等不同設計,其中E1系列屬於Intel倡導發起的EDSFF(企業與數據中心SSD形態)家族,E1.L比較長,E1.S則比較短。

今天,鎧俠(原東芝存儲)宣布,已經開發完成下一代EDSFF E3.S形態的全新SSD,並開始出貨工程樣品。

E3.S是由SNIA SFF TA技術工作組完成標準制定的,是面向雲服務、企業數據中心的NVMe SSD新形態標準,一大特色就是針對PCIe 5.0乃至未來的PCIe 6.0做好了准備,擴展性更強,並在性能、散熱、功耗等方面都做了改進和統一,支持PCIe x4/x8通道,非常適合大容量、高密度的全閃存存儲陣列(AFA)。

另外,廠商還可以在硬盤上設計LED指示燈,方便隨時監控硬盤狀態。

鎧俠的E3.S SSD工程樣品基於其CM6 PCIe 4.0 SSD,2.5英寸規格,支持NVMe 1.4,用上新形態後同樣的主控、閃存下性能提升了大約35%,功耗則放開了40%,允許達到28W。

PCIe 5.0標準規范早已完成並發布,,I/O帶寬再次翻番達到64GT/,PCIe 6.0 x1單向實際帶寬8GB/,PCIe 6.0 x16單向帶寬128GB/、雙向帶寬256GB/,並加入全新的脈沖幅度調制PAM4,以及低延遲前向糾錯(FEC)和相關機制,以改進帶寬效率。

優惠商品信息>>作者:上方文Q來源:快科技

Intel拍胸脯 DDR5、PCIe 5.0明年見

因為種種原因,Intel的產品規劃這兩年調整非常頻繁,路線圖經常出現變動,無論是消費級還是企業級。

在近日與投資者溝通時,Intel公關總監Trey Campbell就保證說,將在今年第二季度末(最遲至6月底)發布代號Ice Lake-SP的下一代至強服務器平台,明年某個時候則會帶來Sapphire Rapids。

Ice Lake-SP將採用和移動端Ice Lake-U/Y系列相同的10nm工藝、Sunny Cove CPU架構,並更換新的LGA4189封裝接口,核心數量和頻率暫時不詳(據說最多38核心),但會引入PCIe 4.0總線,最多64條,而記憶體繼續支持DDR4,但是會從六通道擴充到八通道,頻率也有望提升至3200MHz。

Sapphire Rapids則會使用增強版的10nm+工藝,升級到更新一代的Willow Cove CPU架構,據說可達56核心112線程,並首次引入DDR5記憶體、PCIe 5.0總線,據說前者還是八通道,後者則有最多50條。

在桌面上,據說Intel Alder Lake(12代酷睿)也將引入DDR5記憶體,AMD方面則預計要等到Zen 4架構。

有趣的是,Ice Lake-SP之前其實還規劃有一套至強平台Cooper Lake,依然是14nm工藝,架構、技術規格也沒有太大變化,只要增強機器學習,而接口也是新的LGA4189。

這樣的設計自然無法吸引OEM客戶,Intel也不得不縮減其規模,僅供四路、八路市場,而這個市場是非常非常小的。

作者:上方文Q來源:快科技

賽靈思發布史上最強ACAP芯片 7nm、還有PCIe 5.0

2018年10月16日,FPGA大廠賽靈思(Xilinx)在北京的「Xilinx開發者大會 」(XDF)上,發布了全球首款自適應計算加速平台(ACAP)芯片系列Versal,並發布了AI Core系列和Prime系列。去年,這兩個系列產品也已經成功推向了市場。

今天(3月11日),賽靈思舉行線上發布會,正式推出了Versal ACAP產品組合的第三大產品系列—— Versal Premium。

賽靈思認為,隨着來自多元化應用和工作負載(比如智能設備、視頻流、物聯網、企業等)的數據爆炸性增長,這也使得核心網正面臨巨大的壓力。

數據顯示,2019年區域流量容量提升了100倍,帶寬年復合增長率達到了51%。

隨着數據的爆炸性增長,對於整個網絡基礎設施提出了更高的要求,這也加速驅動了網絡轉型。而在這個轉型過程當中,我們可以看到三個趨勢:

1、下一代核心網絡加速擴展。

根據ABI Research數據顯示,2020年-2024年5G核心網年復合增長率預計為313%。

2、安全已成為網絡運營商最高優先級的問題。

ISH Markit的研究顯示,對於網絡運營商來說,過去性能、擴展性、成本一直是運營商主要關注的問題,而現在,安全性已經成為了網絡運營商最為關注的問題。

3、隨着數據的增長,對於計算能力與帶寬的需求越來越高。

我們可以看到,現在網絡的帶寬的增長非常的迅速,但是,隨着摩爾定律的放緩甚至是趨於消亡,芯片的計算能力越來越跟不上了。根據賽靈思的估算,2018年之時,服務器端口速度的增長已經超過了摩爾定律對於服務器CPU性能所帶來的增長,並且差距正在進一步擴大。

在此背景之下,為了加速運營商的網絡轉型,賽靈思推出了Versal Premium ACAP系列產品,其具備了高度集成且功耗優化的網絡硬核,是業界帶寬最高、計算密度最高的自適應平台。專為在散熱條件和空間受限的環境下運行最高帶寬網絡,以及需要可擴展、靈活應變應用加速的雲提供商而設計。

Versal Premium ACAP系列詳解

我們都知道,2018年賽靈思推出的Versal系列是業界首款自適應計算加速平台( ACAP ),是一個功能遠超常規芯片架構的革命性全新異構計算器件類別。而據賽靈思介紹,其去年就已經向客戶交付的Versal AI Core系列和Versal Prime系列,已經獲得了幾百家客戶的採用,反響很好,目前正在加速生產。

而此次賽靈思推出的全新Versal Premium則是Versal Prime系列的升級款版,是針對網絡基礎設施推出的旗艦級產品,採用台積電7nm工藝製程打造而成,融軟件可編程能力與動態可配置硬件加速、預制連接和安全功能為一體,為加快產品上市進程提供了強大引擎。

作為 Versal ACAP 的最新產品系列, Versal Premium 系列可提供比當前FPGA高達三倍的吞吐量,且擁有高度集成的軟件/硬件平台,內置了以太網接口、Interlaken和加密引擎,以打造快速、安全的網絡。該系列還提供了當前部署主流 FPGA 兩倍的計算密度,同時還面向持續擴展的多元化且不斷演進的雲工作負載及網絡工作負載,提供了靈活應變的能力。

Versal Prime系列

具體來說,與之前的Versal Prime系列相比,Versal...

從速度和通道說起 PCIe 4.0 SSD前途光明

無論承認與否,2019年對於整個DIY硬件行業來說,都是充滿驚喜和極具意義的一年。

這一年,AMD推出了全新的銳龍處理器和X570芯片組,讓PCIe 4.0 得以投入實用。

我們可以預見的是,基於PCIe 4.0 的全新高速帶寬,未來DIY硬件的性能將會迎來爆炸式增長。

可喜的是,這種變化正在加速來臨,與X570芯片組同時間誕生的PCIe 4.0 SSD,已經提前讓我們見識到了PCIe 4.0 的威力。

不難想象,PCIe4.0將是DIY硬件廠商、尤其是存儲廠商着重開辟的新藍海。

為什麼這麼說?在回答這個問題之前,我們需要知道PCIe 4.0究竟是什麼?它和PCIe 3.0有什麼區別?

從PCIe 1.0到2017年發布、但還沒有應用的PCIe 5.0,一共經歷了五代。

傳輸速率上,PCIe 4.0 的傳輸速率為16GT/s,比3.0 翻了一倍,雙向傳輸速度可達到64GB/s。

換一張圖,我們能夠更加直觀地比較PCIe 3.0和PCIe 4.0的速度差距。

註:PCIe通道可以同時進行雙向傳輸,故以上數據為PCIe通道單向傳輸速度,雙向傳輸需*2。

為什麼說PCIe 4.0是SSD發展的新藍海

目前,PCIe 3.0 X 16通道的速度高達32GB/s,這個速度應付當下的顯卡帶寬完全綽綽有餘。

那麼對於硬件廠商來說,為什麼還要着力發展PCIe 4.0呢?其中的原因,與傳輸通道和通道速度緊密關聯。

1、接口與傳輸通道的限制

SSD尚未誕生時,機械硬盤是市場的絕對主力,即使在當下,它也還是大容量存儲的首選。

不過由於結構的限制,機械硬盤的速度難以取得突破。目前性能較好一點的機械硬盤,連續讀寫速度一般在250/150MB/s左右。

而同樣採用SATA接口的SATA SSD,連續讀寫可達500MB/s,隨機讀寫更遠高於前者。

不過受接口和傳輸通道的限制,SATA...

新線路圖顯示Intel 2021年的Xeon將用上LGA4677插槽,支持PCIE 5.0

上個月從一家設計和生產連接傳感器產品的公司TE Connectivity處,我們提前得知TE Connectivity已經為Intel Ice

Lake-SP(ICL-SP)和Cooper Lake(CPL)處理器推出了LGA4189插座。現在該公司的最新線路圖上出現了一個新的插槽——LGA4677。

PC Watch的編輯Kazuki

Kasahara在其推特上放了一張他拍攝的照片,該照片上的線路圖顯示英特爾下一代企業級處理器的插槽將變為新的LGA4677插槽,根據時間軸,LGA4677插槽將設計為適用於英特爾的Sapphire

Rapids和隨後的Granite Rapids處理器。

據傳Sapphire Rapids基於10nm++工藝打造,將於2021年問世,而Granite

Rapids處理器則將基於7nm工藝並於2022年問世,這兩個家族都將位於Eagle

Stream數據中心平台,該平台很可能要使用的就是這次揭示的LGA4677插槽。

之前由泄露的消息表示Sapphire Rapids和隨後的企業級處理器將支持PCIE 5.0接口和DDR5記憶體,這次TE

Connectivity的線路圖幫助確認了「將支持PCIE

5.0接口」,不過DDR5記憶體則沒有證實。LGA4677插槽比LGA4189插槽多488個針腳,這些額外的針腳將使得英特爾能夠帶來新功能,比如對PCIE

5.0的支持以及新的互連技術等等,所以對於DDR5記憶體的支持也是很有可能的。

<p ...

PCIe 5.0首秀PCIe 4.0剛出生就落伍了?

PCIe 4.0產品正在紛紛面世,但是下一代PCIe 5.0已經迫不及待地走來,標準規范剛剛完成不到半年的它,已經得到了一批產品和技術的採納,比如Intel 10nm Agilex FPGA,比如CXL、CCIX、Gen-Z高速互連標準。

近日,芯片開發工具和硅片IP大廠新思科技(Synopsys)展示了自己的PCIe 5.0 CXL、PCIe 5.0 CCIX方案,這也是PCIe 5.0首次公開秀肌肉。

CXL、CCIX都是芯片間的互連協議,用於連接處理器和各種加速器(標量/矢量/矩陣/空間等架構),並保持低延遲的記憶體和緩存一致性,都面向異構計算架構。

CXL 1.0/1.1、CCIX 1.1版本都引入了PCIe 5.0,利用其單鏈路32GT/s高帶寬的優勢,並原生支持不同的鏈路帶寬。

新思科技最近推出的DesignWare CXL IP方案可採用16nm、10nm、7nm工藝製造,支持16個PCIe鏈路,包括CXL 1.1控制器、硅驗證的PCIe 5.0控制器、硅驗證的32GT/s PHY物理層、RAS、VC驗證IP。

DesignWare CCIOX 1.1 IP方案尚未正式發布,不過從展示來看,其功能已經完備,PCIe 5.0已經很好地融入其中。

兩套展示方案都基於FPGA和特殊設備,而沒有使用真實的芯片,所以還只是功能上的演示,距離實際產品尚還需要一些時日,但這無疑表明,PCIe 5.0會比我們想象的來得更快。

作者:上方文Q來源:快科技

高速互連Gen-Z 1.1標準公布 加入PCIe 5.0

AMD剛剛引領開啟了PCIe 4.0時代,下一代的PCIe 5.0標準就已經開始上路了。

不久前,Intel出貨了支持PCIe 5.0的新款Agilex FPGA,並採用10nm工藝。現在,Gen-Z聯盟又發布了這一高速互連標準的最新1.1版本,也加入了PCIe 5.0。

PCIe 3.0標準還是遙遠的2010年發布的,所以在制定新標準的時候,PCI-SIG組織同步規劃了PCIe 4.0、PCIe 5.0,其中後者已在今年5月底完工,這意味着產業隨時可以利用它打造相關技術和產品了。

Gen-Z其實是一堆行業巨頭不滿意Intel技術壟斷和演進的情況下,合作搞出的新型高速互連標準,AMD、ARM、博通、Cray、戴爾EMC、HPE、華為、IBM、聯想、Mellanox(NVIDIA)、美光、紅帽、三星、希捷、SK海力士、西數、賽靈思等等都在其中。

Gen-Z面向數據中心和服務器市場,是一種以記憶體為中心的總線結構式協議,具備高帶寬、低延遲、先進工作負載、良好兼容性和經濟性等優點。

Gen-Z 1.0標準採用PCIe物理層和修改的IEEE 802.3以太網電氣層標準,但在物理層上只定義了PCIe 4.0,因此每通道速度最快只有25GT/s,要想充分利用標準的全部性能,也必須滿足PHY物理層面的所有規定。

Gen-Z 1.1則引入了PCIe 5.0,每通道速度提高到32GT/s,同時在比較寬松的技術限制下,就可以實現Gen-Z-E-PAM4-50G-Fabric鏈接,原始數據率53.125GT/s,一切都以達到更高的傳輸速度、更低的延遲為目標,畢竟這也是該標準的初衷。

更多技術細節這里就不具體展開了,相信未來也會有越來越多的PCIe 5.0技術和產品迅速出現。

至於說過渡性質比較大的PCIe 4.0是不是就沒價值了,當然也並非如此,畢竟全面商用和普及PCIe 5.0仍需時日,對於很多渴求高帶寬的高性能計算、網絡應用來說,PCIe 4.0已經可以解決燃眉之急,後續過渡到PCIe 5.0也非常方便。

作者:上方文Q來源:快科技

Intel推出CXL總線協議:為數據中心,高性能計算打造

Intel在昨天聯合眾廠商一起推出了針對數據中心,高性能計算,AI等領域的全新的互聯協議Compute EXpress

Link(CXL),並正式發佈了CXL

1.0規范。這個協議擁有更高的帶寬,能夠讓CPU與GPU,FPGA或其他加速器之間實現高效,高速的互聯,能夠帶來更低的帶寬和更好的記憶體一致性。而該技術是建立在完善的PCIe

5.0的物理和電氣實現上的,不用通過專門設計的接口,簡化了服務器硬件的設計難度,降低了整體系統的成本。

Intel宣佈與阿里巴巴、戴爾EMC、臉譜、Google、HPE、華為、微軟聯合共同成立一個聯盟,來開發這個協議,用於消除CPU與加速器等計算密集型工作負載的瓶頸。而此次Intel扮演的角色與其在USB和PCIe開發中的角色一樣,

與聯盟成員共享技術成果,並共同持續開發。

與早前向USB推廣組織貢獻雷電3接口協議不同的是,這次Intel選擇自己成立聯盟並與聯盟成員共同開發。同時值得注意的是,這次宣佈CXL的時間點恰巧在NVIDIA宣佈正式收購以色列Mallanox公司之後。而Mallanox公司的業務就是為數據中心提供如infiniband這樣的高速傳輸協議。

此次Intel並沒有公佈更詳細的技術細節。而Intel聲稱將在今年上半年為聯盟成員提供第一代規范。此次CXL聯盟成員為服務器硬件製造商商,主流的雲計算提供商,網絡設備製造商,都為行業內的頂尖企業。而這次Intel為聯盟成員開放CXL協議鞏固自己在數據中心領域的地位。

來源:超能網

PCIe 5.0規范今年制定:速率再翻倍,128GB/s帶寬

PCIe

4.0規范2017年就已經完成了,不過直到AMD的7nm銳龍3000系列上才有消費級平台支持,此前只有超算、企業級高速存儲、網絡設備等產品才使用了PCIe

4.0技術。雖然PCIe 4.0里普及還早,但是PCI-SIG組織早就開始制定更快的PCIe

5.0了,信號速率相比目前的16GT/s翻倍到了32GT/s,帶寬可達128GB/s,今天公佈了0.9版規范,1.0版規范預計在今年Q1季度完成。

來自TH網站的報導稱,PCIe推進組織PCI-SIG今天批准了PCIe

5.0的0.9版規范,這意味着離正式版規范不遠了,很快就能開始上市終端設備了。通常來說,在0.4版規范時廠商可以開始設計終端產品,0.9版規范時會發佈產品。

與以往的標準規范相比,PCIe 4.0規范來的比較晚,2010年就推出PCIe 3.0規范了,與PCIe 4.0的引入時間間隔了7年,所以PCIe

4.0規范的壽命可能會很短,特別是一些供應商已經開始設計PCIe 5.0 PHY物理層設備了。

PCI-SIG組織希望兩個標準能夠共存一段時間,PCIe 5.0主要用於吞吐量要求更高的高性能設備,比如用於AI的GPU、網絡設備等等,這意味着PCIe

5.0更可能出現在數據中心、網絡及HPC環境中,而台式機等對帶寬需求沒那麼強烈的設備可以使用PCIe 4.0。

對於PCIe 5.0,其信號速率從PCIe

4.0的16GT/s提升到了32GT/s,依然使用128/130編碼方式,x16帶寬從64GB/s提升到了128GB/s。

除了帶寬翻倍之外,PCIe 5.0還帶來了其他變化,改變了電氣設計以改善信號完整性,向後兼容PCIe等等。此外,PCIe

5.0還設計了新標準,減少了延遲,降低了長距離傳輸中的信號衰減。

PCI-SIG組織預計今年Q1季度完成1.0版規范制定,不過他們能制定標準,但無法控制終端設備何時推向市場,預計首批PCIe

5.0設備會在今年亮相,2020年才會有更多產品出現。

來源:超能網

PCIe 4.0/5.0很好很強大,但是成本太貴了

從2011年的HD 7000系列顯卡算起,PCIe 3.0顯卡已經普及7個年頭了,PCIe 4.0的標準也早公布了,下下代的PCIe

5.0都在進行中了,速度可達16GT/s、32GT/s,是現有的兩倍、四倍,很好很強大。不過PCIe

4.0依然離普及很遠,影響它的根本原因就是成本實在太貴,主板PCB升級就要100美元之多,廠商承受不起。

EETimes周末的一篇文章就提到了PCIe 4.0及PCIe 5.0的問題,其中PCIe

5.0標準預計在明年批准,傳輸速度提升到32GT/s,這距離16GT/s速度的PCIe 4.0標準問世不過兩年時間。

對高帶寬PCIe需求最高的是雲計算市場,每隔三四年就需要把數據傳輸率提高一倍,數據中心網絡需要更快的速度才能達到400Gbe,越來越多的深度學習機器也需要高速度。

但是高帶寬PCIe的成本越來越高,因為速度越快,傳輸距離也會縮短,PCIe 1.0在主流FR4主板上有20英寸的信號傳輸距離,PCIe

4.0如果不使用任何連接器,每進一步信號都可能衰減完,這樣就需要廠商使用更好的材料以保證信號。

原文援引專家的分析算了一筆帳——完整的16通道PCIe

4.0重定時器晶片需要15-25美元,適配器從Megtron-2升級到Megtron-4可能會增加1美元成本,但對主板進行類似升級則需要100美元,如果升級到更高質量的Megtron-6,則要花費300美元。

如果是更高級的PCIe 5.0,那麼材料、晶片成本還會水漲船高。

從這里也可以看出,PCIe

4.0問世這兩年來,除了企業級市場之外,消費級市場完全沒有什麼動靜的根源就是成本太高了,而且消費級顯卡、處理器以及網絡對速度翻倍的PCIe

4.0也沒什麼需求,這個問題早在PCIe 3.0問世時就做過測試了,現在的顯卡哪怕是使用PCIe 2.0 x16,性能也不會有明顯損失。 ...