Tag: RISC-V

矽速科技發布高性能模塊化單板電腦,搭載平頭哥RISC-V處理器

援引Liliputing的消息稱,日前矽速科技發布了荔枝派4A單板電腦,據悉它擁有比樹莓派4更高的性能。

這款單板電腦的基於矽速科技早前發布的RISC-V SoM LM4A。這款SoM的核心是平頭哥曳影1520 RISC-V SoC,CPU部分為四核玄鐵C910,頻率為1.8GHz。它還擁有一個玄鐵C906作為DSP協處理器,一個低功耗處理器玄鐵E902。它的GPU算力達到50.7GFLOPS,支持OpenGL、OpenCL和Vulkan等多種API。另外,它甚至還有一塊4TOPS的NPU,可支持TensorFlow等機器學習平台,這是主流的樹莓派4B所不具備的。

(圖片來源:矽速科技)

這塊SoM的記憶體為LPDDR4x-3733,可選容量為4/8/16GB;eMMC作為存儲,可選容量為32/64/128GB。通過260Pin SO-DIMM金手指方式引出引腳與載板連接。載板上則擁有USB 3.0,WLAN和藍牙模塊,3.5mm音頻接口,20pin插針等IO接口。

根據矽速科技的測試數據,荔枝派4A在Dhrystone和CoreMarks性能測試中超越了樹莓派4B。而樹莓派採用的是ARM架構的博通BCM2711,CPU部分為四核Cortex-A72,頻率為1.5GHz。並且在IO,視頻編解碼,還有系統支持上,樹莓派4B都不如荔枝派那麼豐富。

(圖片來源:矽速科技)

另外,矽速科技還計劃推出包括集群、路由器、10.1英寸平板電腦和6英寸手機在內的多種基於荔枝派4A的設備,再結合Debian、Android和OpenWRT等更多系統的支持,這塊單板電腦的可玩性稱得上是十分豐富。至於發售時間這塊,矽速科技表示荔枝派4A將會在2023年第一季度發售,目前可供預定。 ...

正面剛x86 第三大CPU架構RISC-V沖擊高性能:5nm 192核

與ARM、x86分別占據移動、高性能計算市場不同,第三大CPU架構RISC-V目前主要用於各種低功耗平台,HPC高性能計算中甚至不被看好,但還是有人不甘心的,初創企業Ventana Microsystems公司偏要正面剛一把,推出5nm工藝打造的192核RISC-V平台。

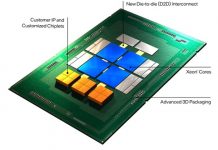

Ventana公司日前發布了第一款產品Veyron V1,該公司研發了一種高性能RISC-V架構,而且使用了AMD的EPYC處理器那樣的小晶片技術,允許客戶從Vnetana那里購買CPU、IO模塊,然後跟自己的加速器IP整合。

就Veyron V1而言,其每個CPU模塊中有16個RISC-V內核,頻率3.6GHz,整合48MB緩存,不僅在RISC-V中算是高頻,在整個CPU行業中也是很高的頻率了,還有大緩存,畢竟是用於高性能計算的。

在Veyron V1,整個處理器可以集成12個CPU模塊,做到192核,台積電5nm工藝生產製造,而IO核心也是自己開發,工藝落後一些,沒有具體提及,猜測也可能是6nm工藝。

這樣做出來的多核處理器在IO延遲要求很高,還好Ventana公司非常自信,他們的IO總線延遲可以低至7ns,比原生核心架構略高,因此性能還是有保證的。

按照計劃,客戶應該在2023年Q2、Q3季度中收到Veyron V1處理器樣品,具體的性能屆時應該會揭曉。

來源:快科技

RISC-V架構 阿里平頭哥發布玄鐵C908 CPU:能效提升超20%

RISC-V架構被認為是繼x86、ARM架構之後,中國晶片產業的第三條路。

在日前舉行的2022雲棲大會上,阿里平頭哥發布全新RISC-V高能效處理器玄鐵C908,官方表示,玄鐵C908計算能效全球領先,較業界同性能處理器能效提升超20%,可用於智能交互、多媒體終端、AR/VR、無線通訊等領域。

據阿里介紹,玄鐵C908支持多核多簇架構,採用高效9級雙發按序流水線,主頻為2 GHz。

玄鐵C908在微架構上得到升級,首次採用RISC-V Vector 1.0標準,並基於標準新增DOT指令,推出INT4數據類型,優化AI算子及算法庫,典型神經網絡計算的性能較前代提升50%以上。

得益於此,玄鐵C908還超越了此前在國際權威AI測試MLPerf Tiny V0.7中奪冠的玄鐵C906,在圖像分類任務中性能再提升3.5倍。

據了解,相比x86、ARM架構,RISC-V擁有開源這項先天優勢,正因如此,除阿里平頭哥外,還吸引了Google、Intel、三星、華為等巨頭參與研發。

雙11紅包活動推薦:

來源:快科技

SiFive推出Performance P670/P470,以滿足可穿戴設備消費類產品需求

基於開源RISC-V架構的晶片設計公司SiFive宣布,推出新的SiFive Performance系列處理器P670和P470。兩款新產品可滿足可穿戴設備、智能家居、工業自動化、AR/VR 和其他消費類設備等大批量應用對小尺寸高性能和高效率的需求。

SiFive表示,Performance P670和P470產品提供的計算密度、能效和強大功能集組合,非常適合各種應用和市場,主要特點包括了:

支持虛擬化,包括用於加速虛擬化設備IO的單獨IOMMU。

完整、無序的RISC-V矢量實現,基於RISC-V Vector v1.0規范。

率先推出RISC-V矢量加密擴展。

SiFive WorldGuard系統安全。

完全符合RISC-V RVA22配置文件。

符合標準的新型高級中斷架構(AIA)中斷控制器,更好地支持消息信號中斷(MSI)和虛擬化。

通過完全一致的多核、多集群增強可擴展性,最多支持16個核心。

Performance P670提供了多項豐富的功能,包括在5nm中實現超過3.4GHz的最大頻率;性能高於12 SpecINT2k6/GHz,在有限面積和功率范圍內提供最優的性能;與傳統解決方案相比,提供更高的單線程性能和兩倍的計算密度;包括一個2x 128位向量 ALU,符合RISC-V Vector v1.0規范。

Performance P470是SiFive首款注重效率的亂序、面積優化矢量處理器,在過往Performance P500系列基礎上進行了擴展,經過優化後,具有一流的性能效率和面積密度,計算密度是領先競爭對手的四倍。同時可以作為Performance P670的配套產品,適用於需要共享計算資源同時優化功耗的苛刻應用。SiFive還將發布Performance P470的面積優化版本P470,不包括矢量單元。

SiFive的Performance P600系列注重的是性能,Performance P670的前身P650在性能上可以與Arm Cortex-A77相媲美。Performance P470被設計為Performance P670的配套晶片,兩者在智慧型手機和平板電腦中可以組成類似Arm的big.LITTLE配置。 ...

英特爾和SiFive展示RISC-V開發平台「Horse Creek」,採用Intel 4工藝製造

去年英特爾確認,會基於SiFive的Performance P550打造自己的RISC-V開發平台「Horse Creek」,而且會採用Intel 4工藝製造,這有可能是英特爾首發的7nm產品。

在英特爾宣布IDM 2.0戰略後,SiFive就已經和英特爾展開合作,SiFive的相關IP可以使用英特爾的代工服務業務(IFS),雙方的關系十分緊密。今年初,英特爾宣布加入RISC-V International,與RISC-V生態系統中的領先合作夥伴聯手,計劃提供一系列經過驗證的RISC-V IP內核,針對不同的細分市場進行了性能優化。

據WikiChip Fuse報導,英特爾在「Intel Innovation」峰會上與SiFive展示了「Horse Creek」開發板,在設計方面受到了樹莓派的啟發,相比於其他RISC-V開發板擁有更多的接口。其採用板載8GB的DDR5記憶體,提供了一個PCIe Gen5插槽,還有各種監控和調試接口。

「Horse Creek」開發板搭載的RISC-V架構處理器擁有四個SiFive Performance P550內核,採用Intel 4工藝製造,尺寸為4 mm x 4 mm,封裝在19 mm x 19 mm的BGA封裝中。SoC還集成了英特爾的PCIe Gen5...

Intel「4nm EUV」工藝再下一城:x86之外也生產了RISC-V處理器

Intel今年的13代酷睿處理器還會繼續使用Intel 7工藝,14代酷睿Meteor Lake則會升級到Intel 4工藝——這是Intel對標友商4nm的工藝,而且首次使用EUV光刻技術,今年下半年已經試產,其電晶體的每瓦性能將提高約20%。

Intel的4nm EUV工藝不僅會用於生產自家的x86處理器,同時還會用於旗下的IFS晶圓代工部門,也就是開放給其他廠商,最新消息稱4nm EUV工藝已經為SiFive公司生產了代號Horse Creek處理器。

現在這款處理器已經從工廠回到了實驗室,據說表現非常好,進展很順利。

Horse Creek是SiFive公司研發的高性能處理器,基於高性能P550內核,該公司是全球開源處理器RISC-V的IP授權龍頭公司,地位相當於移動晶片中的ARM公司。

今年2月份,SiFive公司宣布與Intel達成合作協議,將會基於Intel 4工藝開發Horse Creek平台處理器,產品預計在2022年上市。

來源:快科技

蘋果嵌入式內核將全面轉移到RISC-V架構,或節省授權費用

去年有報導稱,蘋果正在招募RISC-V架構的程式設計師,主要負責iOS、macOS、watchOS、tvOS上運行各種嵌入式子系統的設計和相關改進。根據招聘的描述,應聘者還需要懂得機器學習、計算視覺和自然語言處理技術,同時要對Arm的擴展架構Neon有深入了解。當時就有人從職位的描述中看出,蘋果已經有RISC-V架構的設備在運轉了。

據SemiAnalysis報導,蘋果正在將其嵌入式內核將全面轉移到RISC-V架構。目前蘋果M系列處理器中,除了主核心外,還有大量的嵌入式輔助核心,像M1里就有30多個,負責與作業系統無關的各種工作負載,包括Wi-Fi/藍牙、觸摸板控制、雷電接口等。這些嵌入式輔助核心運行著自己的固件,圍繞運行作業系統的主核心為周邊提供動力。

這類型嵌入式輔助核心很多時候都基於Arm的Cortex-M系列或低端的Cortex-A系列內核,而蘋果正在使用RISC-V架構內核取代。由於這些功能模塊的嵌入式輔助核心大多功能單一,蘋果在固件上稍作調整即可重新適配,以蘋果工程團隊的規模和能力,這麼做的難度並不大。

如今蘋果使用眾多的Arm架構處理器,需要支付一大筆授權費用,隨著蘋果自研晶片的進一步發展,以後數量會繼續增加,費用也會水漲船高。如果將嵌入式輔助核心更換成RISC-V架構內核,由於其免授權費用及開源的特性,蘋果可以省下一大筆錢。

不清楚蘋果什麼時候會將嵌入式內核全面轉移到RISC-V架構,畢竟蘋果不會為此發布正式公告,一方面其自研的M系列處理器在主核心上仍基於Arm架構,另一方面這些嵌入式輔助核心的所有內容對用戶來說都是不可見的。 ...

打破x86、ARM壟斷 CPU技術大牛Jim Keller放言:RISC-V必勝

在全球市場上,x86架構在高性能CPU市場掌握絕對份額,ARM架構在低功耗市場無人能敵,這兩家壟斷了大部分CPU市場,未來能三分天下的可能就是RISC-V了,此前在AMD及Intel都工作多年的大牛Jim Keller也RISC-V必勝。

Jim Keller是何許人也?很多人聽過他,也有很多人不知道,他在半導體行業有20多年經驗,1998年之前在DEC參與了Alpha處理器研發,1998年後進入AMD公司,參與了K7、J8架構CPU研發,離職後又參與了博通、PA Semi及蘋果的CPU研發,2012年重回AMD公司,參與了Zen處理器研發。

2016年在Zen處理器上市前半年離開AMD,去了特斯拉開發自動駕駛晶片,2018年去了Intel公司,不過2020年離職了,現在在一家名為Tenstorrent的初創公司擔任高管,主要設計RISC-V架構的AI晶片,號稱要超越AMD/NVIDIA。

他在晶片行業先後參與了Alpha、x86、ARM等架構開發,現在主要是RISC-V架構了,了解這些背景之後才可以理解他對RISC-V的表態,他認為RISC-V未來必勝。

原因也很簡單,RISC-V晶片現在已經可行了,而且是開放標準的,這個領域的創新正在發生,相比其他架構崛起得更快。

即便考慮到他自己正在從事RSIC-V研發的問題,Jim Keller對RISC-V的四大優勢總結的也是很客觀的,這也是當前的現實,相比x86及ARM架構,RISC-V在性能、生態等問題上顯然有不足,但它的開放及發展速度也是遠超其他兩種架構的。

今年7月份,RISC-V國際基金會CEOCalista Redmond表示,開放標準是關鍵。

她說:“Linux在軟體領域做到了這一點,我們正在硬體領域做到這一點。”她表示:“我們估計市場上已經有100億個核。”

這是什麼概念?哪怕是ARM架構做到100億核心出貨也用了17年時間,直到2008年才實現。

她認為RISC-V可以在未來五年內達到ARM 20年的成就。

來源:快科技

x86/ARM有對手了 Intel力挺第三大CPU架構RISC-V

MIPS倒下後,RISC-V正成為繼x86、ARM之後,冉冉升起的第三大CPU架構。

在RISC-V背後的支持者中,有一個特別的身影,即“x86之王”Intel。

實際上,Intel通過與RISC-V CPU內核開發公司SiFive合作,已經實現了FPGA平台對RISC-V的支持,現在Intel有宣布為普通愛好者和商業晶片製造商提供完整的RISC-V開發套件。

Intel此次的Pathfinder開發工具可讓各種RISC-V內核/IP等在FPGA、模擬器上可操作化,還能在統一的IDE(集成開發環境)中運行最新作業系統和工具鏈,甚至還能承接Intel的代工服務。

據了解,目前SiFive研製的最高端RISC-V內核為P650,對標的是ARM Cortex-A77。

歷史上,Intel在非x86架構上花了不少錢,比如上世紀80年代基於RISC的i960/i860、本世紀初的ARM以及基於VLIW的IA64/安騰(Itanium)等。

來源:快科技

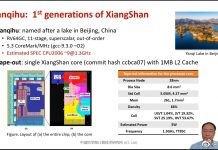

打破x86/ARM壟斷 第三代香山RISC-V開源處理器核研發啟動

8月26日消息,日前,第二屆RISC-V中國峰會北京會場系列活動“首屆北京開源晶片生態產業論壇”正式舉行。

據中科院計算所副所長包雲崗介紹,香山開源高性能RISC-V處理器核發展歷程迎來又一里程碑。

論壇上,中科院計算所、北京開源晶片研究院、騰訊、阿里、中興通訊、中科創達、奕斯偉、算能等形成了聯合研發團隊,開展第三代香山(昆明湖架構)的聯合開發。

包雲崗指出,香山聯合團隊的形成,標志著得到了香山及其開源模式得到了產業界的初步認可,為跨越“從原型到產品”這個死亡之谷邁出了關鍵一步。這還只是第一步,後續一定還會遇到很多挑戰和困難,但我們也做好了迎接各種挑戰的准備。

據悉,“香山”第一代內核“雁棲湖”已在去年7月15日流片,基於28nm工藝,裸片面積6.6平方毫米,單核二級緩存1MB,預計功耗5W。第二代核心“南湖”目標是14nm 2GHz。

值得一提的是,中國工程院院士倪光南指出,目前CPU市場主要被x86和Arm架構所壟斷,而中國想要打破這個局面,實現自主可控,開源的RISC-V架構將是一大機遇和發展方向。

在未來世界主流CPU架構格局中,RISC-V架構將有望達到三分天下有其一。

來源:快科技

x86/ARM勁敵 第三大CPU架構RISC-V性能崛起了

幾乎所有晶片創業公司的CEO都會說,“我們最核心的價值是用更好的晶片解決客戶的實際問題。”

然而,擺在眾多晶片初創公司面前的問題是,晶片設計和生產出來後,落地遲遲難以突破,此時,產品能夠順利落地的公司成為了這個賽場里值得關注的焦點。

由前GoogleCTO江朝暉於2020年創立的躍昉科技(LeapFive)是晶片創業熱潮中值得關注的RISC-V晶片公司。

原因很簡單,站在創業公司比拼落地的2022年,躍昉科技高性能產品的發布會上,就已經有來自電力、智慧物流、機密計算等領域客戶的案例分享。雷峰網(公眾號:雷峰網)了解到,躍昉科技的晶片已經在國家電網的多個單位進行部署,是可規模化復制的落地。

預計在今年底量產的躍昉科技高性能RISC-V處理器NB2實測性能在Arm CortexA55和A72之間,直戳Arm小核,指向Arm大核性能。

晶片創業實際比拼對應用場景的理解

對於九死一生的創業來說,特別是一次晶片流片費用就以千萬甚至億元計的晶片創業公司,創業之初更需要想清楚產品的定位和應用市場。

躍昉科技研發VP袁博滸在“躍昉智慧物聯芯,助力雙碳新基建”的新品發布會上就說,“對一個晶片產品最終的評價應該是以應用的規模和成熟度作為參考,所以核心就是應用為王。

轉換為底層的邏輯有三點:為客戶帶來供應鏈安全、具備差異化特性、具備成本優勢。”

應用為王的道理容易理解,但在創業之初,真正有明確目標應用場景的晶片創業公司實際不多。

“2020年創業時,公司只有我和袁博滸,如今公司的團隊規模已經有一百七八十人。”躍昉科技創始人,CEO兼CTO江朝暉說,“我們圍繞三個核心,聚焦工業和物聯網領域。

首先是利用RISC-V開源的CPU架構設計高中低端性能的邊緣晶片;其次是包含區塊鏈技術,保證數據不可篡改、可追源;第三注重安全性能。”

之所以圍繞工業和物聯網應用創業,其實有多方面的原因,一方面是創始人江朝暉對於用科技去解決能源問題的情懷,更實際的原因是工業市場對於SoC晶片的需求,以及使用RISC-V在工業市場落地的難度更小。

“消費類晶片由於市場競爭激烈,所以首先會關注成本,其次才會考慮功能的差異化以及供應鏈安全。工業類的晶片恰好相反,客戶會首先考慮供應鏈安全,然後考慮差異化,最後才是成本優勢。”袁博滸表示。

“在軟體生態方面,工業領域的軟體生態又比消費生態稍小,非常符合RISC-V的發展現狀。”

除了有明確的產品規劃、市場應用之外,更能體現躍昉科技對應用為王的是早期就有深度的合作夥伴。

從應用出發定義晶片,性能超越Arm A55

雷峰網了解到,躍昉科技在早期設計晶片之初就充分了解了工業物聯網領域對晶片的需求,並與中國電力科學院深度合作,設計出了高性能的NB2處理器。

中國電力科學研究院有限公司人工智慧應用研究所所長蒲天驕在發布會的分享中指出,電力物聯網目前面臨幾個共性問題:數據傳輸處理壓力大、雲端主站計算負荷重、海量數據價值無法挖掘、晶片供貨難度大。所以針對電力邊緣智能高算力、低功耗、自主可控等方面提出了全新的要求。

“鑒於NB2晶片的技術優勢,我們中國電科院與躍昉公司簽訂了戰略合作協議,並入駐國網公司雙創示範中心,雙方一起承擔了國家重點研發計劃以及國網公司技術項目,共推動電力物聯網邊緣智能晶片規格制訂、協同研發和成果落地等。”蒲天驕進一步表示。

正是因為有明確的需求,躍昉科技的NB2晶片敢於用12nm工藝,自主設計出主頻超過1.5GHz的RISC-V CPU,同時集成NPU,DSP、VPU等的工業級SoC。

NB2的自研CPU主頻最高達1.8GHz,GPU主頻達850MHz,NPU在INT8數據格式下性能達到4TOPS,並集成VPU和用於增強輔助NPU視覺處理的視覺DSP,還有音頻DSP。

從CPU的性能看,NB2 的CPU性能在Arm Cortex A55和Cortex A72之間,這在RISC-V陣營大都對比Arm Cortex M系列的當下,NB2率先向高端邁出一步。

相比硬體性能,軟體是限制RISC-V處理器向更高端應用突破的關鍵。

RISC-V作為新興的指令集,軟體生態不夠成熟讓眾多RISC-V晶片公司選擇從對生態依賴不高的MCU市場切入,所以可以看到在CPU主頻低於200MHz的MCU市場有大量RISC-V產品,到了CPU主頻在200MHz-1.5GHz的MPU產品就數量不足10種,在CPU主頻性能超過1.5GHz的高端應用處理器(AP)幾乎空白。

“以目前RISC-V的發展現狀,我們選擇了工業網際網路,工業應用穩定性優先,給我們從RISC-V出發,為工業賽道設計一個相對滿足應用的軟體生態提供了一些便利。”袁博滸表示。

但即便如此,躍昉科技在成立早期就投入了60多人的軟體團隊。

整體而言,袁博滸強調,NB2是第一款可量產的基於RISC-V的高端12nm工業級SoC。

“我們嚴格遵循工業級晶片的測試標準,在零下55攝氏度到125攝氏度的環境下測試了1000小時以上,擁有工業級的品質,在高溫實測中的表現,也非常符合電網整機系統熱設計的需求。”

NB2還支持異構OS運行環境,這個功能也能很好滿足工業場景中部分程序運行在裸機,部分程序運行在Linux上的特殊需求。

晶片創業落地為王

晶片公司最終的商業化成功,實際上是軟體和生態的成功。

因此,晶片初創公司產品落地挑戰巨大也容易理解,畢竟初創公司大都採用新技術,比如比較火熱的AI晶片創業和RISC-V創業,這兩類晶片都比較新,沒有成熟的軟體生態,客戶想要發揮這些硬體優勢的挑戰巨大。

“我們希望靠豐富的SDK性能,使所有的硬體性能得以發揮,客戶的應用能正常、快速、穩定地遷移到我們的系統上。”袁博滸表示。

但對於RISC-V晶片而言,客戶的接受度非常關鍵,畢竟RISC-V是一個比較新興類別的產品,無論在可靠性和性能客戶都會有比較大的擔憂。但也正因為如此,在工業領域SoC選擇不多的背景下,軟體生態相對簡單一些,更是RISC-V高性能晶片的突破點。

躍昉科技的做法是,給客戶提供完整的系統,除了晶片和軟體,還有對應參考設計硬體,以及完整的開發平台。

目前,躍昉科技與中國電科院的合作包括基於NB2的邊緣網關、無人機巡檢系統。已經面向光伏功率預測、電纜廊道感知、輸電線路在線監測、變電站監測等應用場景,分別在中國電科院、重慶公司、天津公司、遼寧公司等單位部署NB2,目前運行正常。接下來雙方還將在更多領域中共同深度探索。

躍昉科技還與鏈昇科技深度合作,將NB2應用在智能物流倉儲場景中。

與摩聯科技合作,基於NB2實現基於RISC-V的機密計算,貫通可信物聯網數據價值鏈。

袁博滸也表示,“和客戶共同開發全棧軟硬體方案只是在剛開始客戶信心不足的情況下,需要與客戶進行的工作,這並非趨勢。”

這也就意味著,未來RISC-V的軟體生態逐步成熟之後,高性能RISC-V晶片的易用性會逐步提高,RISC-V高性能晶片的應用將會進一步拓展。

來源:快科技

RISC-V架構已出貨100億個內核,今年將推出四項新的規范和擴展

RISC-V作為一種開放標準指令集架構,根據開源協議可以免費試用,基本指令集具有32位固定長度自然對齊指令,並且支持可變長度擴展,如今已應用在各種小型嵌入式系統到大規模的機架式並行計算機上。

近日,RISC-V International的執行長Calista Redmond在Embedded World上宣布,RISC-V架構內核的出貨數量已達到100億個。

Linux正在為軟體這麼做,而我們正在為硬體這麼做。我們估計市場上有100億個RISC-V內核。

達到100億個內核並不是容易的事情,要知道如今大紅大紫的Arm架構經過了17年反復更迭,到了2008年才走到這個里程碑,而RISC-V架構僅用了12年就實現了。Calista Redmond預計到2025年,RISC-V架構內核的出貨數量將達到800億個。

近期RISC-V International還宣布2022年將推出四項新的規范和擴展,包括了:

RISC-V通過E-Trace定義了一種使用分支跟蹤的高效處理器跟蹤方法,非常適合調試從微型嵌入式設計到超強大計算機的任何類型的應用程式。

RISC-V的SBI規范,在管理模式(S模式或VS模式)下使用應用程式二進位接口在硬體平台和作業系統內核之間構建了一個固件層,支持跨所有RISC-V作業系統實現的通用平台服務。不少RISC-V成員已經在他們的RISC-V解決方案中實施了RISC-V SBI規范,因此批准該規范將確保整個RISC-V 生態系統的標準方法,並確保兼容性。

RISC-V UEFI協議將現有的UEFI標準引入到RISC-V平台。

RISC-V Zmmul純乘法擴展,支持需要乘法運算但不需要除法的低成本實現,並且是RISC-V非特權規范的一部分。

...

ARM、x86勁敵 第三大CPU架構RISC-V出貨100億核心

目前的CPU市場上,高性能領域被x86架構占領,低功耗領域被ARM占領,就在它們互相搶市場的時候,開源的RISC-V架構崛起了,已經成為第三大CPU架構,而且這幾年中就出貨了100億核心。

在最近的嵌入式世界展覽會上,RISC-V International的執行長Calista Redmond表示,開放標準是關鍵。

她說:「Linux在軟體領域做到了這一點,我們正在硬體領域做到這一點。」她表示:「我們估計市場上已經有100億個核。」

這是什麼概念?哪怕是ARM架構做到100億核心出貨也用了17年時間,直到2008年才實現,不過這幾年出貨量也在加快,16到21年的5年中出貨量超過1000億。

RISC-V未來的發展速度可能更快,Redmond今年5月份表態稱,她認為RISC-V可以在未來五年內達到ARM 20年的成就。

來源:快科技

20年老牌CPU廠商轉型 RISC-V架構新U瓜熟蒂落

去年12月份,作為擁有20多年歷史的老牌晶片設計公司,,推出全新的Catapult系列處理器產品,涵蓋動態微控制器、實時嵌入式CPU、高性能應用處理器CPU、支持汽車功能安全的CPU四大品類。

今天,Imagination宣布推出其首款實時嵌入式IMG RISC-V CPU,型號為「RTXM-2200」,也是此前Catapult系列首批商用核之一。

RTXM-2200是一款具備高度可擴展、功能豐富、設計靈活的32位嵌入式解決方案,可以集成到復雜的SoC系統晶片中,可用於網絡解決方案、數據包管理、存儲控制器、AI攝像頭和智能計量傳感器管理等。

據介紹,這款實時嵌入式內核的I-TCM、D-TCM均可高達128KB,同時一級指令緩存、一級數據緩存都能達到128KB,還支持多種浮點格式,包括單精度、bfloat16,尤其是支持bfloat16,可以不依賴其他晶片而直接支持AI應用,減少成本。

IMG RTXM-2200 CPU是Imagination異構計算解決方案的一部分,不但為Imagination IP提供完整的硬體、軟體和調試支持,還與Imagination領先的GPU、AI加速器和乙太網分組處理器(EPP)核形成互補。

軟體方面,同時擁有功能齊全的SDK和工具包,可直接用於多個平台,幫助開發和支持RISC-V生態系統。

還有Catapult Studio IDE集成開發環境,基於Visual Studio,提供更適合現代開發者和設計者的熟悉環境,作業系統支持Windows、Ubuntu、CentOS、macOS,並提供完整的Linux支持,包括參考引導加載程序、內核和文件系統,還兼容gem5軟體。

來源:快科技

MIPS倒塌 對抗x86/ARM的全新第三大CPU架構RISC-V崛起了

近日,Imagination Technologies宣布推出IMG RTXM-2200,這是其首款實時嵌入式 RISC-V CPU,這是一款高度可擴展、功能豐富的 32 位嵌入式解決方案,具有靈活的設計,適用於各種大容量設備。

IMG RTXM-2200 是 Imagination 的Catapult CPU 系列中首批商用內核之一,此前於 2021 年 12 月發布。

Imagination 的 IMG RTXM-2200 可加速其 RISC-V 產品的擴展,可集成到復雜的 SoC...

x86/ARM怕嗎?第三大CPU架構RISC-V加新規范:效率更高了

作為沖擊x86/ARM的第三大CPU架構RISC-V,其正在得到更多廠商的追捧,所以更好的去完善它是非常有必要的。

RISC-V國際組織宣布了2022年的首批四項規格和擴展的批准--RISC-V高效跟蹤(E-Trace)、RISC-V主管二進位接口(SBI)、RISC-V統一可擴展固件接口(UEFI)規格,以及RISC-V Zmmul純乘法擴展。

"這些新規范加速了嵌入式和大型系統的設計,"RISC-V的首席技術官Mark Himelstein說。"調試是晶片上最難做的事情之一,RISC-V的E-Trace創造了一種標準的處理器跟蹤方式,效率極高,在嵌入式系統設計中特別有用。"

RISC-V UEFI協議將現有的UEFI標準引入RISC-V平台。該規范的開發和批准由Ventana Micro的Sunil V L和VRULL GmbH的Philipp ToMSIch領導,工作在特權軟體技術工作組進行。

對此,專家表示,對於許多微控制器應用來說,除法操作的頻率太低,不足以證明除法器硬體的成本,RISC-V Zmmul擴展將特別有利於簡單的FPGA軟核。

來源:快科技

x86/ARM勁敵 第三大CPU架構RISC-V進入超算:表現驚人

一個歐洲大學生團隊組裝出第一台能夠平衡功耗和性能的 RISC-V 超級計算機。

更重要的是,它展示了 RISC-V 在高性能計算方面的巨大潛力,為歐洲擺脫對美國晶片技術的依賴提供了機會。

「Monte Cimone」集群不會很快用於處理大規模的天氣模擬等,因為它只是一台實驗機器。

這台設備由博洛尼亞大學和義大利最大的超級計算中心 CINECA 的人員構建,六節點集群設計,旨在展示除浮點能力之外的各種 HPC 性能元素。

它使用 SiFive 的 Freedom U740 片上系統RISC-V 的電源模塊,這個2020 年推出的 SoC 有五個 64 位 RISC-V CPU 內核——四個...

Intel宣布發力第三大CPU架構RISC-V:性能將比x86高出1000倍

當前,x86和ARM是世界前兩大CPU架構,Intel作為x86霸主,這麼多年來對ARM一直不感冒,除了當年收購StrongARM後嘗試做過幾款,但最終無疾而終。

雖然x86依然在通用和高性能計算領域有著無可撼動的地位,可Intel的觸角也開始伸向精簡指令集架構,可這次不是ARM,而是更加開放的RISC-V。

隨著MIPS的倒下,RISC-V已經成為世界第三大CPU架構。Intel、阿里、華為、Google、中興等也都是每年繳納25萬美元會費的RISC-V國際組織高級會員。

本周,Intel和西班牙超算中心聯合宣布,將投資4億歐元(約合28.5億元)建立聯合實驗室,10年內開發出基於RISC-V的處理器,目標是用於zettascale規模的超算,也就是十萬億億次,比現在提升1000倍。

要知道,超算算力本周剛剛在美國被刷新,AMD EPYC霄龍處理器、Instinct加速卡打造出全球第一台百億億(exascale)次超算「Frontier」。

實際上,Intel對RISC-V的覬覦不是第一次了,去年還曾試圖收購RISC-V IP研製公司SiFive。

歷史上,Intel也在非x86架構上花了不少錢,比如上世紀80年代基於RISC的i960/i860、本世紀初的ARM以及基於VLIW的IA64/安騰(Itanium)等。

來源:快科技

x86/ARM勁敵 第一款RISC-V架構處理器筆記本來了:運行Windows

隨著MIPS的倒下,RISC-V已悄然成為世界第三大處理器架構,並對x86和ARM虎視眈眈。

在本月初於法國巴黎舉行的RISC-V Week活動上,RISC-V管理組織RISC-V International軟體開發主席Philipp Tomsich曝光了一款黑色的白牌筆記本。

他還透露,多核設計、頻率2GHz以上……

從圖片來看,筆記本並沒有什麼特別之處,從左下角的Windows徽標鍵判斷,它應該支持運行Windows作業系統。

另外,有英國網友注意到左上角出現的「景田」純淨水,猜測這款筆記本是不是中國廠商率先打造。在交流中,Philipp Tomsich的確稱贊了中國公司阿里雲,他們率先實現RISC-V對Android 12的支持。

當然我們也應該謹慎樂觀,因為最大的RISC-V晶片設計公司SiFive曾表示,旗下CPU進入個人電腦最快要到2025年。

來源:快科技

第三大CPU架構RISC-V要靠性價比攪局:ARM小心了

RISC-V的存在值得Arm警惕

晶片公司CEO們的訪談總是能夠引人深思,除了通常我們談論的市場上的成功與失敗、收入與競爭、計劃和陷阱等主題之外,還有一部分是技術宅渴望的技術細節。

近期,國外雜誌The Register對RISC-V International 執行長Calista Redmond進行了一次采訪。

在訪談中,Calista Redmond談及英特爾不太擔心自己的x86業務,因此成為ISA聯盟的白金會員,以及2022年的RISC-V會是什麼樣子——開始進入筆記本電腦領域、AI領域、Google超大規模晶片以及邊緣領域,並計劃在5年內完成Arm花了20年才取得的進展。

Redmond給出了一個大膽的觀點:「RISC-V可能不會對英特爾構成威脅,但Arm需要警惕RISC-V的存在。」

Redmond所指出的RISC-V取得了重大進展確實有據可依,畢竟獲得業界的支持就是一項了不起的成就,RISC-V已經在CPU行業成為一個強有力的競爭者並備受行業關注,目前正在一步步建立自己的生態系統。

這些都是RISC-V的必經之路,但距離真正的生態繁榮還有一段路要走。

處理器市場是一個非常奇怪的市場,沒有真正的跡象表明RISC-V將成為殺手級處理器。

真正的挑戰不是技術能力,也不是能夠做到競爭對手沒辦法做到的事情,例如RISC-V 以嵌入式和 SoC 晶片的形式大量出貨,並且是唯一一個設計人員可以在 ISA 級別自由添加或修改架構特性的 ISA。與其兩個競爭對手的市場優勢相比,這些依然有一些微不足道。

強如Arm,也賺不了「大錢」

再看看Arm。2021年,Arm賣出了300億個核,即平均全球一個人擁有四個內核,賺得27億美元。

Arm的成績證明了三點,第一,全球對先進的移動和嵌入式內核的需求巨大;第二,Arm在移動市場占據絕對的領導地位;第三,即便是這樣,Arm也沒有賺到多少錢。

可能27億美元會被認為是一大筆錢,利潤率也不容小覷,但它僅占全球手機收入4500億美元的0.6%,Arm處理器作為手機核心器件,所賺取的利潤並不能算多,如果Arm的主導地位發生巨變,絕對不是因為市場上有足夠的利潤可以賺取。

英特爾每年有800億美元收入,這是因為英特爾擁有龐大的晶片工廠,對於RISC-V來說,英特爾ISA IP與Arm非常相似,IAS IP的部門化非常獨特。

英特爾和Arm都是各自領域的統治者,盡管幾十年來都試圖在對方主導的市場上攻城略地,但所統治的領域幾乎沒有重合過。去年蘋果公司推出的Mac Mini M1,是自1990年代初,Acorn電腦之後第一款基於Arm處理器的主流桌上型電腦(Raspberry Pi不是主流桌上型電腦)。

至於基於英特爾x86的智慧型手機,歷史上更是沒有記載,PC領域和移動領域都沒有第二名,就連對方的ISA也沒有,數十年來無論是行業工具還是理論知識的發展勢頭,加上雙方在創新上的大量投資,主流CPU市場被兩家互相競爭卻又充滿活力的壟斷企業做瓜分,想與其中任何一家競爭,都只能望其項背。

性價比應該成為RISC-V的競爭優勢

要使RISC-V真正繁榮起來,RISC-V也需要有自己的領地。

AI/ML可以是其中之一,這一領域有很多加速器設計非常多樣化,業界暫無贏家。

物聯網也是一大機會,但這不是新機會,物聯網的發展已經經歷了早期的實驗階段,並被鎖定在高性能標準架構中,事實上,大公司已經做好了劃分新行業的准備。

即便確實出現了一個新領域,RISC-V也必須有一個核心競爭力,開源並不能提供足夠的資金和技術優勢,因為大多數原始設備製造商還是會像Arm一樣授權核心,而不是設計自己的核心,現在的SoC可以在不更改ISA的情況下添加大量架構創新。

坦白來說,RISC-V需要極高的性價比。一個月前,第一台RISC-V SBC VisisonFive出現了,它就像Raspberry Pi一樣,只是更大、更慢、更貴。Pi開創了自己的行業,因為它基於博通SoC多年的行動電話技術,擁有比競爭對手更小、更快、更便宜的優勢,但RISC-V卻不能帶來什麼。

RISC-V不可能通過超越Pi而獲得巨大成功,它需要以一種非常吸引人的方式找到一些應用領域,具體是什麼不重要,但是必須保證一點,在這個領域RISC-V必須保證第一的地位,不給第二位留有空間。

來源:快科技

取代x86/ARM 第三大CPU架構RISC-V有了小目標:要統治世界

隨著MIPS的倒下,RISC-V已悄然成為世界第三大處理器架構,並對x86和ARM虎視眈眈。

日前與TheReg交流時,RISC-V管理組織CEO Calista Redmond女士並沒有掩蓋自己的雄心,她表示希望這個新興的開源架構技術能統治世界。

對於如何做到這一點,Redmond提出要爭取到協會付費成員的支持,從而有足夠的資金支持這一免費、開源架構的持續演進,從而和ARM、x86更好的競爭。

RISC-V International已經有20多名高級會員,會費是25萬美元。這其中有個有趣的名字那就是Intel,現今的x86處理器之王。此外,還有阿里雲、Google、華為、紫光展銳、中興等我們耳熟能詳的名字。

不過,參會並不意味著Intel也有想法以RISC-V來端掉自己的x86「飯碗」,Redmond的看法是,Intel正在大力發展自己的晶圓業務,明確表態可以為其它公司代工x86、ARM、RISC-V等晶片。顯然,從這個角度出發,Intel多一些對RISC-V的滲透,一點壞處都沒有。

按照Redmond的預期,她認為RISC-V可以在未來五年內達到ARM 20年的成就。雖然看起來是一番要取代競品的口吻,可Redmond女士強調,x86/ARM不會過時,未來的IT從業者們會綜合使用三套架構,讓它們在不同場景中找到最佳位置。

另外,Redmond女士還透露,年底前會有基於RISC-V的伺服器和PC產品公布。

來源:快科技

曾經的第三大CPU架構:徹底終結了

來自矽谷的 Wave Computing 周二表示,由於其一度流行的 MIPS 架構即將落伍,它今年將推出兩款採用 RISC-V 架構的新型微處理器設計。

此舉增加了 RISC-V 的增長勢頭,RISC-V 是一種開放標準指令集架構 (ISA),是軟銀集團旗下半導體技術公司英國 Arm 專有架構的新興競爭對手。

新生的RISC-V日益流行很大程度上歸功於其自由和開放標準。由於中國公司開發基於該架構的技術可能不受美國出口管制的影響,它也有可能幫助中國建立自己的半導體產業,因此也受到關注。

Wave 的 MIPS 架構是在史丹福大學教授 John Hennessy 的實驗室開發的,迄今已過去35年。

不過,它已經落後於統治移動晶片領域的 Arm 架構,以及最初由英特爾公司開發的 x86 ,後者主導了筆記本電腦和數據中心晶片。在被一系列公司擁有後,MIPS...

阿里平頭哥玄鐵CPU重要突破:首次實現RISC-V+安卓12的AI支持

,現在開源的RISC-V處理器上也取得了重要突破,研發的玄鐵C910處理器玄鐵C910上成功運行TensorFlow Lite,首次實現RISC-V在安卓新系統上的AI支持;同時,平頭哥集成多項第三方關鍵組件,為廣大RISC-V集成商和開發者成功打樣。

平頭哥公布RISC-V兼容安卓12.0最新進展

RISC-V是新興的CPU指令集架構,安卓(Android)是全球使用最廣泛的作業系統之一,兩者的深度融合被業界寄予厚望,是極具前瞻性的研究方向,技術挑戰很大。

此前,平頭哥通過10萬余行的代碼修改,率先實現了安卓10.0關鍵組件在RISC-V上的移植,成功運行Chrome瀏覽器,初步證明了RISC-V架構具備的高性能潛力。平頭哥的這一工作也已開源。

隨著安卓系統的疊代更新,安卓12.0版本引入了Bazel新架構、Rust新語言和Studio新功能,其Art和Bionic模塊也實現了架構層面的進化。這給RISC-V兼容安卓系統提出了全新挑戰。

基於此,平頭哥對安卓12.0進行了系統性的RISC-V優化支持,並通過Android Studio在 RISC-V 架構上成功運行Tensor Flow Lite模型,開啟了RISC-V在安卓平台上對人工智慧的支持。

安卓12.0,玄鐵C910上成功運行TensorFlow Lite

而針對RISC-V第三方組件開發面臨的支持缺乏、系統不兼容及認證水平低等問題,平頭哥首次在安卓12.0版本上集成並驗證了RISC-V架構的音頻播放、視頻播放、WiFi和相機等關鍵功能:這證明了RISC-V兼容最新版本安卓12.0的可行性,也將極大降低RISC-V廠商開發和集成相關組件的門檻。

「此次我們將RISC-V對安卓的支持擴展到核心工具集、第三方庫和 SoC 板級支持包(BSP)上,首次將它們都集成到系統中來實現,將RISC-V與安卓的融合再往前推進一步。這些架構支持若被接收為安卓官方的ABI接口,將是下一個里程碑。」平頭哥技術專家毛晗介紹說。

據了解,毛晗是RISC-V國際基金會安卓技術工作組(Android SIG)的主席。

RISC-V國際基金會致力於推動技術、標準和生態的發展成熟,下設9個委員會和60多個技術工作組,其中共有8個技術領導崗位來自阿里平頭哥,數量是中國企業中最多的。

平頭哥資深技術專家李春強告訴記者:「我們也將繼續開源RISC-V在安卓系統上的新進展,希望此舉吸引更多生態夥伴加碼新架構。

RISC-V是面向未來的架構,平頭哥將持續推動開放、普惠的RISC-V生態建設,讓更多開發者和廠商共享RISC-V的技術紅利。」

來源:快科技

首款量產RISC-V處理器玄鐵C906雲上免費開放 開發者可體驗「算力自由」

4月18日,。本屆大賽採用首款量產RISC-V處理器玄鐵C906,參賽者可通過平頭哥免費開放的「雲上實驗室」一鍵開發,在不受軟硬體限制的RISC-V「算力自由」開發環境中,探索「碳中和」及工業控制等領域的創新應用。

2022「玄鐵杯」RISC-V應用創新大賽開賽

RISC-V是近年興起的一種CPU新架構,因其開放、靈活的特性而逐漸成為半導體行業的熱門選擇。

當前,已有近2500家機構加入RISC-V基金會,包括阿里、華為、Google、英特爾、IBM等公司。據調研機構Semico Research預測,到2025年,全球RISC-V處理器出貨量將增至624億顆,廣泛應用於工業、PC、消費電子、物聯網等領域。

目前,RISC-V已發展出高能效、低功耗的性能優勢,但上層應用不夠豐富,底層晶片與系統軟體優化程度不高,產業鏈上下游未形成合力,成為RISC-V生態發展面臨的主要壁壘。

「舉辦RISC-V應用創新大賽,是推進生態發展的一次新嘗試。」大賽負責人、平頭哥RISC-V生態副總裁楊靜表示,「我們聚焦具體行業領域,邀請全球開發者參與體驗,共同推動RISC-V技術的成熟及應用落地。」

據了解,2022「玄鐵杯」RISC-V應用創新大賽由晶片開放社區(OCC)主辦,分設「碳中和」、工業控制及機器人、視覺及可穿戴設備、智慧家居等4條賽道。

為讓更多開發者體驗玄鐵RISC-V,激發天馬行空的創意,本次大賽特設兼容多種系統及環境的「雲上實驗室」,參賽者可不受限地測試及開發項目,感受RISC-V「算力自由」。

大賽免費開放雲上實驗室,開發者可體驗玄鐵RISC-V「算力自由」

大賽分為創意提交、項目開發、終審等三大階段,邀請來自學術界、產業界的多位頂級專家,從技術可行性、方案完整性、項目創新性、生態貢獻及原創性等方面進行全面評審,將評選出一、二、三等獎及創意獎等18個優秀項目,最終名單預計於9月公布。

據悉,2021年RISC-V應用創新大賽共吸引了全球1054支隊伍參賽,其中,智慧停車、三軸機器臂等創意項目獲獎,實現了應用落地。

此前,包括C906在內的4款玄鐵RISC-V量產處理器及全棧軟體均已開源,玄鐵系列處理器也已出貨超25億顆。「平頭哥致力於建設開放、透明和普惠的RISC-V生態,未來也將加大投入,與各界持續推動RISC-V軟硬體協同及應用的創新。」楊靜說。

來源:快科技

打破x86/ARM壟斷 中科院RISC-V開源處理器「香山」新歸屬敲定

4月10日消息,日前,中科院計算技術研究所副所長、RISC-V國際基金會理事會成員包雲崗透露,中科院RISC-V開源處理器「香山」有了新的歸屬——北京開源晶片研究院(開芯院)。

包雲崗表示,經過四個月的籌建,現已正式啟動第一批圍繞「香山」的新項目,後續也將陸續啟動其他開源晶片項目。

據悉,「香山」第一代內核「雁棲湖」已經在去年7月15日流片,基於28nm工藝,裸片面積6.6平方毫米,單核二級緩存1MB,預計功耗5W。第二代核心「南湖」目標是14nm 2GHz。

性能方面,「雁棲湖」的SPEC CPU2006成績預計在[email protected],也就是7/GHz左右,大約相當於ARM A72/A73的水平,後者商用化的傑出代表包括驍龍835、麒麟960/970等,「南湖」工藝和頻率升級後,預計SPEC 2006得分能到20左右。

據了解,在去年12月的第十六屆「中國芯」集成電路產業促進大會上,中國工程院院士倪光南指出,目前CPU市場主要被x86和Arm架構所壟斷,而中國想要打破這個局面,實現自主可控,開源的RISC-V架構將是一大機遇和發展方向。

在未來世界主流CPU架構格局中,RISC-V架構將有望達到三分天下有其一。

來源:快科技

GPU上集成CPU內核 AMD顯卡部門招聘RISV-C設計師

最近幾年來,開源的RISC-V指令集正在受到各大企業的歡迎,逐漸成為x86、ARM之後的第三大CPU架構,Intel及NVIDIA都已經開始涉足RISC-V處理器,現在AMD也要跟進了,不過這次是顯卡部門率先招聘RISC-V人才。

根據招聘公告,AMD的RTG顯卡部門正在招聘RISC-V設計師,其工作主要為與開發創新嵌入式RISC-VCPU架構工程師團隊合作,解決復雜技術問題,並分析促進多種可能解決方案,幫助團隊在性能、功耗和晶片面積(PPA)進步。

此外還要了解並改善現有和圖形與計算範例,以及採用RISC-V處理器的新API,能與其他架構工程師合作,了解嵌入式處理器提高性能的瓶頸等問題,提出可實行並具最佳PPA特性的創新解決方案,含分析CPU工作負載提出建議等。

這則招聘的特殊之處在於AMD要找的RISC-V設計師不是給CPU團隊的,而是RTG顯卡部門的,所以我們可能看不到AMD品牌的RISC-V產品,但會在AMD未來的某些顯卡上看到RISC-V內核被使用。

在GPU上集成CPU內核其實不算新鮮事了,NVIDIA之前已經嘗試過,可以將RISC-V內核的CPU與GPU搭配使用,負責管理GPU的某些任務,或者用於特殊目的。

在這些領域,高性能的x86內核是沒必要的,RISC-V即可。

來源:快科技

x86、ARM先後封殺俄羅斯:RISC-V成了唯一選擇

繼AMD、Intel先後停止在俄羅斯的銷售業務之後,ARM也於本周六在回答媒體Lightreading提出的問題時,通過電子郵件的形式確認:

「根據英國、歐盟、美國和其他政府宣布出口限制和經濟制裁,ARM已暫停向俄羅斯客戶和或作夥伴提供產品和支持。」

這讓原本計劃將ARM作為為替代方案的俄羅斯雲伺服器公司們猝不及防。

雖然ARM不生產處理器,只是將其晶片IP核出售給博通、Marvell和高通等晶片公司,其客戶還包括AWS在內的數據中心巨頭,但一旦ARM停止在俄羅斯的業務,依賴ARM伺服器的雲服務商們依然會面臨困境。

俄羅斯搜尋引擎公司Yandex在本月初的投資者大會上曾表示:「我們相信,我們目前的數據中心容量和其他對運營至關重要的技術將使我們能夠在至少未來 12 到 18 個月內繼續正常運營,」它在一份聲明中表示,「如果我們的業務或產品中使用的硬體、軟體或其他技術的供應長期暫停,如果我們無法獲得替代來源,未來我們的運營可能會受到重大不利影響。」

x86和ARM都停止供應,目前只剩下RISC-V是俄羅斯唯一的選擇。

RISC-V始於2010年加州伯克利大學,出於對潛在貿易限制的擔憂,RISC-V基金會總部於2020年3月從美國遷移到「中立國家」瑞士,以尋求更加開放開源的生態。與x86和ARM相比,目前的RISC-V尚未建立起完整的生態,在IoT領域表現較好,但還沒有在高性能領域取得比較突出的成績。

此前一位致力於推廣RISC-V的業內人士在曾表示,RISC-V和ARM打成平手,可能還需要5至10年。

目前,俄羅斯技術投資公司Rostoc、伺服器製造商Yadro和設計公司Syntacore等已經致力於RISC-V處理器的研發。

來源:快科技

AMD正在招聘RISC-V架構工程師,未來或將相關技術用於CPU/GPU

近日,AMD的Radeon Technology Group(RTG)正在為現有的嵌入式RISC-V架構團隊招聘一名RISC-V CPU/GPU微架構師。這表明,未來AMD可能會開發基於RISC-V架構的解決方案,用於旗下的相關產品中。

根據AMD的崗位描述,該職位的主要責任分別有:與開發創新嵌入式RISC-V CPU的架構師團隊合作;識別復雜的技術問題,並將其分解,總結多種可能的解決方案,並幫助團隊在性能、功耗和晶片面積(PPA)方面取得進步;了解並改進現有和新興的圖形/計算範例,以及採用RISC-V處理器的新API;與其他架構師合作,了解嵌入式處理器提高性能的瓶頸和其他問題;提出可以在HW中實施的具有最佳PPA特性的創新解決方案;分析CPU工作負載並提出改進建議。

AMD希望該工程師擁有RTL設計經驗、GPU方面的經驗、了解分支預測器和寄存器重命名、亂序執行、推測執行的CPU原理以及RISC-V RV64 CPU等。其工作的地點是美國佛羅里達州的奧蘭多,那里有Radeon Technology Group的一個設計團隊。

事實上,AMD的競爭對手英特爾和英偉達都有關於RISC-V架構的開發工作。英特爾與RISC-V架構晶片設計公司SiFive早已合作,利用對方的技術打造自己的RISC-V開發平台「Horse Creek」,甚至還有意收購對方,未來SiFive的相關IP可以使用英特爾的代工服務業務(IFS)。英偉達部分Turing架構和Ampere架構GPU內部有一個名為GSP(GPU System Processor)的模塊,基於RISC-V架構,用於接管GPU初始化和管理任務等工作,此外Bluefield系列DPU內部也有RISC-V加速器。 ...

英特爾宣布加入RISC-V International,並以10億美元打造代工創新生態系統

英特爾宣布,將投資10億美元建立一個基金,用於支持業界內的企業,為代工生態系統構建顛覆性技術。通過利用英特爾代工服務(IFS),該基金將以投資方式幫助代工客戶加快產品上市時間,范圍涵蓋智慧財產權、軟體工具、創新晶片架構和先進封裝技術。英特爾還會與基金結盟的企業建立合作夥伴關系,通過開放的小晶片平台實現模塊化產品,可支持多種指令集架構,包括x86、Arm和RISC-V。

英特爾CEO帕特-基爾辛格(Pat Gelsinger)表示,代工客戶正迅速地採用模塊化設計方法來區分產品並加快上市時間。藉助英特爾新的投資基金和開放式小晶片平台,可以幫助推動生態系統在全系列晶片架構中開發顛覆性技術,而IFS正在引領行業的重大變革。

此外,英特爾宣布加入RISC-V International,這是一個支持RISC-V指令集架構和擴展的全球非營利組織,其公司成員目前已接近300家。英特爾表示,正在與RISC-V生態系統中的領先合作夥伴聯手,計劃提供一系列經過驗證的RISC-V IP內核,針對不同的細分市場進行了性能優化。通過IFS的工藝技術優化,以確保RISC-V所有類型的內核(從嵌入式到高性能),都處於最佳運行狀態。

英特爾對RISC-V並不陌生,去年還曾有意花費超過20億美元收購SiFive。英特爾發布IDM 2.0戰略後,SiFive就已經宣布會和英特爾展開合作,其相關IP可以使用英特爾的代工服務業務(IFS)。同時英特爾還基於SiFive的Performance P550打造自己的RISC-V開發平台「Horse Creek」,採用7nm工藝製造。 ...

搶台積電生意 Intel投資10億美元進軍代工業:扶植第三大CPU架構RISC-V

2月8日最新消息,Intel宣布,它已經准備了一筆規模可觀的基金,以幫助大公司、小公司、新公司和老公司利用Intel代工服務公司(IFS)打造顛覆性技術。

這筆10億美元(約合63.58億元人民幣)投資基金旨在利用Intel最新的創新晶片架構和先進的封裝技術,加快客戶產品進入市場的時間。此外,它不會對體系架構支持過於挑剔,支持范圍涵蓋x86、ARM和RISC-V等。

作為新CEO基辛格IDM 2.0戰略的一部分,這是Intel再度對向外開放其晶圓代工服務明確示好。Intel還預計其3D封裝技術等允許在一塊晶片產品上集成不同架構,比如x86+ARM這樣的混合模塊化晶片等。

與此同時,Intel宣布成為RISC-V國際成員並加入理事會,希望能推動RISC-V生態發展。實際上,去年10月,Intel就發布了基於RISC-V的晶片Nios Soft處理器。

另外,Intel還正積極推進一項新的晶片互聯標準,就像之前推動USB、PCIe、CXL那樣。

來源:快科技

NVIDIA新驅動解鎖GPU隱藏技能:這下輕鬆了

早在2016年的時候,NVIDIA就宣布正在研究「快速邏輯處理器」(Fast Logic Controller)的替代升級版,一種新的「GPU系統處理器」(GPU System Processor),簡稱GSP,基於RISC-V架構指令集。

此後似乎就沒了下文,但其實,NVIDIA一部分GPU的控制器內核,已經悄悄用上了GSP。

今天,NVIDIA宣布擴大GSP處理器的開放范圍,只需搭配最新的510.39版專業驅動,即可解鎖,並默認開啟。

NVIDIA表示,GSP可用來接管GPU的一部分初始化、管理任務,從而減輕其資源負擔。

事實上,GPU配合驅動、固件來接替CPU執行特定任務,比如視頻編解碼、AI等等,都是由來已久,可以大大提升執行效率,並釋放CPU資源執行其他任務。

這次開放GSP支持的產品主要是數據中心的Tesla系列(當然官方已經不用這個品牌),包括T4、T4G、T10、A2、A16、A30、A40、A100等的各個版本。

來源:快科技

歐洲自研處理器第一階段完成:雙架構、29個RISC-V核心

在高性能計算領域,中美都在沖擊百億億次超級計算,歐洲也不甘落後,發起了自己的EPI(European Processor Initiative)自研處理器項目,集合了10個國家的28個合作夥伴,涵蓋科研機構、超算中心、行業巨頭、創新企業等。

現在,EPI項目的第一階段(2018-2021)已經順利完成,而按照規劃會一直持續到2033年。

EPI項目第一階段包括通用處理器(GPP)、加速器(EPAC)、汽車三個方向,其中第一代通用處理器代號「Rhea」(希臘神話第二代天後瑞亞、大地女神蓋亞與天空之神烏拉諾斯之女)。

對於這顆處理器的技術細節,官方披露並不多,目前只知道是ARM、RISC-V雙重混合架構,前者基於ARM Neoverse V1架構,支持高效、可擴展、可定製的高性能計算應用,後者則有29個核心。

記憶體支持高帶寬的HBM2E,安全方面有獨立開發的安全管理系統(SMS)、Crypto Tile加密模塊、相關算法。

根據此前曝料,Rhea處理器採用台積電7nm工藝,支持6-8通道DDR5、4路HBM2E,其中DDR5支持來自ARM架構,HBM2E支持來自RISC-V架構。

EPAC加速器也是RISC-V架構的,用來輔助通用處理器。

歐洲計劃在2023年發布基於Rhea處理器的歐洲第一台百億億次超級計算機。

來源:快科技

中科院RISC-V開源處理器「香山」第一代核心已流片:性能指標公布

當地時間12月6日,RISC-V峰會在美國舊金山召開,中科院計算所研究員包雲崗攜高性能RISC-V開源處理器「香山」做開場介紹,。

包雲崗研究員在微博分享表示,「雖然有些晚,但這是香山第一次在國際RISC-V社區正式亮相,再晚也值得。」

他還透露,「香山」有了新的歸屬,「香山」出嫁了,至於嫁到哪里,暫時保密,適時會公開,不知道這是否暗示「香山」的商用化已有了方向。

據會上分享的信息,「香山」第一代內核「雁棲湖」已經在7月15日流片,基於28nm工藝,裸片面積6.6平方毫米,單核二級緩存1MB,預計功耗5W。第二代核心「Nanhu」目標是14nm 2GHz。

性能方面,「雁棲湖」的SPEC CPU2006成績預計在[email protected],也就是7/GHz左右,大約相當於ARM A72/A73的水平,後者商用化的傑出代表包括驍龍835、麒麟960/970等,「Nanhu」工藝和頻率升級後,預計SPEC 2006得分能到20左右。

還有聆聽媒體介紹,包雲崗稱,這套RISC-V架構處理器預計每隔6個月就會疊代一次。

來源:快科技

Imagination處理器轉戰RISC-V架構:首發四款產品、最多8核

Imagination,一個老牌的英國晶片IP設計公司,無論CPU還是GPU都曾經赫赫有名,尤其是PowerVR GPU,一度是手機上的標配,也是全球最大的移動GPU公司。

只是隨著時代、形勢的變化,特別是ARM Cortex CPU、Mali GPU逐漸形成壟斷地位,Imagination慢慢沒落了,甚至「賣身」都賣不出去。

現在,Imagination CPU實現了一次華麗的轉身,擁抱了流行的開源架構RISC-V,推出全新的Catapult系列處理器產品。

Imagination表示,RISC-V是一種正在改變處理器設計的開源CPU架構,Imagination的加入將為迅速擴大的RISC-V生態系統帶來更豐富的的產品和解決方案,並特別針對異構計算系統進行了優化,Catapult CPU可根據性能、效率或兩者間平衡等各種應用場景進行配置,使其適用於更廣泛的市場。

Catapult系列首發就有四款不同的產品,分別是:動態微控制器、實時嵌入式CPU、高性能應用處理器CPU、支持汽車功能安全的CPU。

其中,微控制器已被客戶用於SoC晶片中的GPU模塊,開始出貨;實時嵌入式CPU現已上市;高性能應用處理器CPU、汽車CPU將於2022年開始陸續上市。

Catapult CPU專為5G基帶、存儲、輔助駕駛和自動駕駛、數據中心、高性能計算等市場打造,均採用多線程架構,有32位、64位兩種版本,並提供大量的可選項,客戶可根據每種應用的需求進行配置,比如擴展到每個集群8個非對稱相干內核,還可選擇添加自定義加速器。

Catapult CPU主要功能:

- 全面的創新設計,RISC-V生態系統的全面支持。

- 作為Imagination完整的異構計算解決方案的一部分,與其行業領先的GPU、人工智慧神經網絡加速器(AI NNA)、乙太網數據包處理器(EPP)內核一樣重要。

- 為使用Imagination IP內核的異構SoC提供全面的硬體、軟體和調試支持

- 為汽車和工業領域提供功能安全性解決方案

- 符合行業經過驗證的安全防護理念,同時可滿足目標市場對安全性和認證的要求

- 由一家成熟公司提供,在提供復雜IP解決方案方面有著20年的專業經驗,並擁有強大的支持能力

Imagination同時還提供了功能齊全的SDK開發包,包括增強版的、符合行業標準的構建和調試工具,比如GCC、LLVM和GDB、優化的C庫。

它可用於Windows、Ubuntu、CentOS、MacOS、FreeRTOS等作業系統,也全面支持Linux,包括參考引導加載程序、內核和基於Yocto的文件系統。

還有新的開發工具Catapult Studio,擁有自己的IDE集成開發環境,以Visual Studio Code為基礎,同時具有專注於嵌入式的、RISC-V開發的附加功能,並可與來源更廣泛的SDK緊密集成,從而使開發人員能夠充分利用Catapult CPU的優勢。

來源:快科技

Imagination發布全新Catapult系列:基於RISC-V架構的處理器IP

Imagination Technologies宣布推出全新Catapult系列,這是基於RISC-V架構的處理器IP產品線,以滿足下一代異構計算需求而設計。Imagination表示,其Catapult系列CPU在RISC-V架構基礎上,針對性能、能效或平衡等多種不同需求進行配置,以適用於更廣泛的市場。

作為業界的老兵,Imagination在提供IP解決方案方面有著超過20年的經驗。通過開源的RISC-V架構生態系統,讓Imagination能快速地增加和擴展Catapult系列產品線。目前Catapult產品線下有四個系列,包括動態微控制器、實時嵌入式CPU、高性能應用CPU和車用功能安全CPU。其中動態微控制器已被客戶所採用,在高性能車用GPU上得到應用;實時嵌入式CPU也已上市;高性能應用CPU和車用功能安全CPU的相關產品將會在2022年跟進,後者根據ISO 26262車輛規范標準開發,具有功能安全性和安防性能。

據Imagination介紹,Catapult系列專為5G數據機、存儲、ADAS/自動駕駛汽車、數據中心和高性能計算等市場而設計,擁有多線程,分為32位和64位兩種版本。可根據客戶應用場景的需要提供可選配置,最多擴展到每集群有八個非對稱相干內核,加速器也可以自定義添加,可以與Imagination的GPU、AI和神經網絡加速器內核搭配使用。

此外,Imagination還提供了Catapult系列配套的SDK,其中包括了GCC、LLVM和GDB等工具的增強版本、優化的C庫、以及Catapult Studio。Catapult SDK適用於Windows、Ubuntu、CentOS和MacOS,包括有參考引導加載程序、內核和基於Yocto的文件系統。 ...

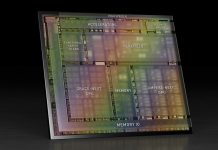

SiFive推出全新Performance P650,進一步提高RISC-V架構CPU性能上限

基於開源RISC-V架構的晶片設計公司SiFive宣布,推出新的SiFive Performance系列處理器P650。SiFive表示,Performance P650是「目前市場上性能最強的可授權RISC-V架構處理器IP」。

SiFive Performance P650最多可配備16個內核,其設計是以P550為基礎,保持高效的流水線,同時擴展處理器指令發射寬度,以實現40%的IPC性能提升。通過增強架構,Performance P650相比上一代性能最強的旗艦產品Performance P550整體性能提高了50%。SiFive表示,相比Arm Cortex-A77,有明顯的單位面積性能優勢。

目前SiFive沒有透露Performance P650的具體頻率和設計細節,此前Performance P550採用13級流水線、三發射、亂序執行的微架構,每個核心擁有自己的32KB一級指令緩存、32KB一級數據緩存、二級緩存,單個叢簇最多4核心,共享4MB三級緩存,支持Linux以及完整的RISC-V矢量擴展v1.0rc。英特爾還藉助Performance P550,打造了自己的RISC-V開發平台「Horse Creek」,甚至有可能是英特爾首發的7nm產品。

SiFive聯合創始人兼首席技術官Yunsup Lee表示,SiFive響應了半導體行業對更多處理器IP的呼籲,專注於將基於RISC-V架構的處理器技術推向市場。自今年早些時候發布Performance系列內核以來,不斷尋求機會突破性能極限,而SiFive Performance P650兌現了一直以來持續提高性能的承諾。

SiFive Performance P650預覽版將會在2022年第一季度向頭部合作夥伴提供,到了年中會有相關產品上市,為數據中心、移動、車載、邊緣計算等領域提供有力的支持。 ...

搶食ARM份額 PCIe 5.0硬碟主控用上RISC-V架構:速度14.6GB/s

ARM是低功耗晶片中的王者,近年來還想著搶x86處理器的高性能市場份額,不過ARM也有自己的麻煩,那就是開源的RISC-V。在高性能SSD主控上,韓國公司FADU就使用RISC-V而非ARM架構,實現了PCIe 5.0 x4高性能。

韓國初創公司FADU日前宣布了自研的PCIe 5.0主控晶片FC5161,主要用於數據中心,支持PCIe 5.0 x4通道,讀取速度14.6GB/,寫入也有10.4GB/,隨機讀取IOPS高達340萬,隨機寫入IOPS也有73.5萬。

目前PCIe 5.0硬碟還比較少,東芝之前公布的新品性能甚至只有PCIe 4.0的水平,FADUA的這款PCie 5.0主控的性能可以說是目前最強的之一了。

快科技獲悉,他們的FC5161主控採用的內核也公布了,不是常見的ARM架構,而是SiFive公司的S5系列RISC-V內核,專門為嵌入式市場設備的。

在FADU公司之前,雖然RISC-V內核也被用於硬碟主控,但之前主打的多是低功耗,性能達到PCIe 5.0頂流水準的非常少,這對RISC-V的推廣很有幫助。

來源:快科技

拿下RISC-V處理器告吹:消息稱Intel未能就127億收購與SiFive達成一致

在x86和ARM之外,RISC-V開源指令集已經悄然成長為CPU架構的第三極。

前不久有消息稱,Intel拋出橄欖枝,想花費20億美元(約合127億元)收購RISC-V處理器開發商SiFive,但財經媒體最新爆料稱,計劃已經流產。

據悉,此次協商是在私下進行,遺憾最終沒能達成一致,看起來主要的分歧較多,包括SiFive未來如何融入Intel以及具體交割的資產分配等。不過,SiFive方面仍在考慮未來進行IPO或者尋求更大的收購方。

對於Intel來說,x86晶片的體量局限在每年3.5~3.6億顆的出貨,而冉冉升起的RISC-V可以給自己補充新鮮能量,從而競爭同樣是精簡指令集的ARM。要知道,ARM晶片的全球累計出貨已經超過2000億顆。

來源:快科技

EPI 首個 CPU 原型 EPAC1.0 已經到來 :RISC-V 架構和 22nm 工藝

在處理器方面,不僅中國和美國需要自主研發,歐洲也不願意受制於人。法國等 10 個國家聯合發起了歐洲處理器計劃 (EPI), 自行開發高性能處理器 。EPI 的第一個 CPU 原型 EPAC1.0 已經到來,採用 RISC-V 架構和 22nm 工藝。

歐洲 EPI 處理器計劃已經進行了好幾年,其中一個就是為歐盟的 HPC 超級計算機開發自己的處理器,但進展緩慢,原型 EPAC1.0 直到現在才出現。

EPAC1.0 處理器採用混合架構 ,CPU 內核是...

首款歐洲自主研發CPU亮相:RISC-V架構、22nm工藝、頻率1GHz

在處理器上,不僅中國、美國要自主研發,歐洲也不甘受制於人,法國等10個國家聯合組建了歐洲處理器計劃(European Processor Initiative :簡稱EPI),要自己開發高性能CPU。現在EPI首個CPU原型EPAC1.0來了,使用的是RISC-V架構,22nm工藝。

歐洲的EPI處理器計劃已經進行了數年,目的之一就是為歐盟的HPC超算開發自己的處理器,不過此前進展緩慢,原型EPAC1.0直到現在才亮相。

EPAC1.0處理器採用了混合架構,CPU內核是SemiDynamics開發的Avispado,基於開源的RISC-V架構,有4個核心,VPU矢量單元則是由巴塞隆納超級計算機中心(西班牙)和薩格勒布大學(克羅埃西亞)聯合開發的。

其他還有L2緩存、STX張量加速器、VRR可變精度計算模塊以及法國開發的SerDes網絡模塊。

從這些單元來看,EPAC1.0處理器的設計還是很先進的,集成了眾多專用的加速器,不過實際性能沒有曝光。

EPAC1.0處理器使用的是格芯22nm工藝製造的,核心面積只有27mm2,不過頻率只有1GHz,應該是測試用的,首批產量只有143個,目前已經跑通程序。

下一代EPAC處理器則會升級12nm工藝,並採用先進的小晶片布局。

來源:快科技