近日,AMD正式發布了,面向伺服器、數據中心、高性能計算、人工智慧等領域。

此前,我們已經介紹了EPYC 9004系列的型號規格、整體特性、性能能效,但是關於它,還有很多層次的東西可以挖掘,包括架構、SoC、記憶體、小晶片、CXL等等。

今天,我們就來仔細說道說道。

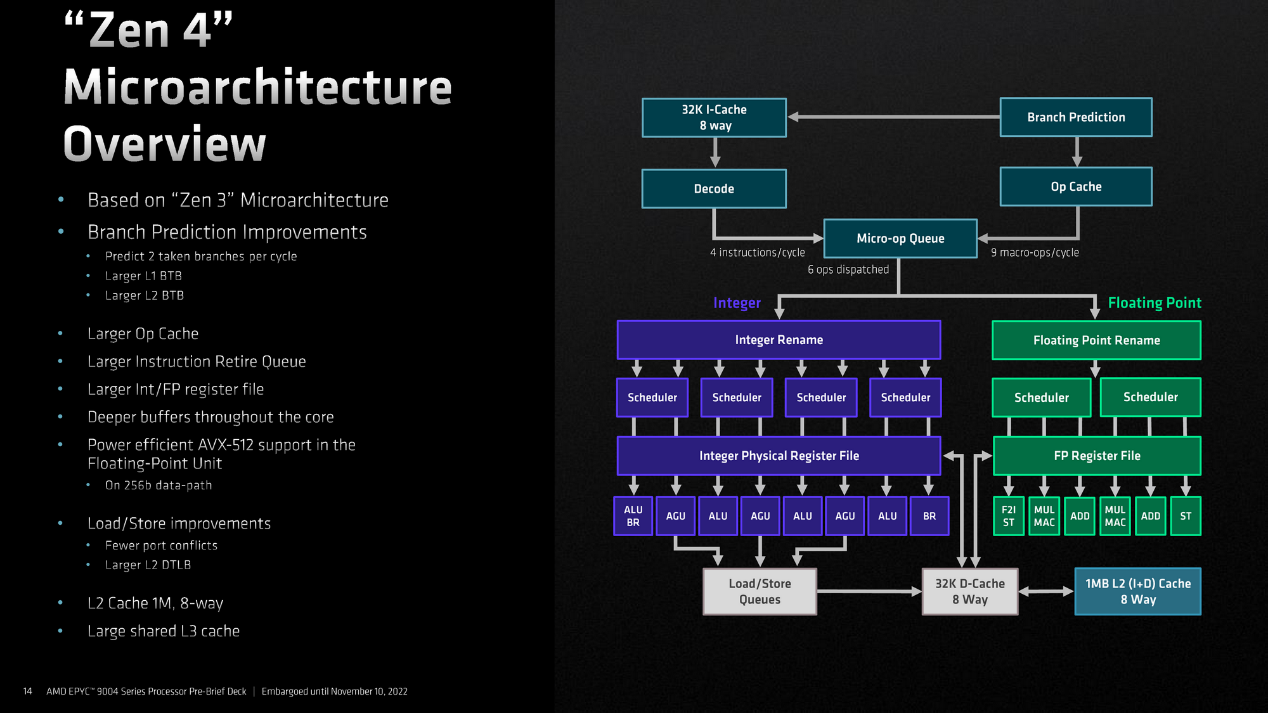

一、Zen4架構

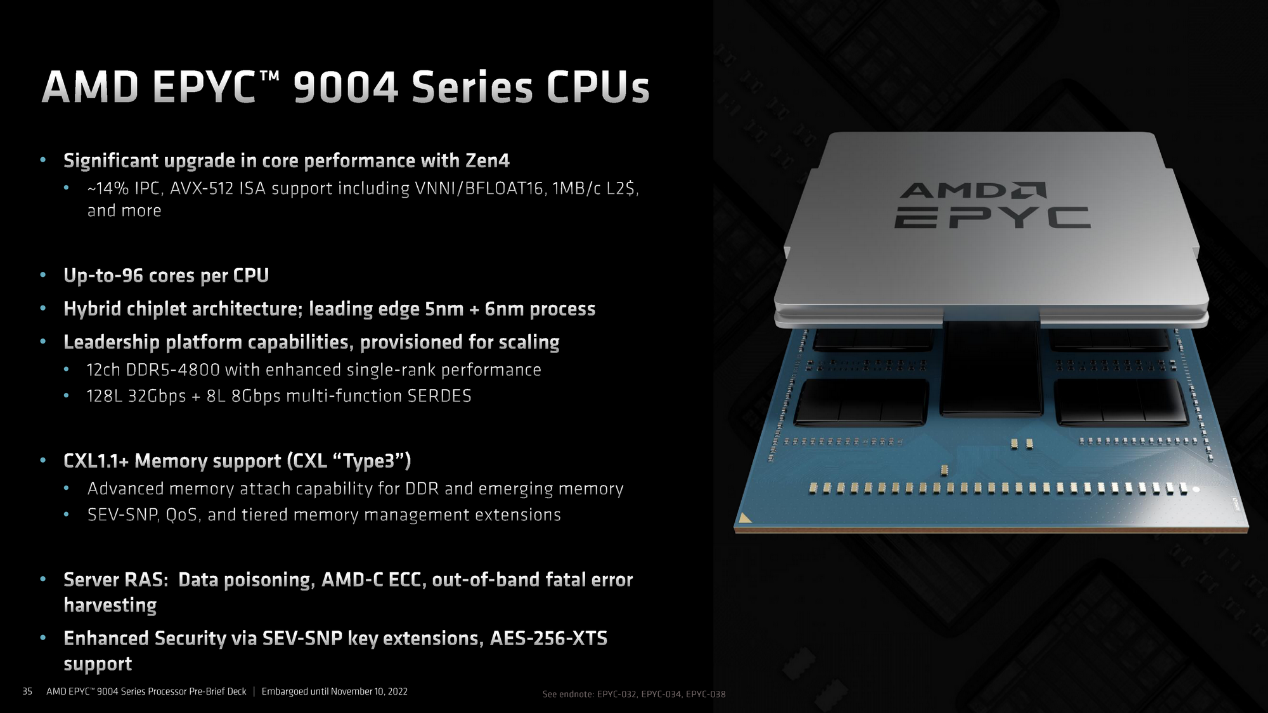

EPYC 9004系列基於和桌面銳龍7000系列同款的Zen4架構,只是針對伺服器與數據中心應用做了適當的調整優化。

整體而言,綜合計算33種不同的伺服器負載,Zen4架構的IPC相比Zen3提升了大約14%,這比銳龍7000系列的提升高了1個百分點。

不同模塊的貢獻差不多,最大的還是前端部分,接下來是載入/存儲、分支預測、執行引擎、二級緩存。

架構總覽,以及與Zen3的變化細節對比,都和桌面版Zen4幾乎毫無二致。這里也就不再贅述了,

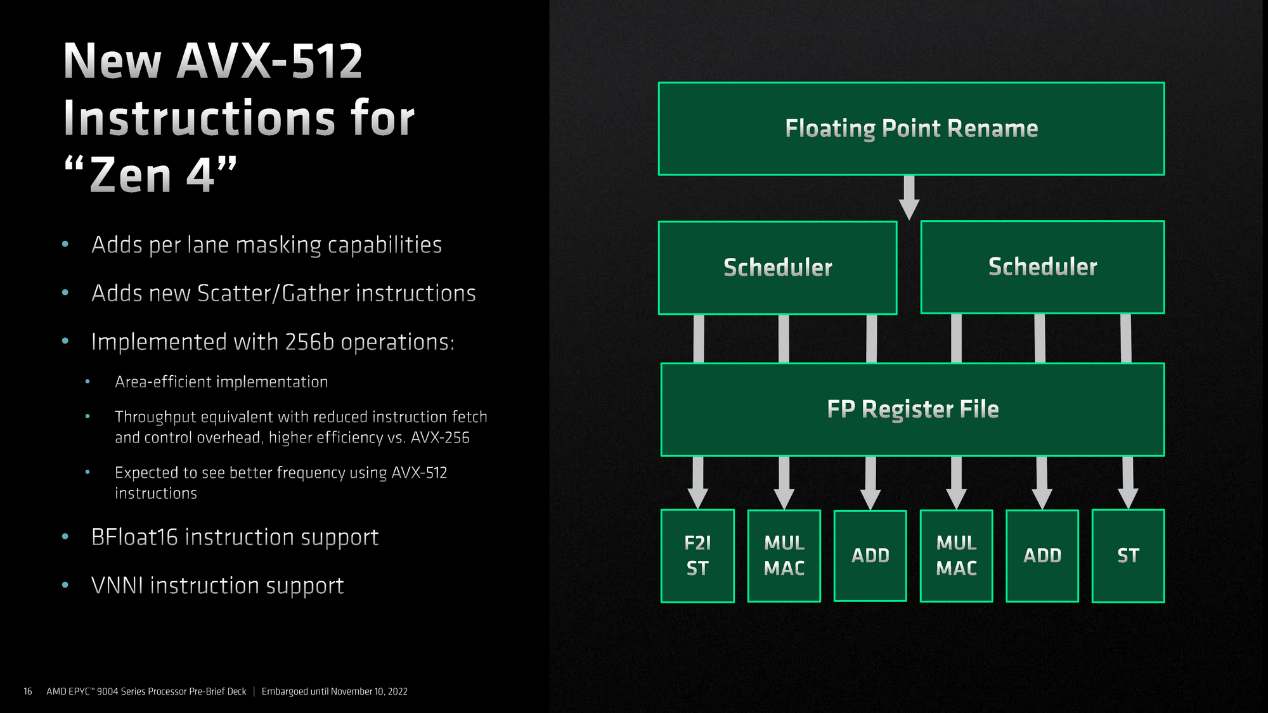

AVX-512指令集其實也是一模一樣的,但它在伺服器數據中心顯然更加如魚得水,作用更加明顯。

根據AMD提供的數字,雙路96核心新旗艦EPYC 9654對比雙路64核心老旗艦EPYC 7763,得益於規格性能的改進,尤其是AVX-512指令集的加持,NLP吞吐量、物體檢測吞吐量、圖像識別吞吐量分別增加了大約4.2倍、3.5倍、3倍之多!

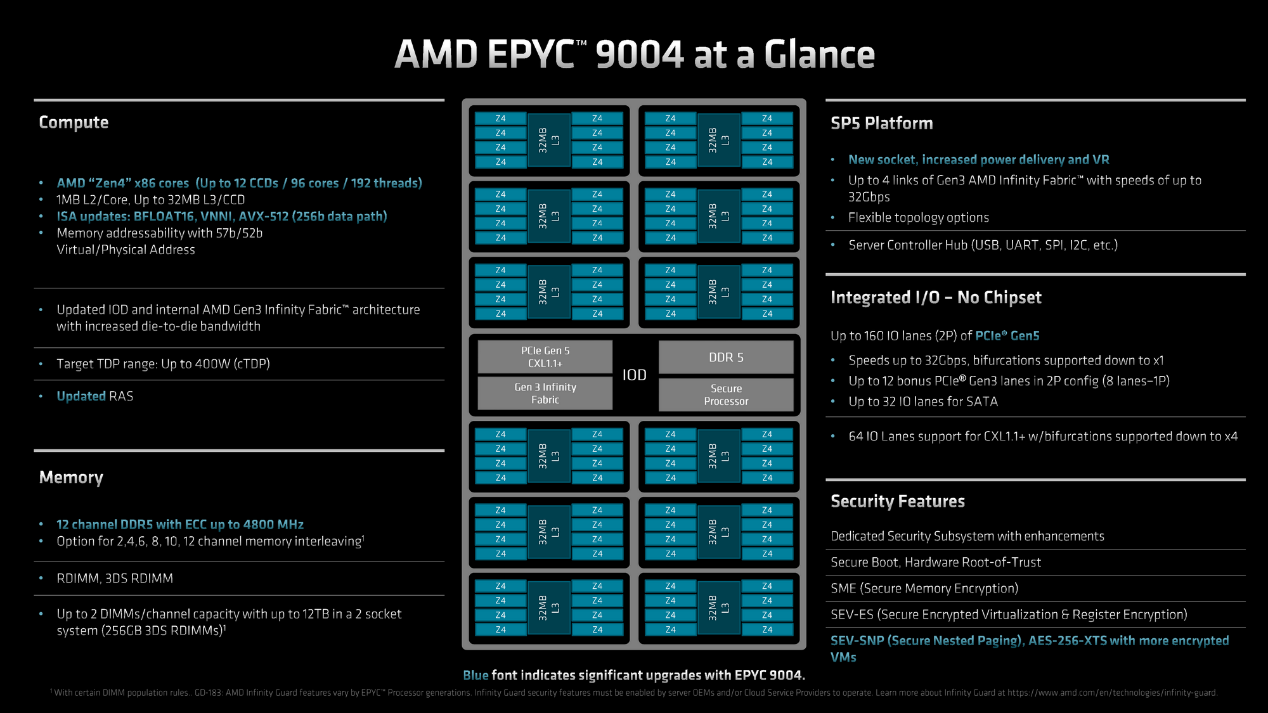

安全方面也更豐富,其中安全加密虛擬化(SEV)方面,除了繼續支持SME、SEVES、SEV-SNP,還將記憶體加密升級到AES-256-XTS,並支持1006個加密客戶機,支持多重主機密鑰(SMKE)。

另外強化了對客戶機的保護,尤其是可免於SMT攻擊。

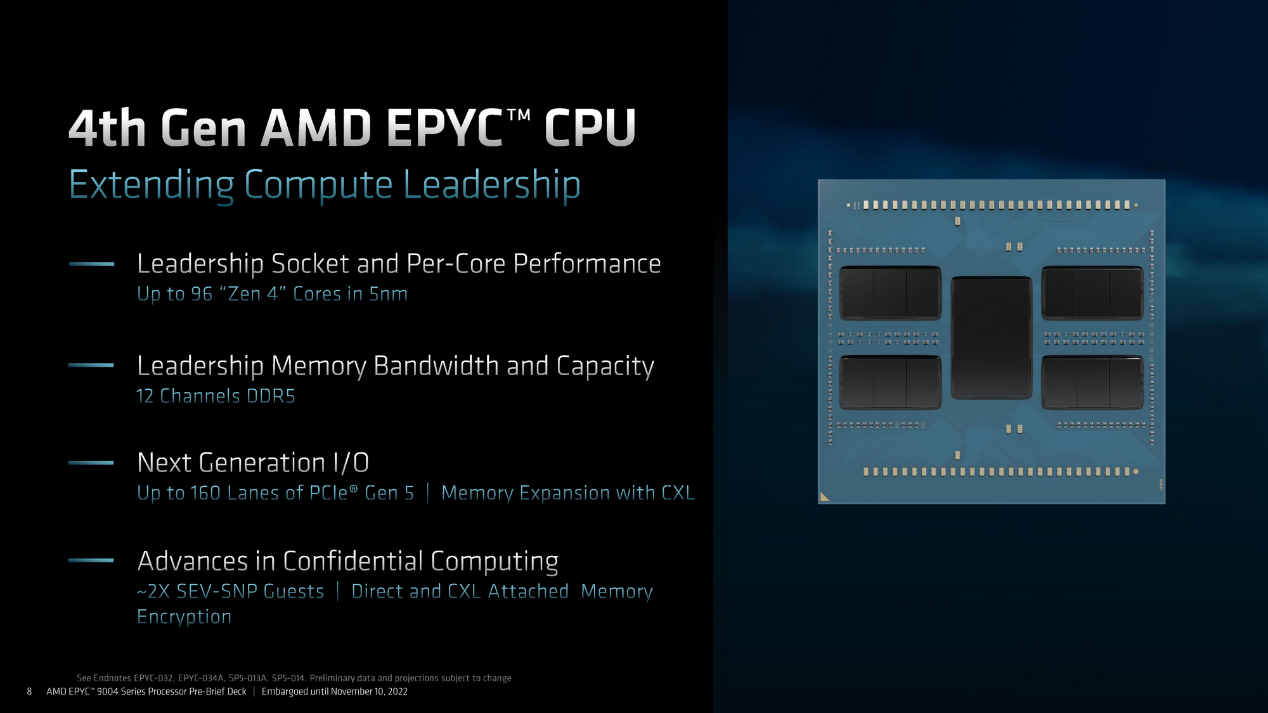

二、SoC總覽

這是EPYC 9004系列額整體布局圖、核心特性。

這一代依然沒有獨立晶片組,而是一個完整的SoC,延續chiplet小晶片設計,內部包含一個IOD、最多12個CCD。

CCD每個集成8顆Zen4 CPU核心、32MB三級緩存,合計最多96核心、384MB三級緩存,同時也有8個CCD、4個CCD的版本,分別最多64核心、32核心。

IOD內集成了DDR5記憶體控制器、PCIe 5.0/CXL 1.1+控制器、第三代Infinity Fabric控制器、安全處理器。

記憶體為12通道,最高頻率4800MHz。PCIe 5.0可提供128條。這兩部分後邊細說。

封裝接口改為新的SP5,尺寸增加到約75×72毫米。

單路配置下,EPYC 9004系列可搭配最多24條DDR5記憶體,每通道2條(2DPC),可提供128條PCIe 5.0、8條PCIe 3.0通道。

雙路配置下,每個記憶體通道就只能裝1條了(1DPC),最多還是12條,PCIe 5.0通道對外可用則是最多160條,每路80條對外、48條用於彼此互連,另外還有12條PCIe 3.0,每路6條。

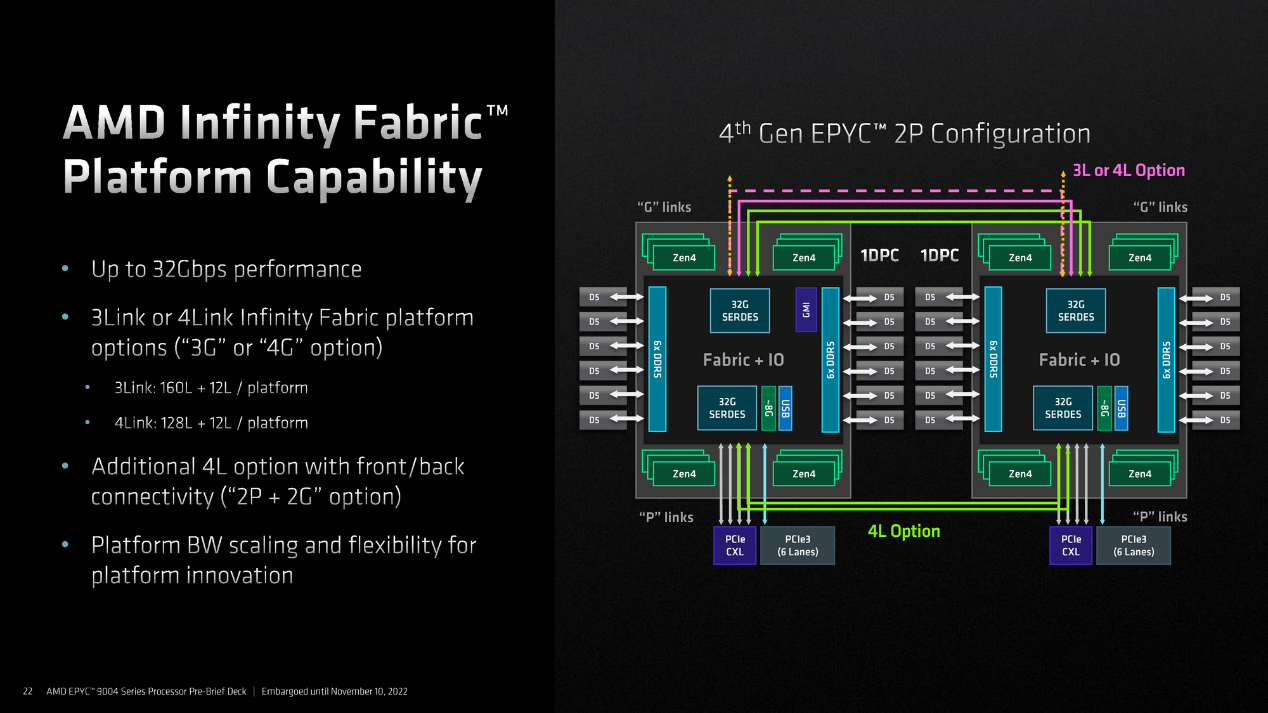

IF高速總線升級到了第三代,最高帶寬32Gbps,可選3條或4條連結,前者是默認的,此時對應的系統可用PCIe 5.0通道數量就是剛才說的160條。

如果選擇4連結,每路處理器就要貢獻一半的PCIe 5.0通道用於彼此互連,留給系統可用的就是128條,這和上代是相同的。

當然,即便同樣128條,從PCIe 4.0升級到PCIe 5.0,可用帶寬也是翻倍的。

160條之多的PCIe 5.0通道能幹什麼?那就很隨意了。

xGMI、PCIe、SATA、CXL想怎麼玩就怎麼玩。x16、x8、x4、x2、x2想怎麼拆分就怎麼拆分。每一路x16都可以連接最多9個PCIe設備(一個x8和八個x1)。

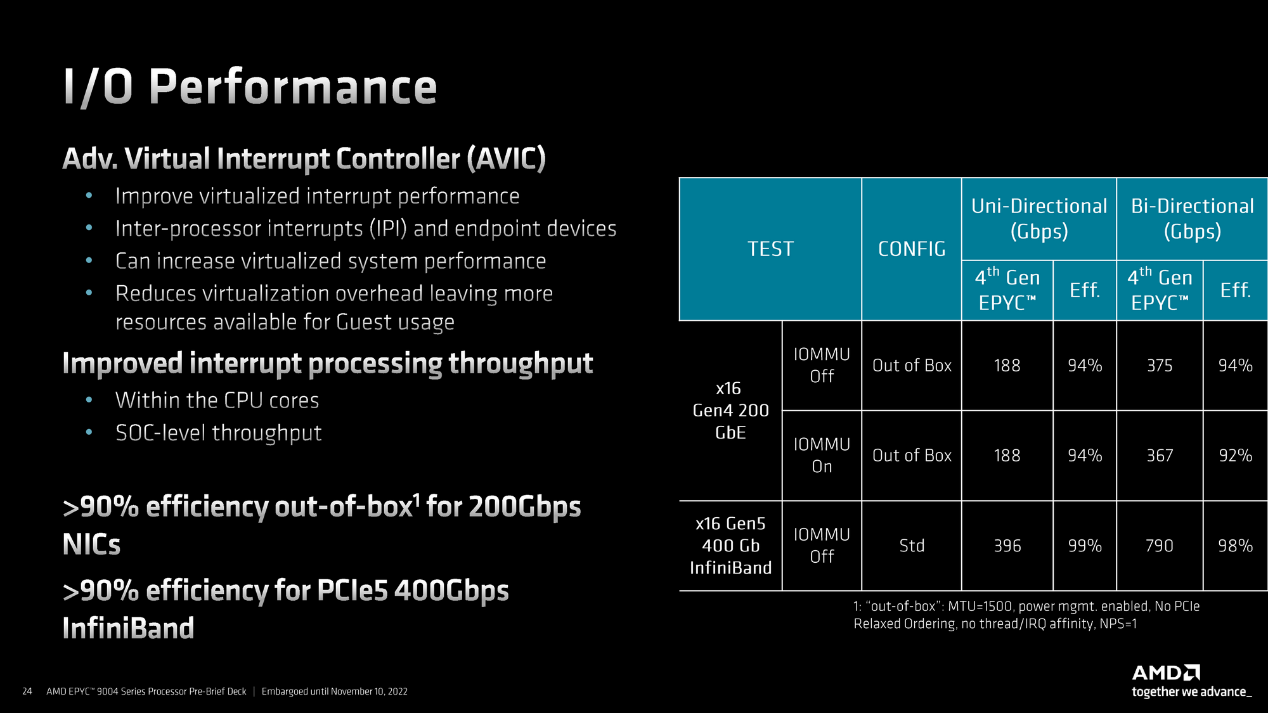

I/O性能方面,EPYC 9004支持新的高級虛擬中斷控制器(AVIC),提升虛擬中斷性能,並改善了中斷處理吞吐量,包括CPU核心內部與SoC層面。

搭配PCIe 4.0 x16規格的200Gbps(20萬兆)網卡,默認設置下效率即可超過90%,最高達94%,單向能跑到188Gbps,雙向則能跑到375Gbps。

如果搭配PCIe 5.0 x16規格的400Gbps(40萬兆) InfiBand高速網絡,標準配置下效率也能超過90%,最高甚至達99%,能跑出396Gbps。

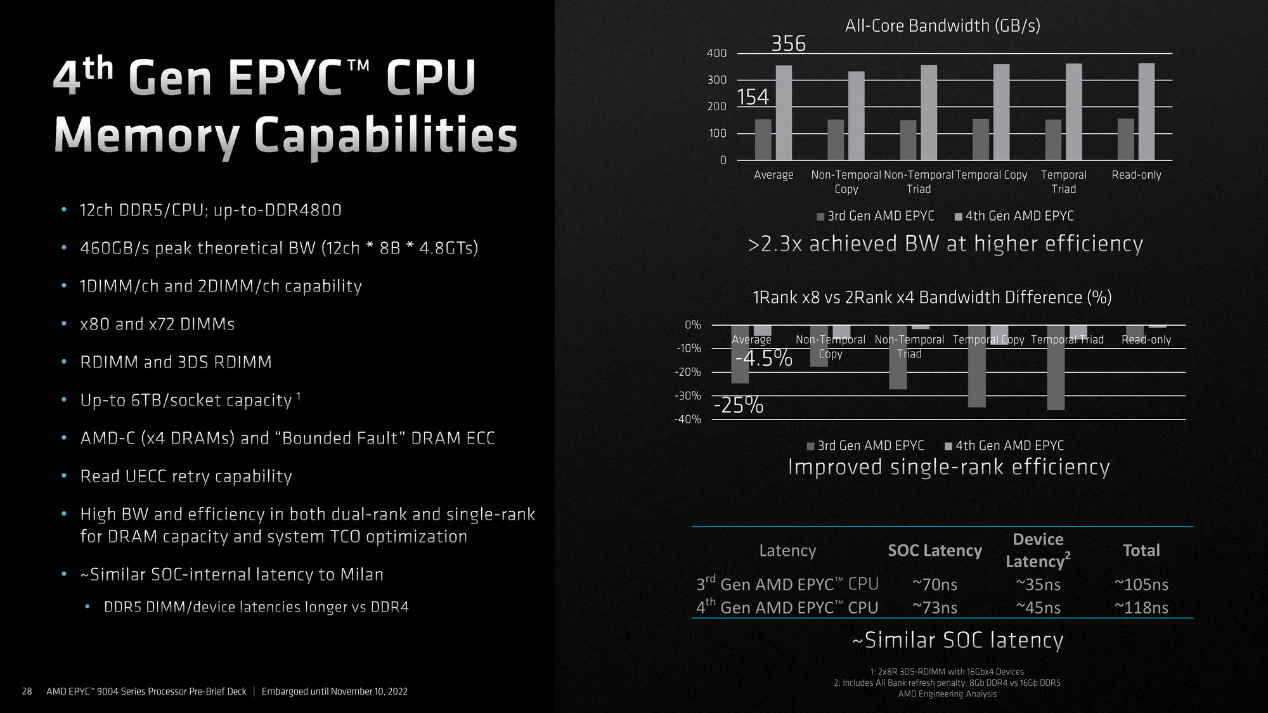

三、記憶體

記憶體方面,一如桌面銳龍7000系列,EPYC 9004也僅支持DDR5,可以帶來更高的頻率與帶寬、更低的電壓與功耗、更好的電源管理(板載PMIC)、更多的通道與更低的延遲、更大的容量、更好的校驗糾錯(板載ECC),等等。

EPYC 9004系列支持12個DDR5記憶體通道,單路最大容量6TB(單條512GB)。

標準的4800MHz頻率下,峰值理論帶寬可達460GB/。

延遲方面,EPYC 9004略有增加,但影響不大,其中SoC約73ns、設備約45ns,總計約118ns,比上代分別增加了3ns、10ns。

EPYC 9004還支持每路多重記憶體節點(NPS),可以對12條記憶體進行分組管理,進一步優化性能。

四、小晶片布局

EPYC 9004依然是chiplet小晶片布局,其中CCD最大數量從上代的8個增加到12個,布局更加緊密,對帶寬、延遲也提出了更高的要求。

為此,小晶片間的通信通道升級為GMI3,最大帶寬達到36Gbps,吞吐能力翻番,同時與內部基準頻率的比例為20:1。

針對不同數量的CCD,GMI還提供寬、窄兩種模式,其中超過4個CDD為寬模式,充分利用足夠的帶寬,小於等於4個則是窄模式,提高效率。

五、CXL

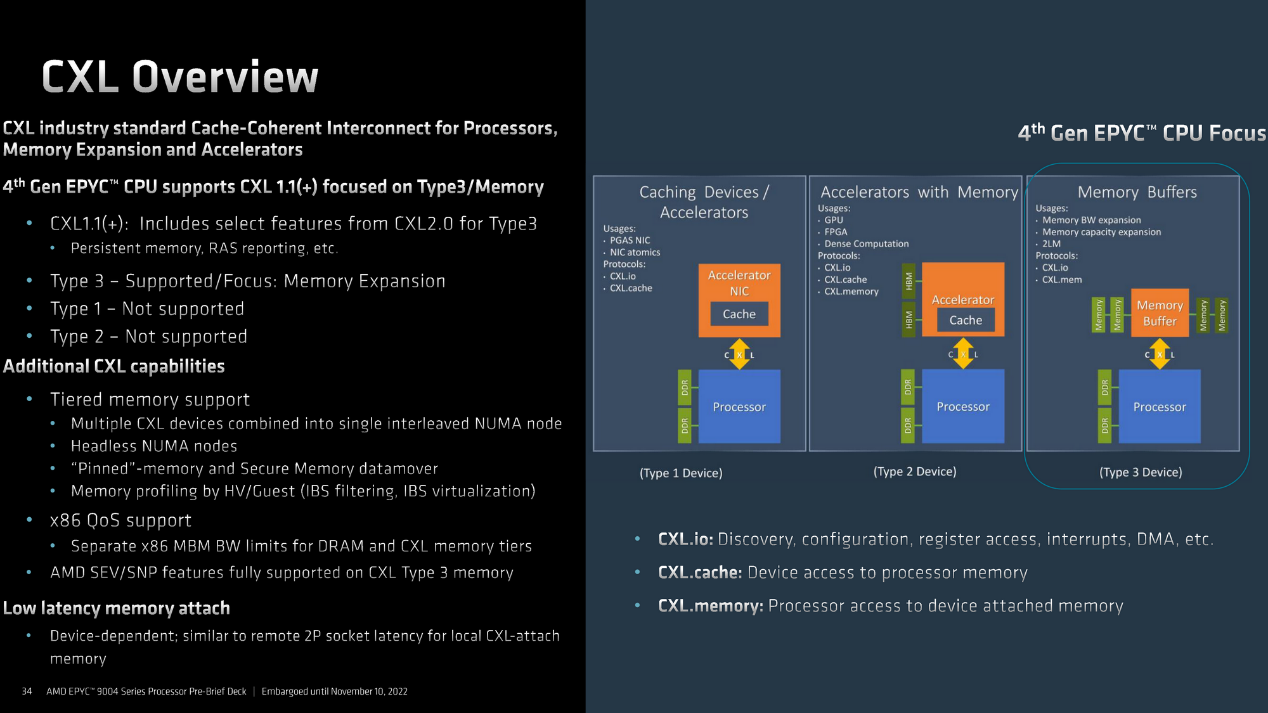

CXL,也就是Compute EXpress Link,一種緩存一致性高速互連行業標準,主要用於處理器、記憶體擴展與加速器。

CXL有三種工作模式,EPYC 9004並不支持第一種(面向NIC網卡)、第二種(面向GPU/FPGA/加速器等密集計算),而僅支持第三種,也就是記憶體緩沖,可擴展記憶體帶寬與容量,協議走的是cxl.io、cxl.mem。

總的來說,AMD EPYC 9004系列在延續chiplet設計的同時,升級了工藝、架構,升級了記憶體、擴展連接等,整體規格、特性上了一個大大的台階。

此外,Zen EPYC家族還會陸續還會推出採用3D V-Cache技術的更高性能版“Genoa-X”,面向雲計算服務的“Bergamo”(貝爾加莫),以及面向電信基礎設施和邊緣計算的“Siena”(錫耶納),組成完整的產品矩陣。

未來的第五代“Turing”(圖靈)家族,還會再次升級全新的“Zen5”架構!

來源:快科技