11月9日消息,RISC-V伺服器晶片設計廠商Ventana Micro Systems在2023RISC-V峰會上發布了其第二代伺服器CPU——Veyron V2,在指令擴展、內核設計、互聯標准、製程工藝等眾多方面進行了全面升級。

官方宣稱其性能超越了AMD的高端伺服器晶片Epyc 9754,堪稱最強RISC-V伺服器CPU!同時,Ventana還能夠讓客戶將定製加速器添加到定製片上系統 (SoC) 藍圖中。

早在2022年12月,Ventana公司就曾發布了全球首款基於RISC-V架構的伺服器CPU——Veyron V1。

採用5nm製程工藝,基於Ventana自研的高性能RISC-V內核,8流水線設計,支持亂序執行,主頻超過3GHz,每個集群最多16個內核,多集群最多可擴展至192核,擁有48MB共享三級緩存,擁有高級側信道攻擊緩解措施、IOMMU和高級中斷架構(AIA)、支持全面的RAS功能、自上而下的軟體性能調整方法,可以滿足數據中心的各種需求。號稱性能可超越AMD EPYC 7763!

根據Ventana的計劃,Veyron V1將於今年下半年上市,但是截至目前仍未有客戶選擇採用。這或許也是為什麼Ventana急於推出Veyron V2的原因。

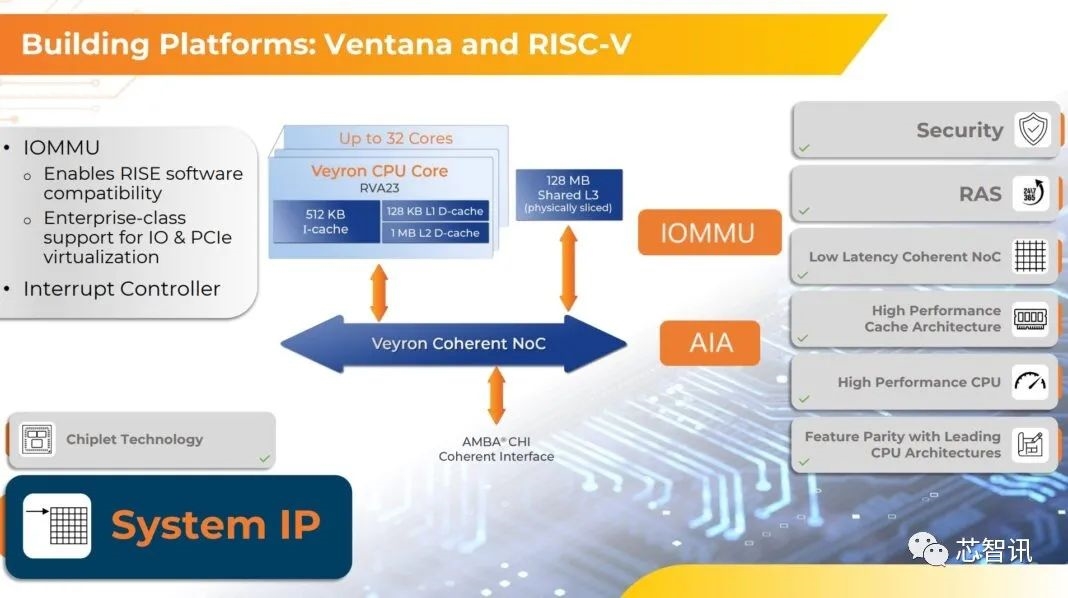

據Ventana 營銷和產品副總裁 Travis Lanier介紹,全新的Veyron V2將融入RISC-V規范中的所有更新,比如RVA23功能集,這是今年的RISC-V最新的指令集配置文件,實現了RISC-V輸入輸出記憶體管理單元(IOMMU)規范,同時還支持小晶片的UCIe互聯標准。

Lanier表示,IOMMU 規范的批准“在 RISC-V 領域是一件大事”。“只要您擁有虛擬機,並且想要直接訪問其中一個 PCIe 設備,您就不必執行所有軟體開銷來切換它,因此這對於數據中心應用程式來說是一項關鍵功能。”

Veyron V2也希望成為一種基於RISC-V標準的兼容性設計,因此 RISE 支持很重要。

“這也是RISC-V軟體生態計劃(RISE)兼容性的關鍵部分,這是一個行業項目,旨在圍繞RISC-V構建必要的應用生態系統。”Lanier進一步解釋道。

Ventana還利用RISC-V矢量擴展規范在其核心中添加了512位矢量處理單元,還具有 AI 矩陣擴展功能。Lanier聲稱這將“對某些生成式 AI 或推理工作負載有很大幫助”。

另外,對於DSA和Chiplet標准UCIe的支持,使得他可以更快地製造晶片,並且可以讓客戶添加 FPGA,添加 ASIC 加速器等。這增加了靈活性,但也降低了進入門檻,因為它允許使用使用 UCIe 和 I/O 集線器的較小 IP 塊來構建軟體包。

Ventana聯合創始人兼執行長Balaji Baktha在RISC-V峰會上也表示,Ventana客戶可以使用其智慧財產權和其他智慧財產權在Veyron V2 上創建的潛在CPU設計。

具體到Veyron V2的核心配置方面,基於台積電4nm工藝,依然是基於8流水線設計,支持亂序執行,主頻高達3.6GHz,單個集群的內核數量提升到了32個,相比上一代提升了一倍,多集群最多可擴展至192核。緩存的大小也增加到每個核心1MB二級緩存,以及128MB 的共享集群級三級緩存。

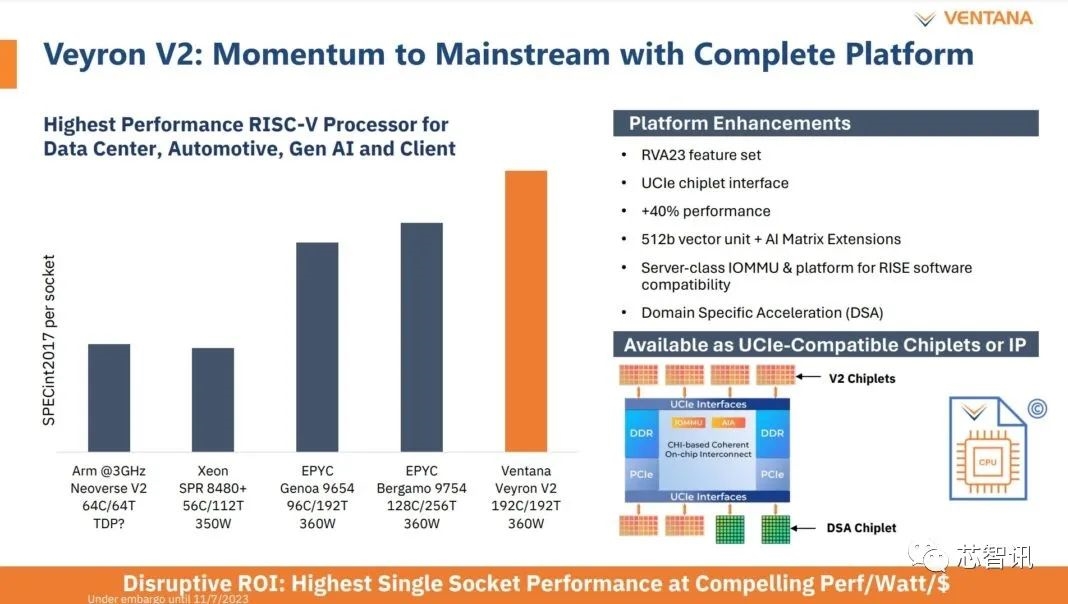

Lanier聲稱,Veyron V2 的所有新的升級使得其性能相比上一代提高了近40%。官方提供的性能預測數據顯示,192核的Veyron V2性能超越了AMD高端伺服器晶片Epyc 9754!

下面對於Veyron V2幾大關鍵升級進行詳細介紹:

互聯標準的轉變

VeyronV2 的一個重大轉變是將支持作為Chiplet(小晶片)連接標準的UCIe(UniversalChiplet Interconnect Express)標准,而不是上一代的VeyronV1中的BoW(Bunch of Wires)接口互聯總線協議標准。

據了解,BoW協議是一個開放的標准,由開放計算項目中的開放域特定架構小組控制。

包括Ampere Computing、阿里巴巴、AMD、Arm、思科系統、戴爾、Eliyan、富達投資、高盛、谷歌、惠普企業、IBM、英特爾、聯想、Meta Platforms、微軟、諾基亞、英偉達、Rackspace、希捷科技、Ventana和Wiwynn都支持BoW,這種廣泛而廉價的晶片到晶片互連協議,使跨工藝和供應商混合小晶片的承諾成為現實。

但是在2022年3月,英特爾、AMD、Arm、高通、台積電、三星、日月光、Google雲、Meta(Facebook)、微軟等十大行業巨頭成立了Chiplet標准聯盟,正式推出了通用Chiplet的高速互聯標准“UCIe”,旨在定義一個開放的、可互操作的標准,用於將多個矽晶片(或芯粒)通過先進封裝的形式組合到一個封裝中。

UCIe 標准希望與其他連接標准(如 USB、PCIe 和 NVMe)一樣普遍,同時為Chiplet連接提供卓越的功率和性能指標,降低IP移植及產品SKU數量提升的成本,加速Chiplet設計的創新。

雖然HPE、IBM和Nvidia等大廠並沒出現在最初的創始名單當中,但最終他們也加入了UCIe聯盟。

Balaji Baktha表示,其在與46家現有的和潛在的客戶討論Veyron V1和V2 CPU設計時,很明顯,UCIe是小晶片互連的發展方向。因此,Ventana公司加快了Veyron V2的發布,其中包括大量的RISC-V核心增強,因為它採用了UCI Express而不是BoW進行小晶片互連。

以下是BoW、AIB 2.0和UCIe 1.1互連的比較,這是Lei Shan撰寫的一篇論文的補充。Lei Shan曾在IBM TJ Watson研究中心從事互連硬體工作,現在在Arm伺服器晶片新創公司Ampere Computing工作:

正如您所看到的,UCIe的數據速率是BoW的兩倍,總線帶寬可以相同或高出4倍。信道覆蓋范圍是UCIe距離的一半,但鏈路的功率效率提高了兩倍,延遲不到BoW的一半,每毫米的帶寬也高出35%到65%。

Balaji Baktha表示:“如果晶片設計者想使用小晶片,他們必須支持UCIe”。

“UCIe背後有著巨大的推動力,因為每個人都想要一個統一的標准。BoW本可以成為這樣一個標準的。但我們不想繼續構建它,因為UCIe標准有效地解決了封裝成本,並且正在以最佳水平實現。UCIe還解決了3D記憶體堆疊問題。

因此,利用UCIe很容易實現Express 2.0,並利用我們自己的專業知識彌合與UCIe 1.0之間的差距。例如,UCIe根本沒有提供到AMBA CHI一致接口總線的連結。因此,我們在UCIe 2.0上添加了AMBA功能。”

支持512位矢量擴展

Ventana希望迅速抓住,並將其納入Veyron V2核心設計的另一個重大變化是RISC-V Vector 1.0 512位矢量擴展。

該擴展類似於英特爾至強Phi處理器從2015年開始提供的擴展,以及2017年在“Skylake”至強SP處理器中提供的擴展。

一年前,該擴展也剛剛被添加到AMDGenoaEpyc處理器中。這些512位矢量引擎實際上並不是英特爾AVX-512的克隆(就像AMD Genoa晶片中的那些至少在軟體級別上),但它們足夠接近,不會給想要將代碼從X86移植到RISC-V的Linux開發人員帶來一場軟體噩夢。

此外,512位矢量擴展將為HPC和AI工作負載提供與X86和Arm處理器有競爭力的性能,在這些工作負載中,CPU將進行AI計算,而不是像GPU和其他加速器一樣在CPU上或CPU外部使用加速器。

Ventana為VeyronV2核心添加了512位矢量擴展,使矢量引擎能夠支持矩陣運算,並允許客戶將自己的矩陣引擎添加到架構中,無論是在核心中還是在使用UCIe鏈路的離散小晶片中與之相鄰。

順便說一句,VeyronV1核心沒有任何向量引擎或矩陣引擎擴展,這顯然是一個問題,因為許多人工智慧推理仍在CPU上進行,在某些情況下,人工智慧訓練和HPC模擬和建模也在CPU上完成。

全新的內核架構

Veyron V2設計的另一個重大變化是Ventana創建了一個顯著改進的RISC-V內核架構。

通過在Veyron V2核心中更積極地融合指令處理並進行許多其他調整,Ventana已經能夠將一攬子工作負載的每時鍾指令(IPC)性能提高20%。

與3GHz主頻的Veyron V1內核相比,Veyron V2主頻也提高到了3.6 GHz,這將內核的性能再提高了20%,從而在Ventana的Veyron RISC-V CPU內核設計中,從V1內核到V2內核的整體性能提高了40%。

Veyron V2核心是基於台積電4nm工藝設計的,相比上代基於台積電5nm工藝的Veyron V1得到了進一步提升。

VeyronV2內核還支持RVA23體系結構配置文件,該配置文件強制使用512位矢量擴展。還有一些在矢量引擎上運行的加密函數。

Ventana的VeyronV2內核還支持RV64GC規范,並實現了一個超標量、無序流水線,每個時鍾周期可以解碼和調度多達15條指令。由於其IOMMU設計和高級中斷體系結構(AIA),VeyronV2核心可以支持類型1和類型2的伺服器虛擬化管理程序以及嵌套虛擬化。

Veyron V2核心還具有用於調試、跟蹤和性能監控的埠。

以上所有這些都是現代超大規模數據中心伺服器CPU所應有的能力。

V1和V2內核都沒有同時的超線程,就像亞馬遜雲和Ampere Computing的Arm內核沒有,未來“Sierra Forest”Xeon SP處理器中使用的“Siera Glen”內核也沒有。

另外,Veyron V2內核具有512 KB的L1指令緩存和128 KB的L1數據緩存以及1 MB的L2數據緩存。這些內核還有一個4MB的L3緩存,與之相關的是,在Veyron V2的小晶片復合體中的32個內核中,總共擁有128MB的L3緩存。

每個小晶片上的核心使用專有的片上網狀網絡相互連接,該互連為CPU核心、記憶體和其他I/O提供了高達5TB/秒的聚合帶寬。

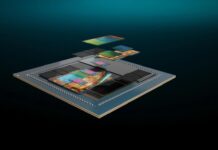

四個VeyronV2小晶片可以與UCIe互連,以創建一個128核的復合體,如果你真的想突破極限,你可以將最多六個小晶片連接在一起,獲得192核。

以下是基於VeyronV2內核的CPU的概念圖,它有一個I/O管芯和六個32核VeyronV2小晶片,以及一些特定於領域的加速器連結:

上圖顯示了I/O集線器與PCI Express 5.0控制器和DDR5記憶體控制器的連結,但如果Ventana公司願意,可以換成HBM3記憶體控制器。

默認設計為六個VeyronV2小晶片上有十二個DDR5記憶體控制,四個VeyronV2小片上有八個,這與我們目前在任何伺服器CPU中看到的配置是一樣的。

性能超越AMDEpyc 9754

Ventana的VeyronV1發布之時,號稱性能超越AMD EPYC 7763。那麼Veyron V2的性能又能有多強呢?

以下是Ventana如何模擬Veyron V2的整數性能,以及每個插槽的原始SPECint2017性能:

按照Ventana公布的數據來看,一個192核的Veyron V2 RISC-V CPU的整數吞吐量將比AMD“Bergamo” Epyc 9754處理器高23%,該處理器在相同的360瓦功率范圍內有配備了128核和256線程;

同樣,Veyron V2也比96核的AMD“Genoa” Epyc 9654高了34%左右;與56核的Intel “Sapphire Rapids”Xeon SP 8480+相比,Veyron V2性能更是達到了其2.7倍。

這並不奇怪,因為VeyronV2有3.4倍的內核和1.7倍的線程,盡管VeyronV2內核必須以較低的時鍾速度運行;

另外一款基於Arm Neoverse V2的64核產品似乎的是亞馬遜雲(AWS)Graviton3的替代品,擁有64核心,性能比IntelSapphire RapidsXeon SP 8480+芯略高,但是也僅為Veyron V2的一半不到。

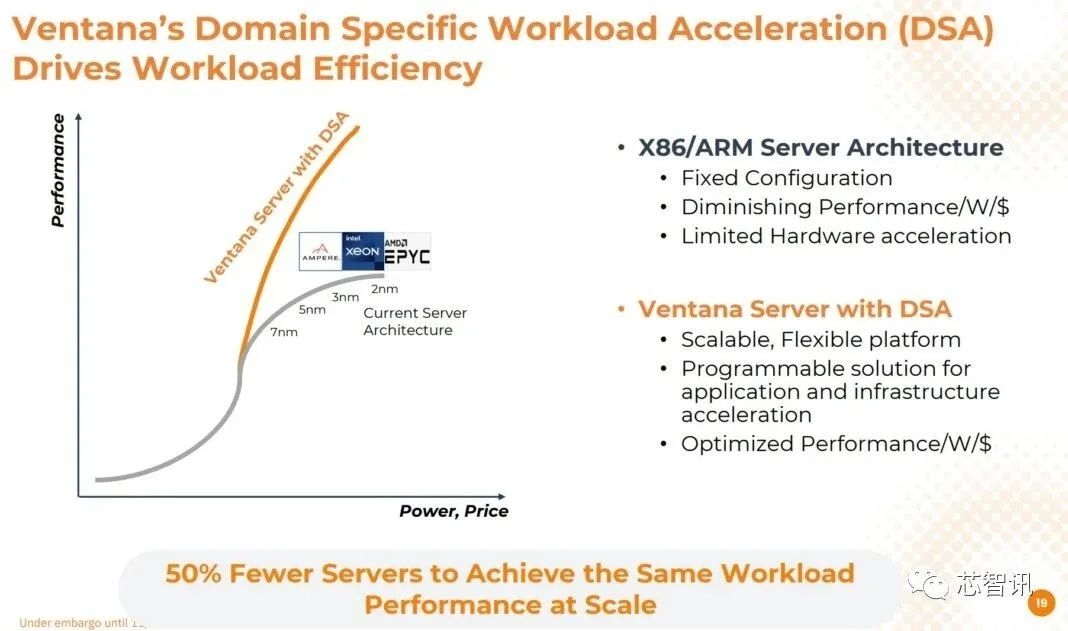

支持DSA

Veyron V2還支持 DSA(面向某個特定的領域定製優化的設計),該功能允許客戶向其 SoC 添加定製加速器晶片。

Lanier 表示,這是針對可能希望提高數據中心特定工作負載的超大規模客戶,例如壓縮和加密、網絡中的 TCP 卸載處理或資料庫中的鍵/值處理。這些加速器小晶片由 Veyron V2內核通過 Ventana 添加的自定義指令提供支持,這是整個 RISC-V 架構的一大賣點。

在這種情況下,自定義指令使軟體能夠調用加速器,這可以看作是英特爾處理器使用指令調用浮點單元 (FPU) 的方式的回響,當時其中一個是可選的單獨的浮點單元 (FPU)。

總結來說,Ventana 的目標是讓其客戶設計使用這些 DSA 小晶片(無論是 FPGA 還是 ASIC)來提供更好的工作負載效率,而不僅僅是最大 SPECint 吞吐量。

安全性大幅提升

Veyron V2 的另一個特色是,支持全面的RAS,具有ECC能力、防數據中毒等。

如今,數據中心處理器還需要具有安全啟動和身份驗證能力。Veyron V2設計也能夠更好地抵禦側信道攻擊,例如Spectre 和 Meltdown缺陷,這些缺陷可能導致伺服器記憶體中的數據被竊取。

不過,Lanier強調,這並不意味著Veyron V2晶片不可能被此類攻擊,只是 V2 在設計時就了解了這些攻擊的執行方式,可以在一定程度上進行預防。“數據中心客戶為受影響的伺服器運行軟體補丁或緩解措施的成本通常可能會降低 10% 甚至 20% 的性能。”

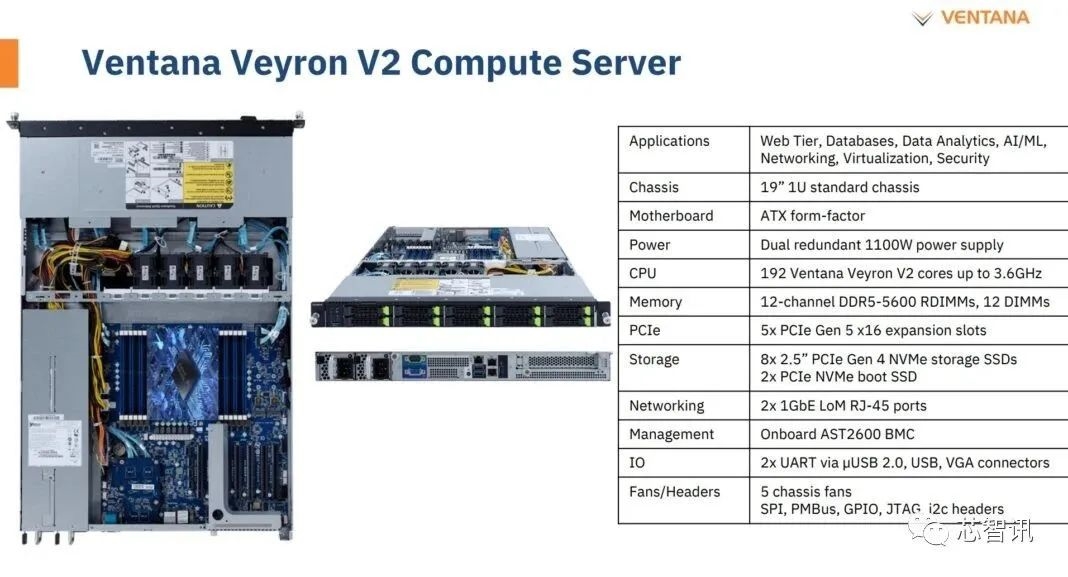

2024年第三季度投入生產

Ventana還將提供基於Veyron V2的192 核 1U 伺服器參考設計,有四個128核的小晶片和12通道的DDR5-5600記憶體,小晶片上有UCI Express互連,還有一個I/O接口,可以將它們放在伺服器CPU插槽內。

據介紹,Veyron V2將於2024年第三季度投入生產,屆時用於互連小晶片的UCIe 1.1 PHY有望上市。

編輯:芯智訊-浪客劍

資料來源:

https://www.theregister.com/2023/11/07/ventana_riscv_server/

Ventana Veyron V2 RISC-V CPU Launched for the DSA Future

Ventana Launches Veyron V2 RISC-V Into The Datacenter

來源:快科技