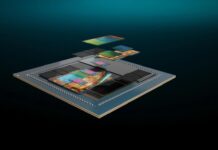

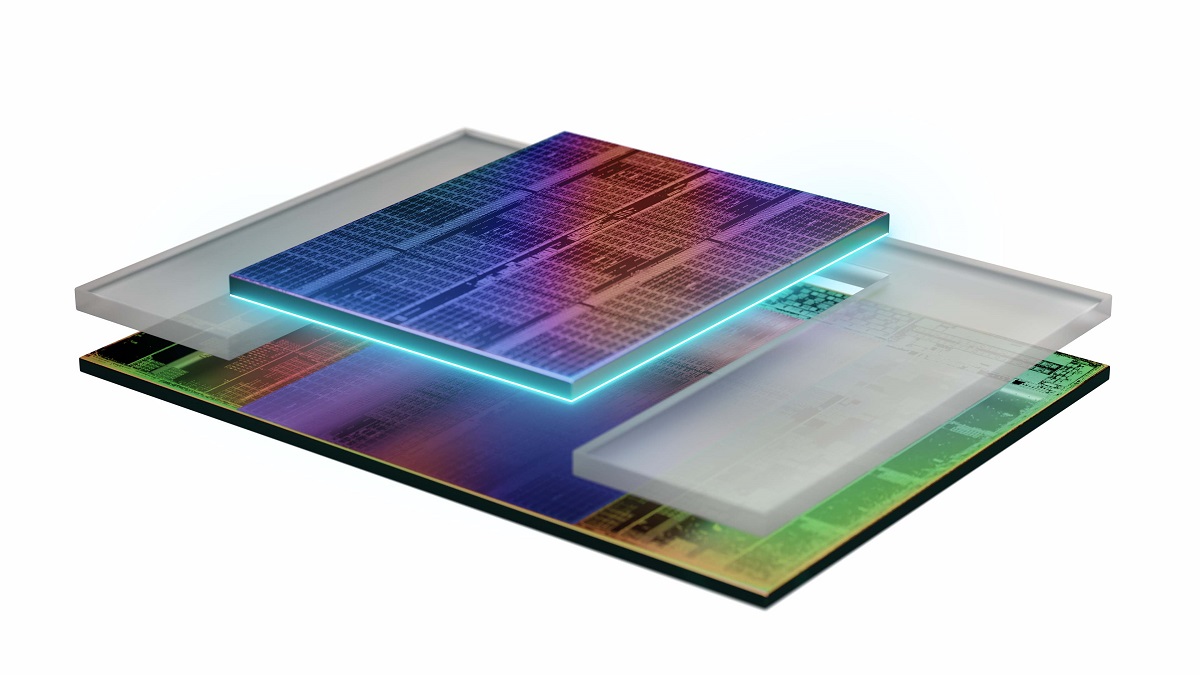

目前AMD採用3D垂直緩存(3D V-Cache)技術的Zen 4架構桌面處理器已經開始銷售了,Ryzen 7000X3D系列處理器相比原有的普通型號,L3緩存容量均增加了64MB,成為了當今最好的遊戲處理器。不過AMD並沒有在Ryzen 7000X3D系列處理器材料中分享第二代3D V-Cache的細節,直到最近的ISSCC 2023里,才提供了一些具體的信息。

據TomsHardware報導,在第一代3D V-Cache里,AMD使用了7nm製造的SRAM晶片堆疊在同樣7nm製造的Zen 3架構CCD上,而Zen 4架構CCD採用的是5nm工藝,會造成一些不匹配,為此AMD需要進行一些修改。

首先7nm的SRAM晶片變得更小,尺寸由41mm2縮小至36mm2,電晶體總數保持約47億個,因此密度會更高。SRAM晶片也缺乏典型的緩存控制電路,這有助於減少延遲。額外的L3緩存會增加4個時鍾的信號延遲,不過帶寬已增加至2.5TB/s,相比之前第一代3D V-Cache的2TB/s提高了25%。

SRAM晶片通過兩種類型的矽通孔(TSV)連接基礎晶片,供電TSV在小晶片之間傳輸電力,而信號TSV在單元之間傳輸數據。在第一代3D V-Cache設計中,兩種類型的矽通孔都在CCD的對應L3緩存區域內,不過由於Zen 4架構CCD採用的是5nm工藝,基礎晶片的密度增加使得L3緩存區域變更小,即便新款SRAM晶片變得更小,也會與L2緩存出現重疊。

為此AMD將供電TSV移到了L2緩存區域,信號TSV仍在L3緩存區域。對於基礎晶片,AMD在L3緩存、數據路徑和控制邏輯上實現了0.68倍的有效面積縮放,通過對第一代3D V-Cache的優化改進,將L3緩存里的矽通孔區域縮小了50%,以減少新接口設計中的額外電路。

AMD的3D垂直緩存技術是基於台積電(TSMC)的SoIC技術,作為一種無損晶片堆疊技術,意味著不使用微凸點或焊料來連接兩個晶片,矽通孔可以在沒有任何類型的粘合材料的情況下進行匹配。第二代3D V-Cache在連接方面採用了基本相同的工藝,雖然做了改進,但最小TSV間距沒有改變。此外,SRAM晶片與處理器內核保持在同一功率區域,無法獨立調整,電壓不能超過1.15V,所以小晶片的頻率也不會太高。

AMD在ISSCC 2023上還展示了Ryzen 7000系列和EPYC處理器使用的6nm工藝IOD的大量細節,由於代號Genoa的EPYC處理器需要連接多達12個CCD,所以對應的IOD也十分地巨大。相比之下,消費級的Ryzen 7000系列處理器局限於兩個CCD,這是一個不可改變的限制,因為對應的IOD只有兩個GMI3互連接口連接CCD,所以最終限制了處理器的核心數量。

此前我們已經對Ryzen 9 7950X3D進行了評測,更大的L3緩存使其成為了當今最好的遊戲處理器,想了解更詳細內容可以點擊《銳龍9 7950X3D天梯榜首發評測:大緩存就是給力,當前最佳遊戲處理器》閱讀。

來源:超能網