英特爾早在幾個月前就確認了Lakefield處理器,這款處理器最重要的技術就是英特爾的Foeveros 3D封裝技術,可以將不同架構、工藝的核心封裝在一起,提供了極大地靈活性。在近日的Hot Chips 31會議中,英特爾也將一些技術細節公布出來。

根據Tom’s Hardware的報導,英特爾在Hot Chips 31進行了Lakefield處理器的技術講解。在幾個月前英特爾已經公布了一些規格,包括Lakefield處理器猜就得是1個大計算核心+4個小核心,構成了類似於ARM的big.LITTLE架構形式。3D堆疊讓處理器的集成度更高。英特爾稱Lakefield處理器主要目標是開啟全新規格的移動計算設備,並為這些設備提供較強性能的同時保證低TDP,做到持續在線及非常低的待機功耗。而第一代就是Lakefield。

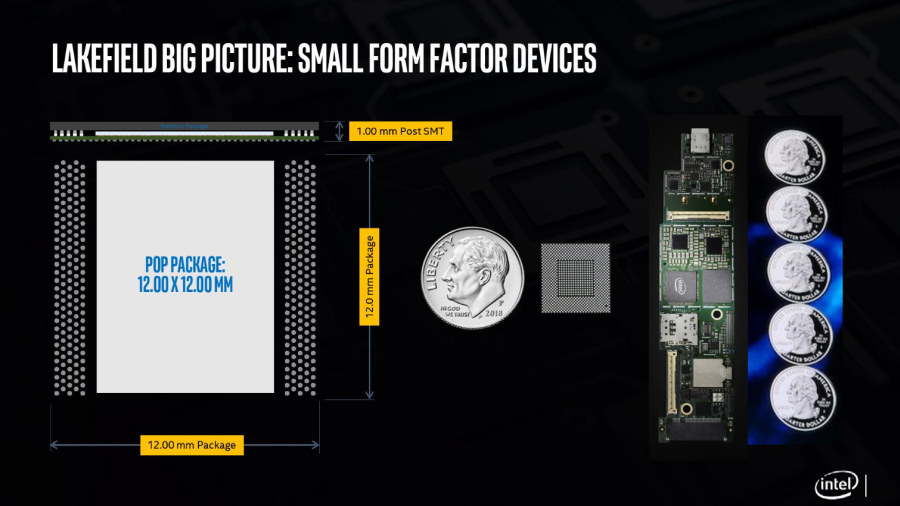

Lakefield處理器的封裝大小為12×12mm,厚度為1.00mm,大小與一枚硬幣相仿。可在極小的PCB上實現完整的計算平台。

對比之前的處理器尺寸,新的Lakefield處理器要小不少,對比SkyLake-U第一代Y系列處理器,Lakefield僅為其40%大小。採用POP封裝的LPDDR4及LPDDR4X記憶體。電源管理也改為了PMIC。

除了3D封裝帶來的好處外,英特爾稱3D封裝最重要的好處可以用不同的工藝適配不同的模塊,以發揮出不同工藝的優勢。比如低漏電P1222工藝用於基礎Die,10nm的工藝用於計算Die。在12×12mm的封裝之上就是基礎層,這一層主要為音頻、USB、UFS等接口。在基礎層之上英特爾並沒有直接放置計算層,而是放了一層Die,分隔計算層和基礎層。英特爾的計算層中包含了CPU核心及GPU核心、這部分採用了英特爾的10nm+工藝製造。在計算層之上就是DRAM層。各層間通過TSV矽穿孔技術提供電力和I/O傳輸。

在計算層,英特爾使用了一個基於Sunny Cove架構的大核心以及四個基於Tremont的Atom核心。通過大小核的搭配既保證了性能,也保證了效率。英特爾也展示了在Web瀏覽時大小和的調度情況。

降低待機功耗也是英特爾Lakefield處理器的一大目標,相比第六代Core處理器,Lakefield處理器在待機狀態下的功耗僅為其8%。

圖形性能也是英特爾提升的主要目標,在Lakefield處理器中,英特爾也使用了與第十代Ice Lake處理器相同的Gen11 GPU,也採用了64個EU設計,不過主要針對低功耗,所以頻率上應該要低一些。

Lakefield處理器作為第一批英特爾3D封裝的處理器,主要用於低功耗、二合一或雙屏設備。現在Lakefield處理器已處於生產准備就緒的最後階段,將在今年四季度提供樣品。到明年我們就見到採用該處理器的產品了。

來源:超能網