大概在一個月前,PCI-SIG宣布PCIe 6.0已經到了0.9版本,相當於最終草案階段。目前PCI-SIG成員正在對技術進行內部審查,以確保其智慧財產權和專利。除非出現重大問題,否則不允許進行任何功能上的修改,相關企業也可以開始在產品中採用PCIe 6.0。

近日,Cadence(楷登電子)宣布推出PCIe 6.0 IP測試晶片設計套件,讓晶片開發人員能夠在其設計中實現對PCIe 6.0的支持並進行測試,其支持Cadence的智能系統設計戰略(Intelligent System Design),實現了SoC的卓越設計。據Cadence介紹,早期的開發人員已開始探索新一代的PCIe 6.0規范,利用Cadence和台積電(TSMC)的技術,或許會在2022年-2023年加入到晶片設計中。

這款面向PCIe 6.0 IP測試晶片設計套件包括基於DSP的高性能PHY和功能豐富的配套控制器,為為超大規模計算和5G通信的新一代應用提供優化的性能和吞吐量。在今年7月份,Cadence的PCIe 6.0子系統測試晶片在台積電N5製程節點上完成流片,其集成了第二代功耗、性能和面積(PPA)優化的PCIe 6.0 PHY與PCIe 6.0控制器。

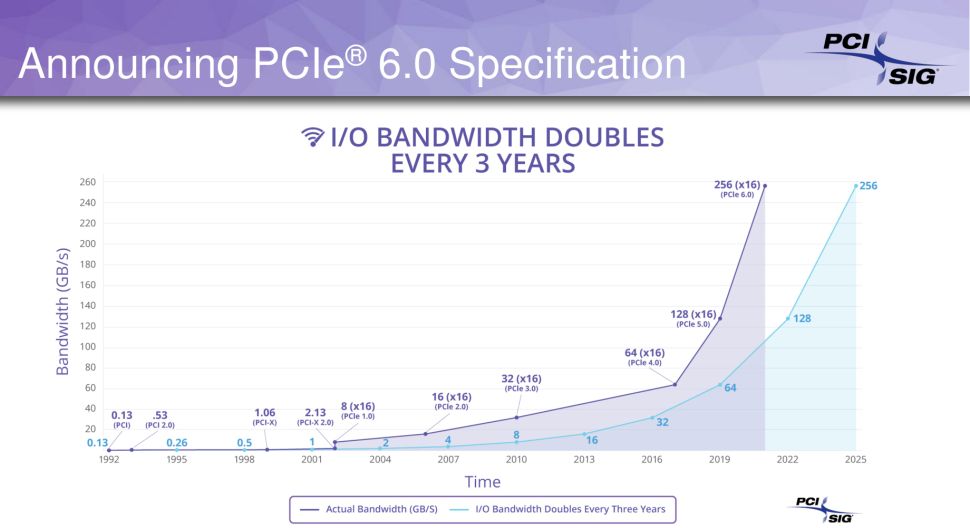

在PCIe 6.0規范中,數據傳輸速率從PCIe 5.0的32 GT/s和PCIe 4.0的16 GT/s提高到每引腳64 GT/s,PCIe 6.0 ×16通道單向理論數據傳輸速度達到了128 GB/s(雙向256 GB/s)。為了提高數據傳輸速率和帶寬,新接口採用了四級脈沖振幅調制(PAM4)信令,這種信令也被用於像InfiniBand這種高端網絡技術以及GDDR6X記憶體等地方。此外,PCIe 6.0還採用了低延遲前向糾錯(FEC),以確保高效率運行。

來源:超能網