Tag: PCI Express

PCI-SIG發布CopprLink線纜規范:適用於PCIe 5.0和6.0標准

去年11月,PCI-SIG在美國丹佛科羅拉多會議中心舉行了SC23會議,向成員展示了PCIe技術演示和新的PCI快速線纜命名方案,強調了PCIe技術是高性能計算互連的首選。PCI-SIG表示,PCIe內部和外部線纜新命名方案為「CopprLink」,相關規范正在制定當中,將滿足PCIe 5.0和PCIe 6.0標準的使用要求。

現在PCI-SIG終於發布了CopprLink內部和外部線纜規范,適用於PCIe 5.0和PCIe 6.0標准,提供了32/64 GT/s的信號傳輸速率,並利用了由SNIA維護的成熟行業標准連接器外形尺寸。PCI-SIG原來打算在2023年內發布,已經晚了小半年了。

PCI-SIG總裁兼主席Al Yanes表示,CopprLink線纜規范將PCIe布線與PCIe電氣基礎規范無縫集成,提供了更長的通道覆蓋范圍和拓撲靈活性。CopprLink線纜旨在與相同的連接器外形尺寸一起發展,適應未來PCIe技術的發展,並滿足新興應用的需求。

CopprLink內部線纜規范:

支持PCIe 5.0/6.0標準的信號,速率分別為32/64 GT/s

包括SNIA SFF-TA-1016連接器外形尺寸

單個系統內的最大傳輸距離為1米

實施示例包括獨立伺服器平台節點中的主板到擴展卡、主板到背板、晶片到晶片以及擴展卡到背板

目標應用包括存儲和數據中心計算節點

CopprLink外部線纜規范:

支持PCIe 5.0/6.0標準的信號,速率分別為32/64 GT/s

包括SNIA SFF-TA-1032連接器外形尺寸

在機架到機架的連接中最長可達2米

實施示例包括分解伺服器平台節點中的CPU到存儲、CPU到內存、CPU到加速器、以及CPU到伺服器平台節點中的加速器結構

目標應用包括存儲和數據中心AI/ML用例

CopprLink內部和外部線纜規范資料已經提供給PCI-SIG成員下載,同時針對128 GT/s的PCIe 7.0 標準的CopprLink線纜相關工作已經在進行當中,這表明了PCI-SIG對CopprLink線纜規范的承諾。 ...

PCI-SIG公布PCIe 7.0規范的0.5版本:向成員提供完整草案

在2022年PCI-SIG開發者大會上,PCI-SIG慶祝其成立三十周年,並宣布了下一代的PCIe 7.0規范,計劃在2025年向其成員發布。近日PCI-SIG宣布,推出PCIe 7.0規范的0.5版本,可供成員審查。這是PCIe 7.0規范的正式初稿,納入了2023年6月發布0.3版本後從成員那裡收到的所有反饋。

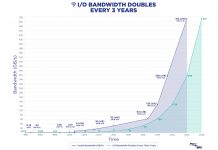

相比於PCIe 6.0規范,PCIe 7.0規范的數據傳輸速率將再次倍增,達到128 GT/s,大幅度高於PCIe 6.0的64 GT/s和PCIe 5.0的32 GT/s。一個PCIe 7.0 x16通道可以支持512 GB/s,使用了四級脈沖幅度調制(PAM4)信令和1b/1b flit模式編碼和前向糾錯(FEC),這些都延用了之前PCIe 6.0規范的功能。

此外,PCIe 7.0規范還重點關注了注重通道參數和覆蓋范圍、繼續實現低延遲和高可靠性目標、提高電源效率、並保持與所有前幾代PCIe技術的向後兼容性。PCI-SIG希望,PCIe 7.0規范可以成為800G乙太網、人工智慧/機器學習、超大規模數據中心、HPC、量子計算和雲等數據密集型市場的可擴展互連解決方案。

就像PCI-SIG設計的其他規范一樣,每個PCI Express規范都會有五個主要的節點。

0.3版本:概念。該草案描述了需要實現的目標和實現這些目標的方法。

0.5版本:第一稿。這個版本必須完全解決0.3草案中設定的目標,它還包括所有的架構方面和要求。此外,它還包含了來自各相關方的反饋意見,此時PCI-SIG的成員可以將功能添加到正在制定的規范中。

0.7版本:完整草案。這個版本必須有一套完整的功能需求和方法定義,因為在這個版本之後不能再增加新的功能了。此外,電氣規范必須已經使用測試晶片進行了驗證。在這一點上,PCI-SIG成員可以提出新接口的不同實現。

0.9版本:最終草案。此時,PCI-SIG成員正在對技術進行內部審查,以確保其智慧財產權和專利。同時,不允許進行任何功能上的修改。

1.0版本:最終版本。從這個版本開始,所有的更改和增強都必須通過正式的勘誤表文檔和工程變更通知(ECN)。

據了解,PCIe 7.0規范需要更短的PCIe走線,這使得根設備和端點設備之間的距離進一步縮短。目前要實現PCIe 5.0的設計,需要更厚的PCB和更高質量的用料,也就是說成本提高了,暫時還不清楚PCIe 7.0對於這方面的考慮。

...

PCI-SIG確認PCIe 5.0/6.0將使用新線纜設計,名為「CopprLink」

近日PCI-SIG在美國丹佛科羅拉多會議中心舉行了SC23會議,向成員展示了PCIe技術演示和新的PCI快速線纜命名方案,強調了PCIe技術是高性能計算互連的首選。PCI-SIG表示,PCIe內部和外部線纜新命名方案為「CopprLink」,目前正在制定PCIe 5.0和PCIe 6.0的內部和外部線纜規范,目標是今年內發布。

PCI-SIG的演示重點是高性能計算(HPC),因此CopprLink可能會將目標放在了接口的數據傳輸上,以便為下一代平台上的各種設備提供最佳的傳輸帶寬,供電問題或許不是考慮的重點。如果CopprLink與供電密切相關,那麼應該會努力解決當前12VHPWR標准遇到的一些問題。雖然「12V-2×6 PCIe 6.0」連接器新設計已經發布了,不過似乎還有改進的餘地。

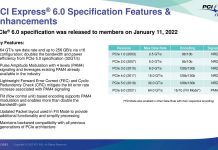

PCI-SIG早在去年1月就發布了PCIe 6.0規范,主要面向數據密集型市場,比如高性能計算、數據中心、邊緣計算、人工智慧和機器學習(AI/ML)、汽車、物聯網(IoT)以及航空航天等,並進一步加強了PCI Express作為高速互聯的接口。PCIe 6.0規范將數據傳輸速率提高到64 GT/s,相比PCIe 5.0規范提高了一倍,16通道可以提供高達256 GB/s的最大雙向帶寬。

此外,PCIe 6.0規范利用基於固定大小流控制單元(Flit)的編碼,允許使用低延遲前向糾錯(FEC)和四級脈沖幅度調制(PAM4)信令和強循環冗餘校驗(CRC)。當然,PCIe 6.0規范保持了與以往PCIe技術的兼容性,支持與數以萬計現有產品的連接。 ...

PCI-SIG探索新的連接方式:以光互連實現更高的PCIe技術性能

PCI-SIG今天宣布,將成立一個新的工作組,負責開發通過光連接的方式提供PCI Express(PCIe)技術。PCI-SIG的光連接工作組尋求廣泛的光學技術支持,同時可能會開發特定技術的外形尺寸。

研究人員表示,光互連將是PCIe架構的一大進步,因為可以實現更高的性能、更低的功耗、更長的覆蓋范圍和更短的延遲。許多有數據需求的市場和應用程式,比如雲端服務、量子計算、超大規模數據中心和高性能計算等,都將受益於光互連的PCIe技術架構。

PCI-SIG總裁兼主席Al Yanes表示,已看到業界對通過實現應用之間的光互連來擴大成熟、多次疊代和高能效的PCIe技術標準的應用范圍有著濃厚的興趣。PCI-SIG歡迎業界提供意見,並邀請所有PCI-SIG成員加入新的工作組,分享各自的專業知識,幫助制定工作組的具體目標和要求。

目前PCI-SIG正在推進PCIe 7.0規范的制定工作,大概兩個月前發布了PCIe 7.0規范的0.3版本。PCIe 7.0規范的數據傳輸速率將再次倍增,達到128 GT/s,大幅度高於PCIe 6.0的64 GT/s和PCIe 5.0的32 GT/s。一個PCIe 7.0 x16通道可以支持512 GB/s,並沿用了之前PCIe 6.0規范的四級脈沖幅度調制(PAM4)信令和1b/1b flit模式編碼和前向糾錯(FEC)等功能。 ...

PCI-SIG公布PCIe 7.0規范的0.3版本:目標2027年x16插槽提供512GB/s的速度

在2022年PCI-SIG開發者大會上,PCI-SIG慶祝其成立三十周年,並宣布了下一代的PCIe 7.0規范,計劃在2025年向其成員發布。近日PCI-SIG宣布,發布PCIe 7.0規范的0.3版本。這標志著PCIe 7.0規范的新成就,表明PCI-SIG組織成員已經就即將推出的技術的關鍵特徵和架構達成了一致。

據TomsHardware報導,PCIe 7.0規范的數據傳輸速率將再次倍增,達到128 GT/s,大幅度高於PCIe 6.0的64 GT/s和PCIe 5.0的32 GT/s。一個PCIe 7.0 x16通道可以支持512 GB/s,使用了四級脈沖幅度調制(PAM4)信令和1b/1b flit模式編碼和前向糾錯(FEC),這些都延用了之前PCIe 6.0規范的功能。

就像PCI-SIG設計的其他規范一樣,每個PCI Express規范都會有五個主要的節點。

0.3版本:概念。該草案描述了需要實現的目標和實現這些目標的方法。

0.5版本:第一稿。這個版本必須完全解決0.3草案中設定的目標,它還包括所有的架構方面和要求。此外,它還包含了來自各相關方的反饋意見,此時PCI-SIG的成員可以將功能添加到正在制定的規范中。

0.7版本:完整草案。這個版本必須有一套完整的功能需求和方法定義,因為在這個版本之後不能再增加新的功能了。此外,電氣規范必須已經使用測試晶片進行了驗證。在這一點上,PCI-SIG成員可以提出新接口的不同實現。

0.9版本:最終草案。此時,PCI-SIG成員正在對技術進行內部審查,以確保其智慧財產權和專利。同時,不允許進行任何功能上的修改。

1.0版本:最終版本。從這個版本開始,所有的更改和增強都必須通過正式的勘誤表文檔和工程變更通知(ECN)。

據了解,PCIe 7.0規范需要更短的PCIe走線,這使得根設備和端點設備之間的距離進一步縮短。目前要實現PCIe 5.0的設計,需要更厚的PCB和更高質量的用料,也就是說成本提高了,暫時還不清楚PCIe 7.0對於這方面的考慮。

...

Rambus推出PCIe 6.0接口子系統,面向下一代高性能數據中心和AI SoC解決方案

Rambus宣布,推出PCI Express(PCIe 6.0)接口子系統,由PHY和控制器IP組成,同時還支持最新的Compute EXpress Link(CXL)3.0規范,旨在為下一代高性能數據中心和AI SoC解決方案提供支持。

Rambus接口IP總經理Scott Houghton表示,AI、ML和數據密集型工作負載的快速發展正在推動數據中心架構的持續發展,需要更高的性能,而新一代PCIe 6.0接口子系統可以滿足下一代數據中心的性能要求,具有一流的延遲、功耗、面積和安全性。

Rambus的PCIe 6.0接口子系統可提供64 GT/s的數據傳輸速率,經過全面優化後,可以滿足高級異構計算架構的需求。在該子系統中,PCIe控制器通過具有完整性和數據加密(IDE)引擎提供最先進的安全性,監控和保護PCIe鏈路免受物理攻擊。

由於Rambus PCIe 6.0接口子系統完全支持CXL 3.0,可實現緩存相干記憶體共享、擴展和池化的晶片級解決方案。隨著CXL變得越來越重要,加上PCIe在數據中心已無處不在,更多的客戶會追求不斷升級帶寬和速度,以支持下一代應用,而訪問高性能接口IP解決方案將是實現生態系統的關鍵。

Rambus PCIe 6.0接口子系統的主要特性包括:

支持PCIe 6.0規范,包括64 GT/s數據傳輸速率和PAM4信令

支持實現高帶寬效率的固定大小的FLIT

實現低延遲前向糾錯 (FEC) 以提高鏈路穩健性

通過IDE引擎實現一流的安全性

向後兼容PCIe 5.0、4.0和3.0/3.1

支持CXL 3.0用於優化記憶體資源

...

Rambus發布PCIe 6.0控制器:為下一代數據中心提供64 GT/s的傳輸速率

PCI-SIG在2022年1月正式向其成員發布了PCIe 6.0規范,PCIe新規范讓帶寬再次翻倍。PCI-SIG表示,PCIe 6.0規范的發布將有利於數據密集型市場,比如高性能計算(HPC)、數據中心、邊緣計算、人工智慧和機器學習(AI/ML)、汽車、物聯網(IoT)以及航空航天等,並進一步加強了PCI Express作為高速互聯的接口。

Rambus宣布推出全球首款PCIe 6.0控制器,這是完全符合本月初發布的PCIe 6.0規范。Rambus表示,這款新的PCIe 6.0控制器針對功耗、面積和延遲等方面進行了優化,為高性能應用提供64 GT/s的數據傳輸速率。此外,該控制器通過完整性和數據加密(IDE)引擎提供最先進的安全性,監控和保護PCIe鏈路免受物理攻擊。

Rambus營運長Sean Fan表示,人工智慧/機器學習和數據密集型工作負載的快速發展需要我們繼續提供具有一流延遲、功耗和面積的更高數據速率的解決方案,這款PCIe 6.0控制器作為其產品線的新成員,可以為客戶提供了一種易於集成的解決方案,為高級SoC和FPGA提供性能和安全性。

Rambus PCIe 6.0控制器的主要特性包括:

支持PCIe 6.0規范,包括64 GT/s數據傳輸速率和PAM4信令

支持實現高帶寬效率的固定大小的FLIT

實現低延遲前向糾錯 (FEC) 以提高鏈路穩健性

內部數據路徑大小可根據最大值自動放大或縮小(256、512、1024 位)連結速度和寬度,以減少門數和優化吞吐量

向後兼容PCIe 5.0、4.0和3.0/3.1

支持端點、根埠,以及雙模式和交換機埠配置

針對性能進行了優化的集成IDE

...

PCI-SIG正式發布PCIe 6.0規范,將有利於數據密集型市場

PCI-SIG在2019年6月開始PCIe 6.0規范的相關制定工作,在經歷了兩年零七個月後,PCI-SIG在2022年1月正式向其成員發布PCIe 6.0規范。新規范是在PCIe 5.0規范發布不到三年後推出的,同時也兌現了PCI-SIG的承諾,即每發布一個PCIe新規范就會讓帶寬翻倍。

PCIe 6.0規范的發布,將有利於數據密集型市場,比如高性能計算(HPC)、數據中心、邊緣計算、人工智慧和機器學習(AI/ML)、汽車、物聯網(IoT)以及航空航天等,並進一步加強了PCI Express作為高速互聯的接口。

PCIe 6.0規范的主要優勢在於:

帶寬加倍:將數據傳輸速率提高到64 GT/s,相比PCIe 5.0規范提高了一倍,16通道可以提供高達256 GB/s的最大雙向帶寬。

低延遲: 利用基於固定大小流控制單元(Flit)的編碼,允許使用低延遲前向糾錯(FEC)和四級脈沖幅度調制(PAM4)信令和強循環冗餘校驗(CRC)。

向後兼容性: 保持與以往PCIe技術的兼容性,支持與數以萬計現有產品的連接。

就像PCI-SIG設計的其他規范一樣,每個PCI Express規范都會有五個主要的節點。

0.3版本:概念。該草案描述了需要實現的目標和實現這些目標的方法。就PCIe 6.0而言,是指提出了64 GT/s數據傳輸速率、PAM4信令和FEC。

0.5版本:第一稿。這個版本必須完全解決0.3草案中設定的目標,它還包括所有的架構方面和要求。此外,它還包含了來自各相關方的反饋意見,此時PCI-SIG的成員可以將功能添加到正在制定的規范中。PCI-SIG在2020年2月底發布了PCIe 6.0規范的0.5版本。

0.7版本:完整草案。這個版本必須有一套完整的功能需求和方法定義,因為在這個版本之後不能再增加新的功能了。此外,電氣規范必須已經使用測試晶片進行了驗證。在這一點上,PCI-SIG成員可以提出新接口的不同實現。

0.9版本:最終草案。此時,PCI-SIG成員正在對技術進行內部審查,以確保其智慧財產權和專利。同時,不允許進行任何功能上的修改。

1.0版本:最終版本。從這個版本開始,所有的更改和增強都必須通過正式的勘誤表文檔和工程變更通知(ECN)。

相關支持PCIe 6.0規范的產品,很可能要到2023年底或2024年的某個時候才會上市。這個可以參考此前的PCIe 5.0規范,PCI-SIG是在2019年5月底公布了PCIe 5.0規范的最終版本,實際上首批支持該技術的產品直到2021年底才出現。 ...

Cadence發布PCIe 6.0 IP測試晶片設計套件,採用台積電5nm工藝製造

大概在一個月前,PCI-SIG宣布PCIe 6.0已經到了0.9版本,相當於最終草案階段。目前PCI-SIG成員正在對技術進行內部審查,以確保其智慧財產權和專利。除非出現重大問題,否則不允許進行任何功能上的修改,相關企業也可以開始在產品中採用PCIe 6.0。

近日,Cadence(楷登電子)宣布推出PCIe 6.0 IP測試晶片設計套件,讓晶片開發人員能夠在其設計中實現對PCIe 6.0的支持並進行測試,其支持Cadence的智能系統設計戰略(Intelligent System Design),實現了SoC的卓越設計。據Cadence介紹,早期的開發人員已開始探索新一代的PCIe 6.0規范,利用Cadence和台積電(TSMC)的技術,或許會在2022年-2023年加入到晶片設計中。

這款面向PCIe 6.0 IP測試晶片設計套件包括基於DSP的高性能PHY和功能豐富的配套控制器,為為超大規模計算和5G通信的新一代應用提供優化的性能和吞吐量。在今年7月份,Cadence的PCIe 6.0子系統測試晶片在台積電N5製程節點上完成流片,其集成了第二代功耗、性能和面積(PPA)優化的PCIe 6.0 PHY與PCIe 6.0控制器。

在PCIe 6.0規范中,數據傳輸速率從PCIe 5.0的32 GT/s和PCIe 4.0的16 GT/s提高到每引腳64 GT/s,PCIe 6.0 ×16通道單向理論數據傳輸速度達到了128 GB/s(雙向256...

PCIe 6.0規范進入最終草案階段:×16通道單向速度達128 GB/s

PCI-SIG在2019年6月開始PCIe 6.0相關工作,在經歷了兩年零四個月後,目前PCIe 6.0已經到了0.9版本,相當於最終草案階段。PCI-SIG成員正在對技術進行內部審查,以確保其智慧財產權和專利。除非出現重大問題,否則不允許進行任何功能上的修改。這意味著相關的公司可以開始在產品中採用PCIe 6.0,以確保產品符合規范草案。

據了解,1.0版本將會在今年年底或明年初公布。

PCIe 6.0將把數據傳輸速率從PCIe 5.0的32 GT/s和PCIe 4.0的16 GT/s提高到每引腳64 GT/s,PCIe 6.0 ×16通道單向理論數據傳輸速度達到了128 GB/s(雙向256 GB/s)。為了提高數據傳輸速率和帶寬,新接口採用了四級脈沖振幅調制(PAM4)信令,這種信令也被用於像InfiniBand這種高端網絡技術以及GDDR6X記憶體等地方。此外,PCIe 6.0還採用了低延遲前向糾錯(FEC),以確保高效率運行。

就像PCI-SIG設計的其他規范一樣,每個PCI Express規范都有五個主要的節點。

0.3版本:概念。該草案描述了需要實現的目標和實現這些目標的方法。就PCIe 6.0而言,是指提出了64 GT/s數據傳輸速率、PAM4信令和FEC。

0.5版本:第一稿。這個版本必須完全解決0.3草案中設定的目標,它還包括所有的架構方面和要求。此外,它還包含了來自各相關方的反饋意見,此時PCI-SIG的成員可以將功能添加到正在制定的規范中。PCI-SIG在2020年2月底發布了PCIe 6.0規范的0.5版本。

0.7版本:完整草案。這個版本必須有一套完整的功能需求和方法定義,因為在這個版本之後不能再增加新的功能了。此外,電氣規范必須已經使用測試晶片進行了驗證。在這一點上,PCI-SIG成員可以提出新接口的不同實現。

0.9版本:最終草案。此時,PCI-SIG成員正在對技術進行內部審查,以確保其智慧財產權和專利。同時,不允許進行任何功能上的修改。

1.0版本:最終版本。從這個版本開始,所有的更改和增強都必須通過正式的勘誤表文檔和工程變更通知(ECN)。

支持PCIe 6.0規范的產品並不會那麼快上市,預計支持的平台產品將在2023年底或2024年的某個時候才上市。這個可以參考此前的PCIe 5.0規范,PCI-SIG在2019年5月底公布了PCIe 5.0規范的最終版本,實際上首批支持該技術的產品直到2021年底才出現。 ...

幫你更好的了解PCIe 4.0:3DMark上線相關功能測試

AMD Ryzen 3000系列處理器和X570主板馬上就要開售了。除了IPC和緩存、核心數等方面的提升,目前大家最關心的應該就是PCIe 4.0相關內容了。今天Underwriters Laboratories(UL)旗下的3DMark上線了PCI Express功能測試,可以用來測試PCIe接口為顯卡提供的帶寬,可以更加直觀的反映出不同PCIe版本的區別,從而為玩家選擇主板和顯卡提供參考。

根據說明,3DMark的PCI Express功能測試可以通過PCIe接口測試顯卡的可用帶寬,並表示更多的帶寬可以讓遊戲運行傳輸更多的數據,減少遊戲的加載時間,並可以在更加復雜的場景當中跑出更流暢的成績。

這項測試在幀與幀之間使用固定的時間步長,因此可以保證在測試時不同的硬體都會執行相同的工作量。測試將大量頂點和紋理數據上載到顯卡,測試運行時頂點數據量會逐漸增加,由於帶寬達到飽和,系統渲染每一幀畫面花費的時間也會增加,但是使用的總帶寬量維持不變。軟體會根據測試時的平均帶寬占用提供最終的測試結果。

測試畫面

目前相關測試已經上線,購買3DMark Advanced Edition或3DMark Professional Edition的用戶都可以免費試用,兼容任何支持Direct X 12的獨立顯卡,大家更新3DMark就可以直接使用了。由於這項測試的主體是PCIe插槽,所以不能測試核顯相關內容,而且如果你的電腦有多個顯卡,它只會測試主顯卡。為了更好的了解這項功能,我也用我手頭的測試平台進行了測試,大概規格為英特爾酷睿i7-8700K、技嘉 Z370 AORUS Gaming 3、技嘉 AORUS 8GB DDR4-3200x2、技嘉 GeForce RTX 2080 Ti...