近日,Intel在其2020年架構日中更新了他們在六大技術支柱方面所取得的進展,揭秘了Willow Cove,Tiger Lake和Xe架構以及全新的晶體管技術。這為我們展現了一個不服輸,甚至還在挑戰新領域的Intel。

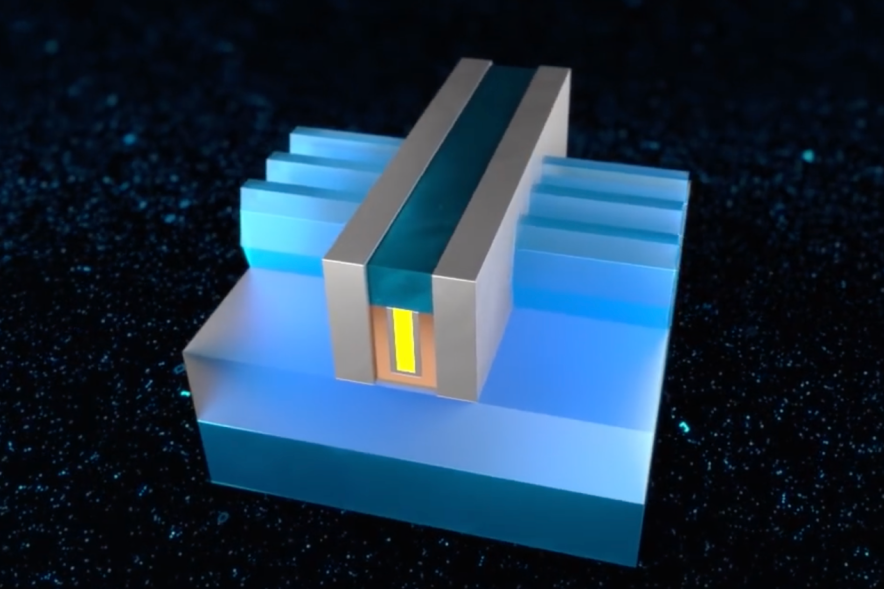

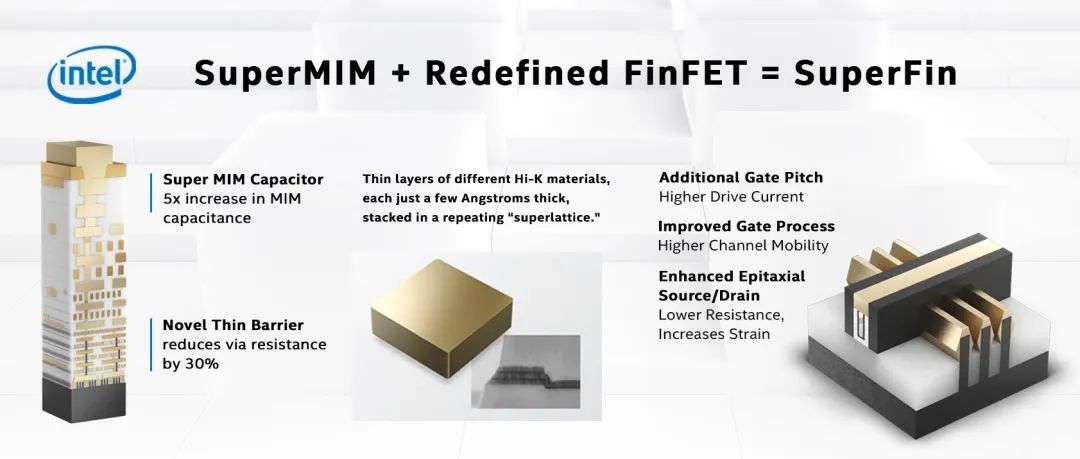

SuperFin技術重新定義晶體管

Intel本次發布的全新晶體管技術是這次架構日中的亮點之一。

一直以來,Intel在晶體管技術的發展中扮演着重要的角色。大約十年以前,晶體管結構開始從平面結構轉向FinFET。在這個轉變過程當中,Intel是第一個將FinFET實現商業化的企業——2011年,Intel將之用於22nm工藝的生產。兩年後,其他企業才跟進有關FinFET的生產。從16/14nm開始,FinFET成為了半導體器件的主流選擇。時至今日,FinFET仍舊是現代納米電子半導體器件製造的基礎,支持着7nm,甚至是未來5nm、3nm的發展。

但在先進工藝不斷向前發展的過程當中,FinFET技術也需要不斷地進行更新,才能滿足晶體管性能上的提升。因此,在Intel從14nm走向10nm的過程中,他再次重新定義了晶體管。

在本次架構日當中,Intel推出了10nm SuperFin技術。Intel稱,這是該公司有史以來最為強大的單節點內性能增強,帶來的性能提升可與全節點轉換相媲美。換言之,在SuperFin技術的加持下,Intel推出的10nm工藝效能可以等同於7nm。

從Intel公布的信息中看,10nm SuperFin技術還實現了Intel增強型FinFET晶體管與Super MIM(Metal-Insulator-Metal)電容器的結合。據其官方資料顯示,Super MIM在同等的占位面積內電容增加了5倍,從而減少了電壓下降,顯著提高了產品性能。

Intel稱,該技術由一類新型的「高K「( Hi-K)電介質材料實現,該材料可以堆疊在厚度僅為幾埃厚的超薄層中,從而形成重復的「超晶格」結構。這是一項行業內領先的技術,領先於其他芯片製造商的現有能力。

為什麼說SuperFin技術重新定義了晶體管。這就要從單節點內性能提升幅度的角度看。從Intel提供的數據來看,如今加強版14nm在性能上相比第一代已經提升了超過20%,而這種提升幅度是經過了四次修訂才達到的。但有了SuperFin技術,Intel的10nm做到這種提升卻只花了一代。因而,可以說這是相當於一代製造工藝的飛躍。

從Intel的介紹中看,SuperFin技術無疑是推動其先進製程快速向前發展的利器。在筆者看來,這也是Intel對市場質疑其先進工藝落後的回擊(前不久Intel公布了其第二季度財報,當時Intel稱其7nm芯片考慮由其他企業代工,引起了市場質疑其先進工藝的水平)。

3D封裝技術的新進展

眾所周知,先進工藝的進步需要相關企業對此進行的投入越來越大,但在大規模投資下所誕生的製程微縮所帶來的單位成本降低的效益卻明顯下降,在這種環境下,先進封裝成為了各大廠商競逐的新領域。

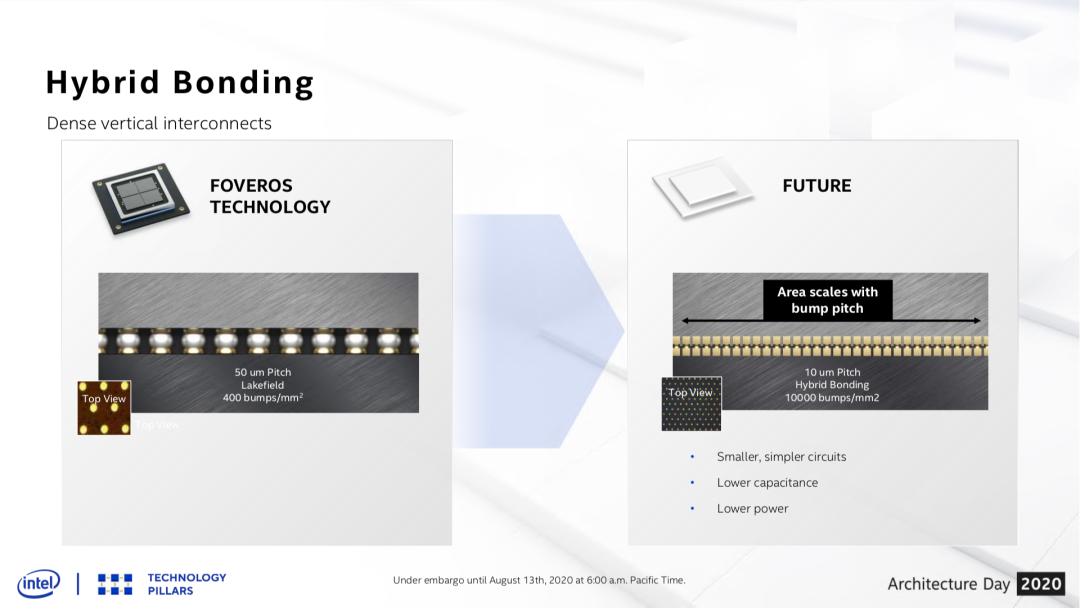

近幾年,異構架構的出現推動了先進封裝的發展。在此期間,Intel發布了2.5D封裝 EMIB、3D封裝Foveros以及被視為是兩者結合的Co-EMIB。

在本次架構日當中,Intel介紹了繼Foveros後又一新的先進封裝技術。Intel稱其為「混合結合(Hybrid bonding)「技術。Intel的官方資料顯示,當今大多數封裝技術中使用的是傳統的「熱壓結合(thermocompression bonding)」技術,混合結合是這一技術的替代品。這項新技術能夠加速實現10微米及以下的凸點間距,提供更高的互連密度、帶寬和更低的功率。

據透露,使用「混合結合(Hybrid bonding)「技術的測試芯片已在2020年第二季度流片。

這些先進封裝到底能解決什麼樣的問題?從市場情況中看,異構已經成為了未來芯片發展的一種趨勢,越來越多的硬件將會集成到一塊芯片當中,未來這種趨勢還將發展成將更多的IP集成到一塊芯片當中。Intel將這種設計定義為「分解設計」。

如下圖所示,利用這種分解設計可以大幅縮短整個開發時間。眾所周知,採用新的工藝就意味着相關器件要重新進行驗證,但隨着終端領域所需要的功能越來越大,越來越多的器件都將加入其中,這就導致開發或者是驗證的時間越來越長。

而採用這種分解設計則可以化繁為簡,先把它做成幾個大的部分,比如可以分為CPU、GPU、IO等(這些硬件可以採用不同的工藝),再分別進行更新或驗證。舉例來說,CPU可能是一個已經驗證過的,在這種分解設計下,CPU就不再需要重新驗證。而GPU則是要用更新的,但由於它與CPU是分離的,所以僅需要對GPU進行重新驗證。這也就是說,不會因為CPU和GPU互相糾纏在一起,而出現新的Bug出現,這也就大大縮短了產品驗證的時間。

要達到這種設計效果,其中的互聯就變得尤為重要,而這就是先進封裝所能解決的問題。EMIB、Foveros或是Co-EMIB能夠保障這些硬件能夠分解,又能保證它們在低功耗下擁有足夠的數據傳輸帶寬。也正是利用這些技術,Intel才能夠將來自其他供應商的IP和處理節點混合並匹配到異構封裝中,從而加快產品上市時間。

用產品驗證技術的價值

紙上得來終覺淺,產品才是驗證技術的真正價值所在。

而Intel的技術價值將在Tiger Lake中得以體現。據透露,Tiger Lake將由Intel全新的Willow Cove架構提供動力,該架構也是基於新的「 SuperFin」晶體管打造而成。

Intel指出,Tiger Lake將在關鍵計算矢量方面提供智能性能和突破性進展。同時他也是Intel第一個採用全新 Xe-LP微架構的SoC架構,可以對CPU、AI加速器進行優化,使CPU性能得到超越一代的提升,並實現大規模的AI性能提升、圖形性能巨大飛躍,以及整個SoC 中一整套頂級IP,如全新集成的Thunderbolt 4。

Tiger Lake中所採用的Xe-LP是Intel面向PC和移動計算平台的最高效架構,擁有多達96個EU,並採用了包括異步計算在內的新架構設計,以提供更大的動態范圍和頻率提升。根據Intel提供的官方數據顯示,與Gen11相比,Xe-LP能夠在更低的功耗下,提供更高的性能。

當然,Xe-LP只是Intel發展路線圖中的一部分。除此之外,Intel還提供了Xe-HP的更新版本,據介紹, Xe-HP是業界首個多區塊(multi-tiled)、高度可擴展的高性能架構,可提供數據中心級、機架級媒體性能,GPU可擴展性和AI優化。它涵蓋了從一個區塊(tile)到兩個和四個區塊的動態范圍的計算,其功能類似於多核GPU。據悉,該款GPU有望在2021年發布。

同時,Intel還發布了另一款GPU架構:Xe-HPG。據介紹,它是專門針對遊戲而設計。據Intel官方消息顯示,Xe-HPG添加了基於GDDR6的新記憶體子系統以提高性價比,且將具有加速的光線跟蹤支持。因此,也有外媒猜測,這可能代表着Intel將首次圍繞着遊戲所需的GPU,與AMD和Nvidia展開競爭。據透露,Xe-HPG預計將於2021年開始發貨。

除了Tiger Lake之外,Intel還在本次發布會中提到了另外一款產品——Alder Lake。據介紹,該產品是Intel的下一代採用混合架構的客戶端產品。Alder Lake將結合Intel即將推出的兩種架構——Golden Cove和Gracemont,並將進行優化,以提供出色的效能功耗比。

據此前消息顯示,集眾多新技術於一身的Tiger Lake將於今年當中面市,而這也會是驗證Intel技術的時刻。

結語

其實除了在備受矚目的架構、先進製程與封裝、互聯等領域外,Intel還在安全、軟件、存儲方面都有了一些新的進展。例如,在軟件方面,InteloneAPI的正式版本將於今年當中面市。

自從2018年,Intel提出這六大支柱後,我們就可以看出,Intel早已不是那個依賴於某一單獨領域去領導半導體產業發展的企業了,將多個不同領域的技術組合起來而形成產品的領導力正在Intel身上凸顯出來。