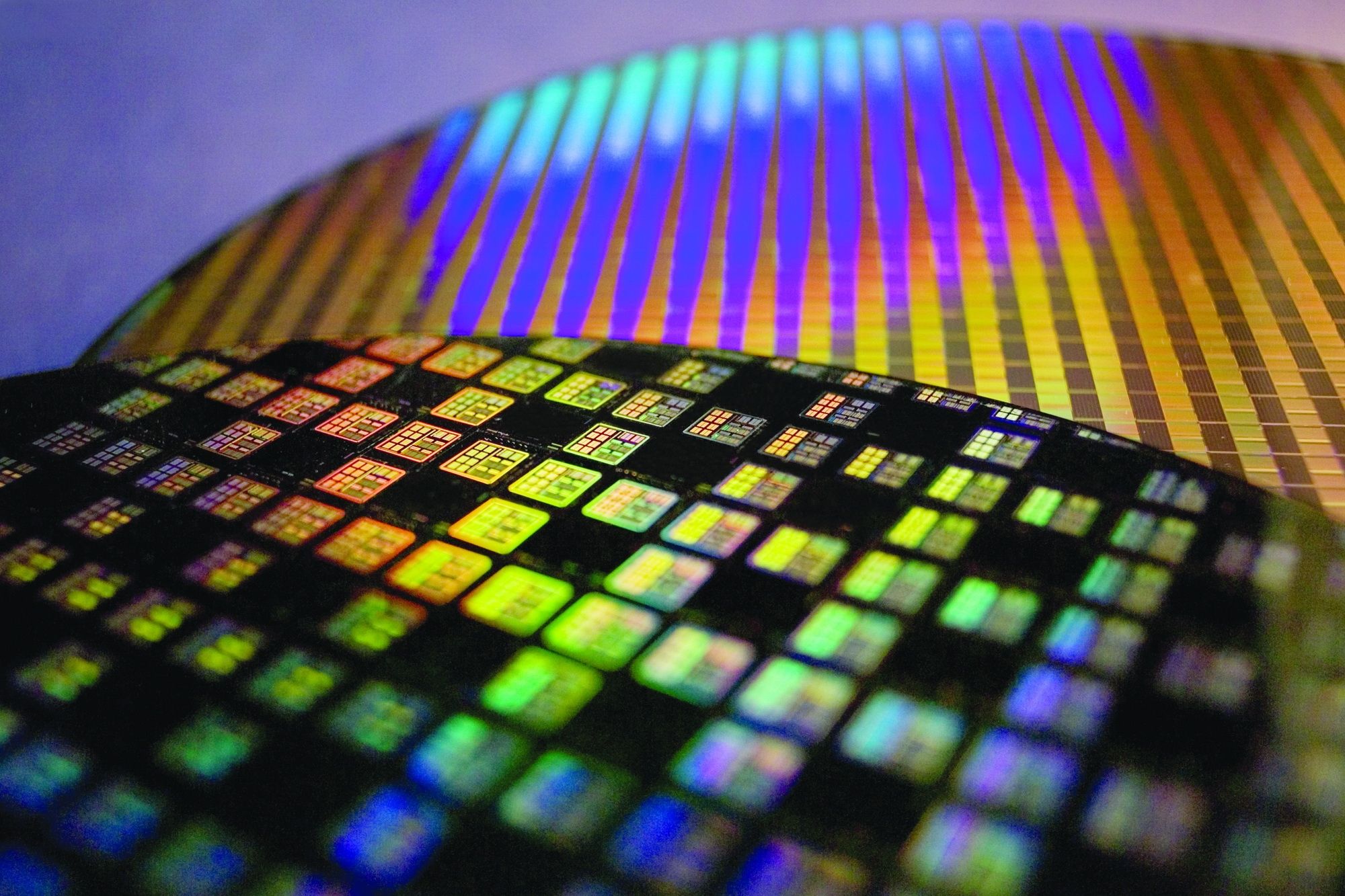

快科技8月9日消息,天眼查顯示,近日華為技術有限公司新增多條專利信息,其中一條發明專利名稱為“晶片堆疊結構及其形成方法、晶片封裝結構、電子設備”,公開號為CN116504752A。

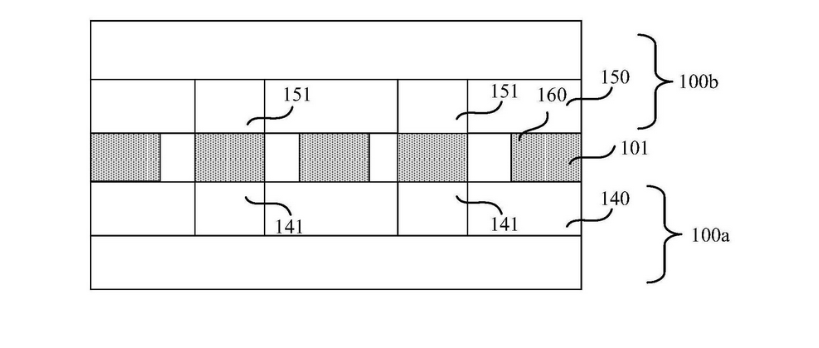

該專利涉及的技術領域為晶片技術領域,尤其涉及一種晶片堆疊結構及其形成方法、晶片封裝結構、電子設備,該技術將被用於簡化晶片堆疊結構制備工藝。

該專利也是再次引起了一些用戶的討論,什麼華為可以將兩塊14nm製程晶片堆疊在一起,實現與7nm製程晶片相似的性能和功耗,而類似的說法華為官方已經多次證實是假消息。

需要注意的是,通過晶片疊加工藝讓兩塊14nm晶片達到7nm水平說法本身就是錯誤。晶片堆疊技術方案難題包含了,熱管理、電氣互聯、封裝和測試、製造技術等等,想要完成這些並非易事。

此外,兩款14nm晶片疊加一起,還要功耗跟7nm相當,暫且說可以組合,這樣實現後也是通過降頻。要知道,14nm晶片達到7nm的性能水平就必須功耗翻倍,同時還得進一步擴大晶片面積才能塞下更多的電晶體,這顯然脫離了晶片發展規律。

再來說功耗,7nm晶片功耗基本在7W左右,14nm晶片想要保持跟前者的性能,然後功耗就至少要翻一倍,如果兩款疊加,那……

來源:快科技