AMD的下一代Zen 5架構銳龍移動處理器代號為Strix Point以及一個巨大的APU——Strix Halo,他們可能會在今年年內推出,也有可能在明年的CES上推出,現在推上有一份關於他們的官方文件泄露了少關於它們的信息。

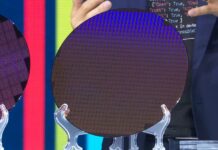

這份文件是一個名為Izzukias的用戶發布的,目前已經被刪除,但HKEPC記錄了下來,它上面明確顯示了Strix Point與Strix Halo的具體信息。當中Strix Point會繼續採用單晶片設計,CPU核心數量從8核增加到12核,包含4個Zen 5內核與8個Zen 5c內核,L3緩存共24MB,當中Zen 5內核有16MB,Zen 5c內核8MB。GPU部分將從12組RDNA 3.1 CU升級未16組RDNA 3.5 CU,NPU算力從現在的16 TOPS暴增至50 TOPS,TDP為45~65W,記憶體支持和現在是一樣的,支持DDR5-5600和LPDDR5-7500。

而巨大化的Strix Halo測採用多晶片設計,將包含兩個Zen 5架構的CCD,共16核,每個CCD各擁有32MB L3緩存,在SoC Die上有一個巨大的核顯,配備40個RDNA 3.5的CU單元,目前的RX 7600 XT也只有32組CU而已,根據此前透露的消息,該GPU的性能可媲美RTX 4060 Laptop。

有趣的是AMD在SoC Die上增加了32MB MALL Cache,它的作用類似現在的Infinity Cache,能降低GPU對記憶體帶寬的依賴,雖然Strix Halo的記憶體控制器是256bit的,也就是四通道,支持LPDDR5x-8000,但對於現在的GPU來說帶寬還是太低了,MALL Cache的加入可以有效緩解記憶體帶寬不足的問題。

Strix Halo的NPU算力能到60 TOPS,標准TDP的70W,廠商可以根據設備的散熱設計進行改動,最高可以把CPU TPD調到130W以上。

來源:超能網