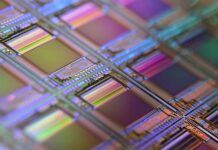

上個月,SK海力士宣布與台積電(TSMC)簽署了諒解備忘錄(MOU),雙方就下一代HBM產品生產和加強整合HBM與邏輯層的先進封裝技術密切合作。SK海力士計劃與台積電合作開發第六代HBM產品,也就是HBM4。據了解,台積電將生產用於HBM4的基礎裸片(Base Die),這是雙方針對搭載於HBM封裝內最底層的基礎裸片優化工作的一部分。

據AnandTech報導,台積電在近日舉辦的2024歐洲技術研討會上表示,將採用N5和N12FFC+工藝製造基礎裸片,為HBM4提供前所未有的性能和能源效率。台積電稱,正在與主要的HBM記憶體合作夥伴聯手,在先進位程上實現HBM4的全堆棧集成,其中N12FFC+工藝可以在滿足性能要求下具備成本優勢,N5工藝則可以在更低功耗下達到HBM4預期的速度。

N5是目前最先進的製程工藝之一,用於製造最好的CPU和GPU,現在用到存儲器上屬於一件大事,比起之前傳言中採用的N7工藝更為先進。利用N5工藝,可以將更多的邏輯和功能封裝到HBM4的基礎裸片里,並實現非常精細的互連間距,這對於邏輯晶片上的直接鍵合至關重要,從而提高人工智慧(AI)和高性能(HPC)所需的記憶體性能。N12FFC+工藝源自台積電非常成熟的16nm FinFET技術,製造的HBM4基礎裸片可用於構建12層及16層堆棧,分別提供48GB和64GB的容量,比起N5工藝更具性價比。

此外,台積電還在優化CoWoS-L和CoWoS-R封裝技術,以支持HBM4集成。按照SK海力士和台積電的計劃,HBM4預計在2026年投產。

來源:超能網