在2021年英特爾架構日上,英特爾公開了包括Alder Lake、Sapphire Rapids、Ponte Vecchio和Alchemist等信息。據Wccftech報導,在隨後的HotChips 33上,英特爾分享了更多有關Sapphire Rapids-SP處理器的信息,還介紹了一些有關Ponte Vecchio的晶片封裝問題。

英特爾表示,Sapphire Rapids使用了全新內核和加速器引擎,樹立了下一代數據中心處理器的標準。其核心是一個模塊化的分區SoC架構,受益於EMIB互連封裝技術和先進網格架構,有著很好的可擴展性,同時仍保持單晶片CPU接口的優勢。Sapphire Rapids將基於Intel 7製程工藝,支持PCIe Gen5、CXL 1.1(Compute Express Link)、八通道DDR5記憶體和HBM技術。

Sapphire Rapids支持英特爾加速器接口架構指令集(AIA),以及英特爾高級矩陣擴展(AMX)。前者支持對加速器和設備的有效調度、同步和信號傳遞,後者可以為深度學習算法核心的Tensor處理提供大幅加速,每個周期內進行2000次INT8運算和1000次BFP16運算。此外,還支持英特爾數據流加速器(DSA),旨在卸載最常見的數據移動任務,以提供更高的整體工作負載性能。

與此前流傳的信息一樣,Sapphire Rapids-SP將會有兩種不同的封裝型號,一種是標準配置,另外一種是HBM配置。標準配置將由四個XCC晶片構成的小晶片設計,單個XCC晶片的面積約為400平方毫米,通過EMIB互聯,EMIB間距為55u,核心間距為100u。標準的Sapphire Rapids-SP將有10個EMIB互聯,整個封裝的尺寸為4446平方毫米。如果是HBM配置的型號,將有14個EMIB互聯,因為需要將HBM2E記憶體互聯到核心,整個封裝的尺寸為5700平方毫米。AMD代號Genoa的EPYC處理器的封裝面積為5428平方毫米,高於Sapphire Rapids-SP標準配置版,略小於HBM配置版。

英特爾表示,與標準封裝設計相比,EMIB鏈路提供兩倍的帶寬和四倍的電源效率。受益的還有基於Xe HPC架構的Ponte Vecchio,這是英特爾現階段先進技術的集大成者,擁有超過1000億個電晶體,專門針對HPC和AI工作負載設計。其內部總共有47個不同的單元(Tile),包括了計算單元、Rambo緩存單元、Foveros封裝單元、基礎單元、HBM單元、Xe鏈路單元和EMIB單元等,採用了5種不同的製造工藝。

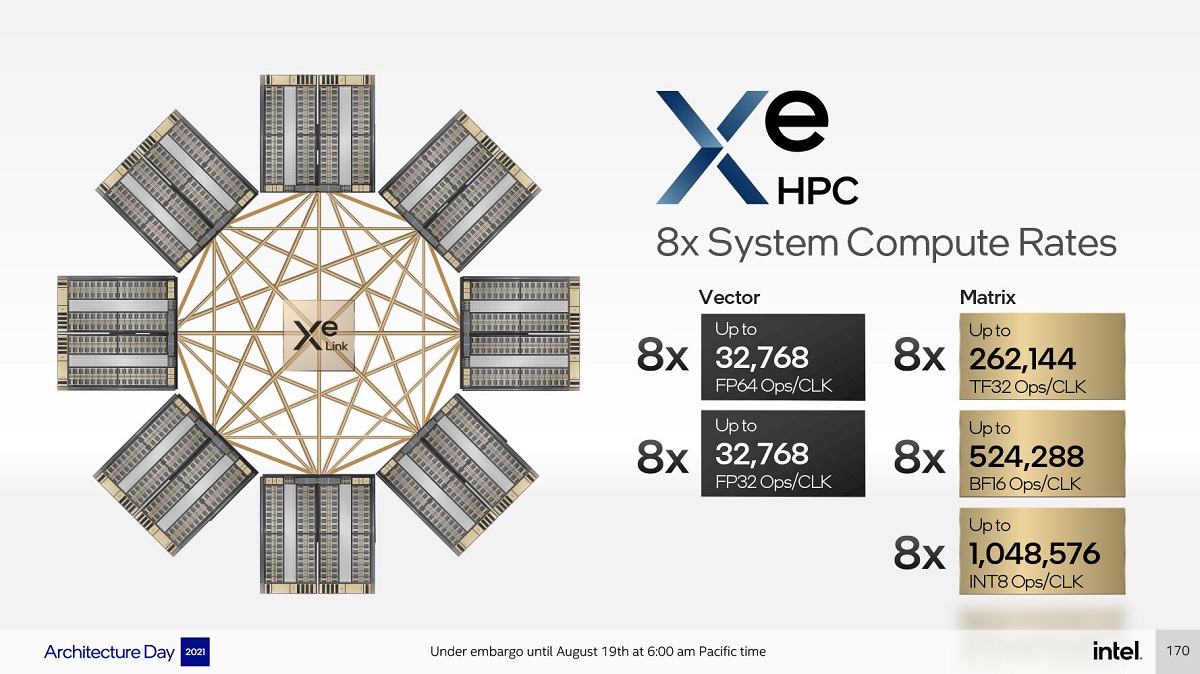

與Alchemist顯卡一樣,Ponte Vecchio的Xe HPC架構也是基於全新的Xe核心(Xe Core),不過結構上有所不同,擁有8個512位的矢量引擎和8個4096位的矩陣引擎(Xe Matrix eXtension,XMX),雖然相比Xe HPG架構數量減半,但位數分別是Xe HPG架構的一倍和四倍,同時每個Xe核心擁有512KB的L1緩存。Xe HPC架構還支持其他數據類型,比如TF32(Tensor Float 32)。由16個Xe核心可以組成一個切片(Slice),由四個切片組成一個堆棧,總計會有64個Xe核心。堆棧內還有L2緩存、4個HBM2E記憶體控制器、1個媒體引擎、8個Xe鏈路PCle控制器等。 通過多堆棧設計,加上EMIB互連封裝技術和相互間的互聯通道,可以進一步擴展,比如Ponte Vecchio則採用雙堆棧設計。

這次英特爾也介紹了Ponte Vecchio的封裝,以及對應的晶片尺寸。比如Ponte Vecchio的封裝尺寸為4843.7平方毫米,使用的3D Forveros封裝間距為36u等。Ponte Vecchio的計算單元採用台積電5nm工藝,每個單元有8個Xe核心和4MB的L1緩存;有負責I/O和高帶寬組件的基礎單元採用Intel 7工藝,面積為640平方毫米,有144MB的L2緩存;Xe鏈路單元採用台積電7nm工藝,負責GPU之間的互聯。Ponte Vecchio正處於A0版本階段,至少45 TFLOPs的FP32吞吐量。

展望未來,英特爾隨著RibbonFET和PowerVia兩大突破性技術,電晶體將進入埃米時代。英特爾還擁有幾種下一代的先進封裝設計方案,比如Forveros Omni和Forveros Direct。

來源:超能網