在Hot Chips 33上,AMD談及了其3D堆棧技術的發展方向,還分享了3D V-Cache的一些細節。AMD表示,封裝選擇和晶片架構取決於具體產品的性能、功率、面積和成本,AMD稱之為PPAC。如果將已經發布和即將推出的產品包括在內,AMD有14種多層小晶片設計的封裝架構正在進行中。

據ComputerBase報導,AMD負責封裝的高級研究員Raja Swaminathan表示,並非每個解決方案都適合所有產品,未來屬於模塊化設計和匹配協調的封裝。這已經是業界的共識,各個廠商展示的解決方案都證明了這一點。不過所有廠商都關注經濟效益,並非所有方案都適合消費市場,比如配備3D垂直緩存(3D V-Cache)技術的Zen 3架構桌面處理器,至少要有12核心的處理器才會用到。

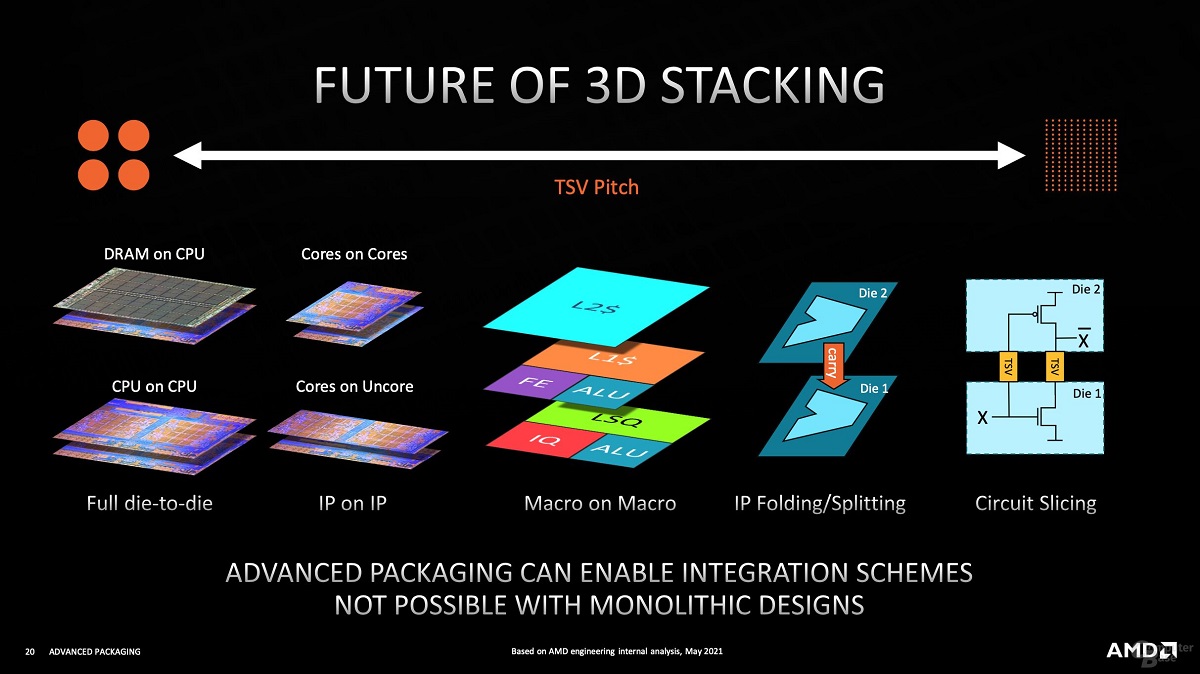

在六月份,AMD就介紹過其3D垂直緩存技術是基於台積電的SoIC技術。隨著矽通孔(TSV)的增加,未來AMD會專注於更復雜的3D堆疊技術,比如核心堆疊核心,IP堆疊IP,甚至宏塊可以3D堆疊。最終矽通孔的間距會變得非常緊密,以至於模塊拆分、折疊甚至電路拆分都將成為可能,這會徹底改變今天對處理器的認知。

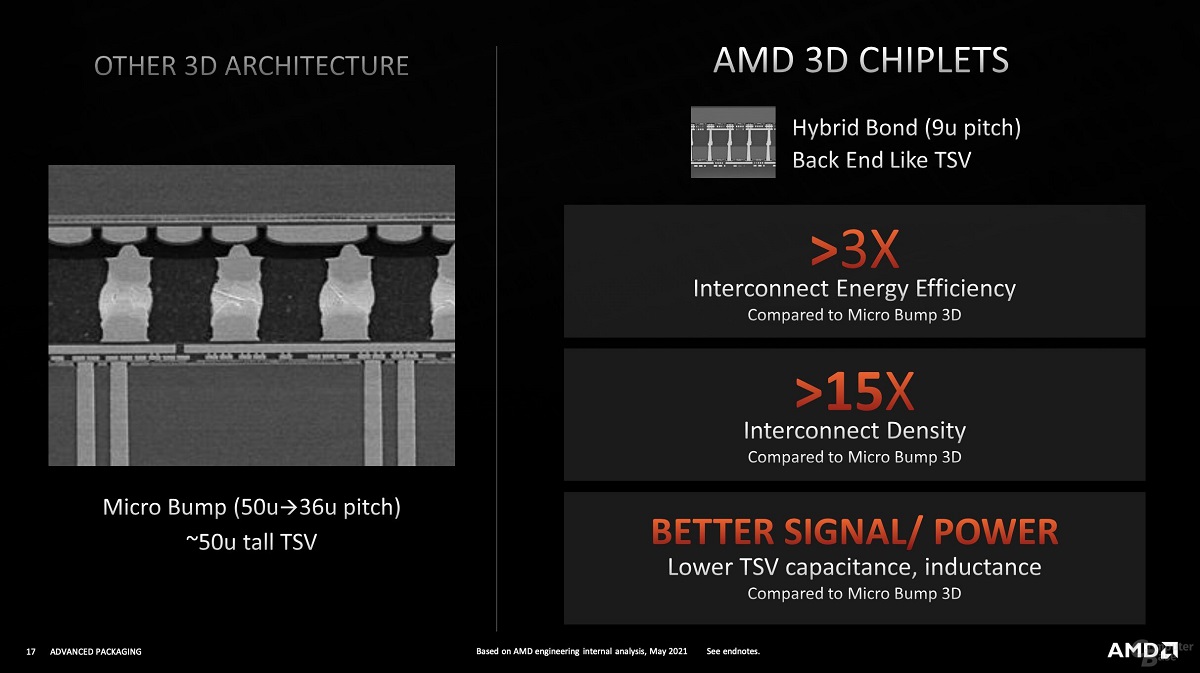

AMD分享了一些使用在Zen 3架構處理器上的3D V-Cache技術的信息,其中使用了3D微突(Micro Bump)和矽通孔互連方案,結合全新的親水介電鍵合與Direct CU-CU鍵合技術。其混合鍵合的間距僅為9u,小於英特爾Forveros互連的10u間距 。 AMD預計其3D Chiplet技術提供3倍的互連能效,以及15倍的互連密度。

來源:超能網