AMD將在明年推出Zen5架構的銳龍8000系列、霄龍9005/8005系列,更下一代的Zen6架構也已經嶄露頭角,據說可以支持到

現在,MLID曝光了一份AMD架構路線圖,列出了Zen5、Zen6的不少細節,尤其是前者料很猛。

AMD Zen架構家族採取了波動式升級策略,一代大改、一代小改交替進行,比如Zen5就會是一次大改,Zen6則是一次小改。

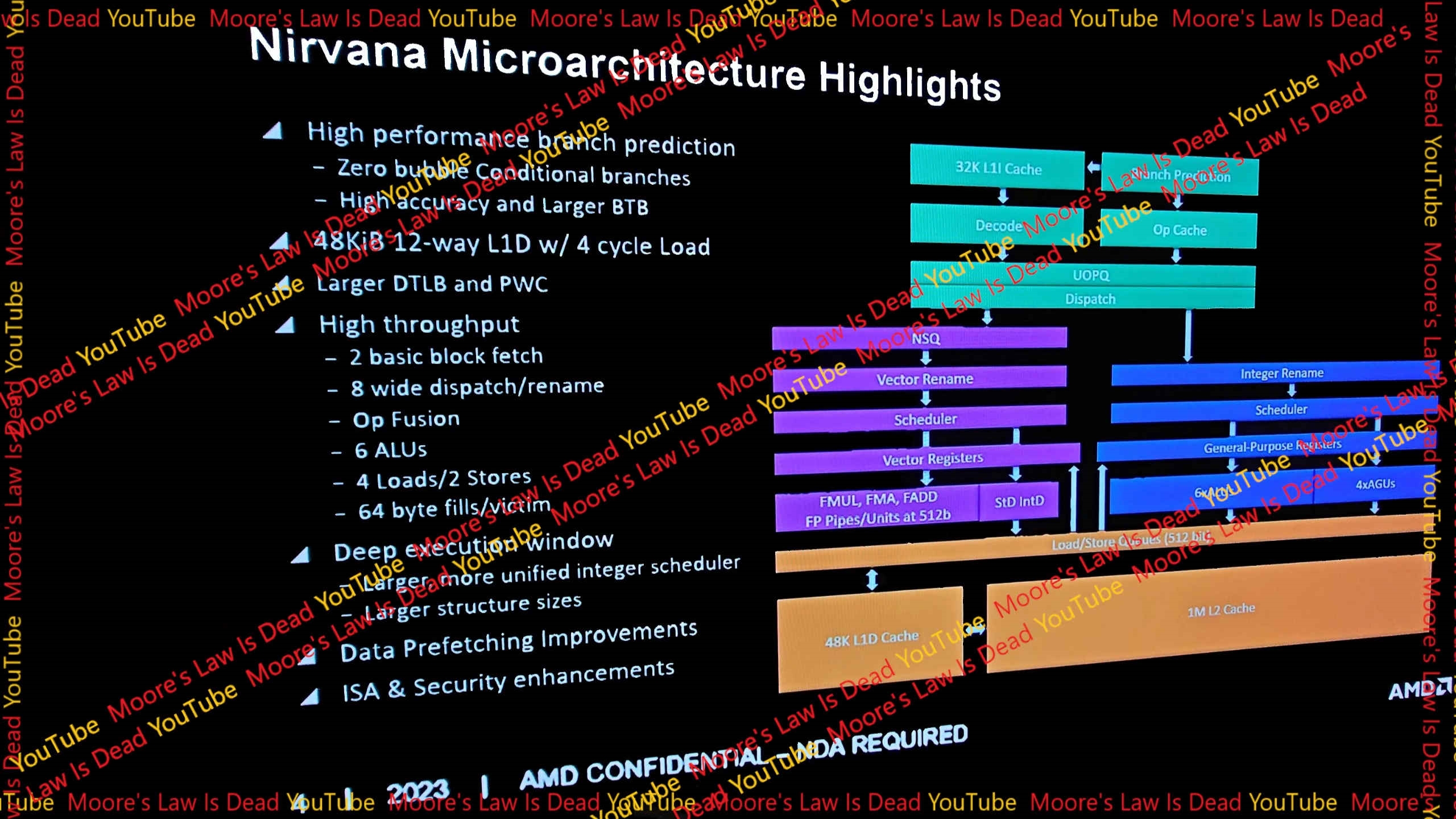

Zen5架構代號Nirvana(涅槃),預計會將IPC提升大約10-15%,對比Zen3 19%、Zen4 14%似乎不是很突出,但一則這是早期預估目標,不排除未來進一步提升,二則也要考慮頻率同步提升所帶來的性能增益。

另一點就是首次大范圍應用“大小核”混合架構,搭檔Zen5c,但應該主要面向筆記本。

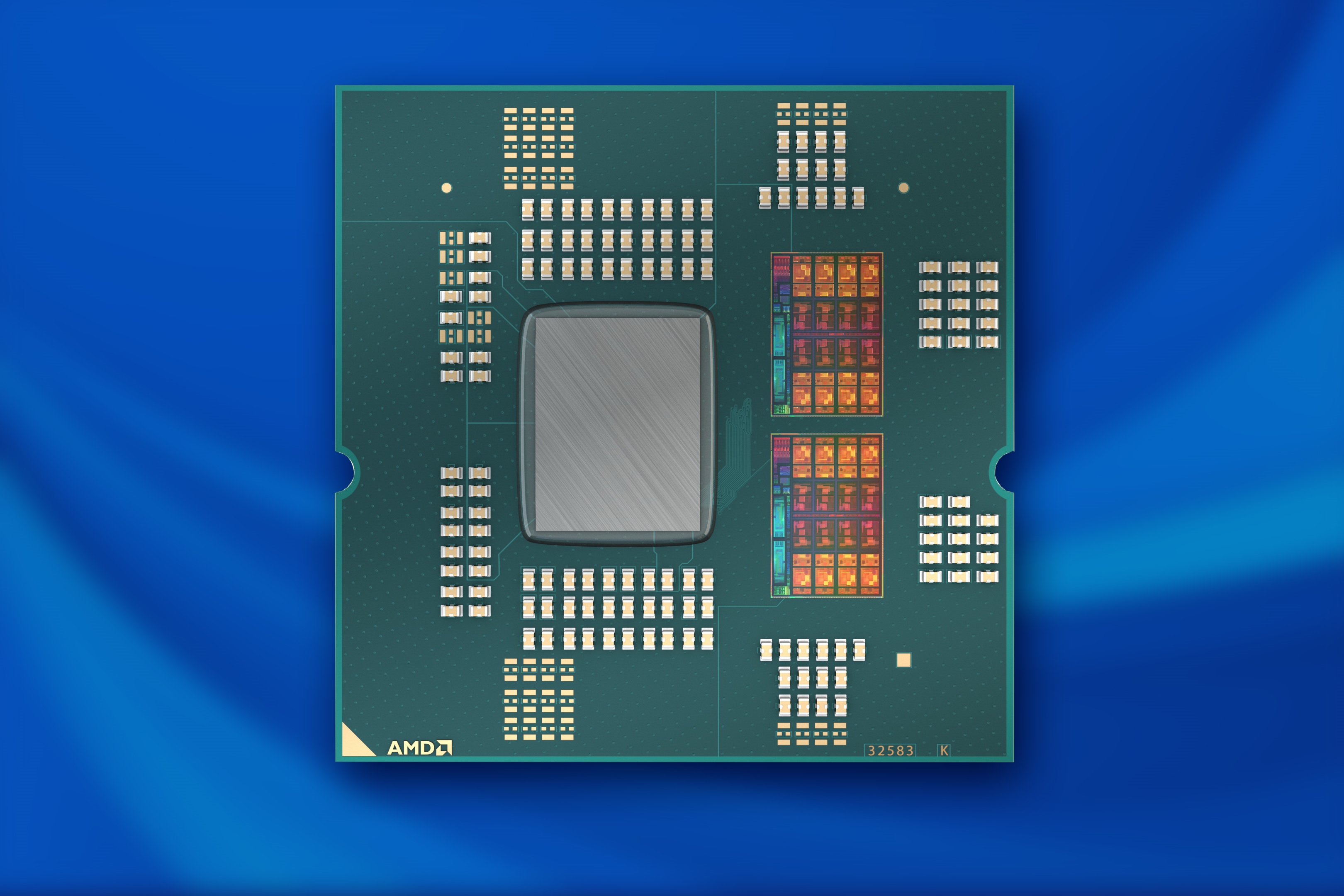

工藝方面,CCD升級為3nm,IOD升級為4nm。

尤為值得注意的是,Zen5將會首次支持原生16核心的CCD,相比這幾代的8核心翻了一番,使得桌面主流32核心成為可能。

其他方面,一級數據緩存容量從32KB增至48KB,同時8路關聯升級為12路,不過一級指令緩存仍是32KB, 二級緩存仍是每核心1MB。

分支預測繼續提升性能和精度,數據預取繼續改進,ISA指令與安全繼續增強,吞吐能力也進一步擴大,包括8寬度的分派與重命名、6個ALU算術邏輯單元、4個載入與2個存儲,等等。

Zen6架構代號Morpheus(希臘神話夢神摩耳甫斯),製造工藝將會進一步升級到CCD 2nm、IOD 3nm,而且CCD再次升級為原生32核心!

IPC性能預計再提升10%,同時加入面向人工智慧、機器學習的FP16指令,以及新的記憶體增強。

此外,Zen6據說還會有新的封裝技術,可能會將CCD堆疊在IOD之上,可以達到縮小晶片面積、提升內部通信效率,但就沒法直接堆成64核心了。

Zen6大機率會繼續沿用AM5封裝接口,畢竟AMD承諾過要支持到2026年。

來源:快科技