在國際可靠性物理研討會上,海力士CEO李錫熙提出了整合CPU以及記憶體的想法。目前記憶體標準正在准從DDR4過渡到DDR5上,後者相比前者可以帶來不少的性能增幅。不過,無論DDR記憶體有多快,與HBM相比在速度上還是要落後不少。這點也是李錫熙認為CPU以及記憶體應該要合並整合的基礎。

他在研討會上發表了對於一套「融合存儲以及邏輯」、更快的存儲標準的願景。

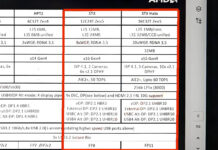

「高帶寬記憶體的速度提升是通過增加CPU及記憶體之間的通道而來的,而在CPU以及記憶體共同處於同一模塊的近記憶體處理(Processing Near Memory,簡稱PNM)中,速度提升會更多。如果更進一步的話,在記憶體內處理(Processing In Memory,簡稱PIM)中,當CPU以及記憶體都處於單一包裹(package)上的時候,速度可以獲得更大加的提升。而最終,CPU以及記憶體整合在同一晶片中的記憶體內計算(Computing in Memory,簡稱CIM)可以讓記憶體速度提升更加多。」

圖片來源:三星

海力士目前是全球第二大存儲生產商,不過他們並沒有開發及生產任何諸如CPU的晶片,因此CEO李錫熙呼籲半導體巨頭之間互相合作,形成一個可以維持CPU及記憶體集成的生態圈。

「只有在消費者、供貨商、學術界以及政府之間形成合作及共享的開放創新性的戰略合作關系,我們才可以塑造一個追求經濟及社會價值的新時代。」

另外,李錫熙也提出了一種名為Compute Express Link(CXL)的新標準,它可以與現有的PCIe總線互補。CXL記憶體可以快速且高效地在CPU以及圖形/計算加速器,或者智能網絡界面中移動數據。

「CXL記憶體不僅可以擴展帶寬以及容量,還可以實現持久性記憶體的價值,是一種可以縮小記憶體性能以及行業要求之間差距的解決方案。」

來源:超能網