Tag: 3nm

Intel Lunar Lake超低功耗處理器現身:居然是台積電3nm

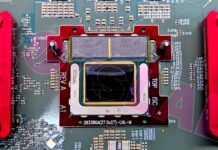

快科技3月28日消息,Intel將在今年晚些時候推出的超低功耗處理器Lunar Lake,現在第一次看到了它的驗證測試平台,供調試之用的。

和之前官方展示的裸片一樣,可以看到由三顆小晶片組成(其中一個應該是占位和保持形狀的),一側整合封裝了兩顆LPDDR5X內存,另外三個方向都有保護和固定用的金屬邊框。

之前展示的樣片

進一步消息確認,Lunar Lake包含MX Compute Die、MMX SoC Die兩個分離式模塊,其中前者的製造工藝並非Intel 20A,而是採用了台積電N3B,也就是3nm級別。

它包含4個Lion Cove架構的P核心、4個Skymont架構的E核心,也就是最多8核心8線程,也沒有AVX-512指令集。

相比之下,橫跨桌面和筆記本的Arrow Lake也是同樣的架構,但採用Intel 20A工藝,規格和性能都高得多。

GPU核顯部分,Lunar Lake升級到了第二代Battlemage架構的低功耗版本Xe2-LPG,最多8個Xe核心,但每個核心的流處理器或者說執行單元數量比第一代翻番,總計最多1024個。

根據內部測試,它的性能相比Meteor Lake最多可以再翻一倍,後者已經翻倍了。

Lunar Lake將在今年晚些時候發布,主打超低功耗領域,提供8W、30W兩個級別。

來源:快科技

3nm工藝 AMD未來APU有名字了:有希望上Zen6

快科技3月4日消息,AMD處理器一直在有條不紊地推進,現在第一次看到了未來APU的代號名字,非常特殊,叫做——“Sound Wave”(聲波)。

AMD將在今年年中左右發布Strix Point,預計命名為銳龍8050系列。

明年初追加不同定位的Fire Range、Stirx Halo(Sarlak)、Kraken Point,統一升級為4nm工藝、Zen5 CPU架構,大部分還都有RDNA3.5 GPU架構,應該都劃歸到銳龍9000系列的范疇。

Hawk Point、Escher則都是馬甲,工藝也是4nm,但架構還是Zen4。

Sound Wave應該要等到2026年了,製造工藝首次升級為3nm,而架構很有希望繼續推進到Zen6。

事實上,Zen5架構同時使用的是4nm、3nm兩種工藝,Zen6架構則會是3nm、2nm工藝的組合。

來源:快科技

傳聞天璣9400移動平台將採用台積電3nm工藝,性能提升巨大

此前已有不少傳聞稱天璣9400移動平台和第四代驍龍8移動平台將成為首批採用3nm製程節點的安卓陣容旗艦SoC。近日博主數碼閒聊站曝料,聯發科打算利用台積電的第二代3nm工藝來製造下一代旗艦SoC,而且博文中說到這款SoC的性能超強。

去年台積電的3nm生產線只有蘋果一個客戶,蘋果的A17 Pro和整個M3系列晶片都是採用台積電的"N3B "工藝製造,該工藝也被視為第一代3nm技術。數碼閒聊站在博文中提到,天璣9400移動平台將採用台積電第二代3nm工藝。對此wccftech則猜測這種工藝是台積電的"N3E"光刻工藝,據說這種工藝的晶圓產量比N3B高,價格也更合理,因此獲得了高通和聯發科的訂單。此前我們也有報導過,聯發科執行長蔡力行稱,聯發科正在與台積電深入合作新一代3nm晶片,目前項目正在推進當中,但他暫未透露過多技術細節。

此外博文中還提到天璣9400移動平台將採用ARM最新公版的CPU和GPU架構,因此聯發科這款旗艦SoC很大機率將搭載Cortex-X5核心。博文還提到,這款SoC的性能非常強,之前也有報導稱它在架構上將與天璣9300移動平台一樣,不配備能效核。

網上甚至已有傳聞稱天璣9400移動平台的綜合性能將強於第四代驍龍8移動平台,但鑒於驍龍今年將改用定製的Oryon內核,兩款SoC的性能差異暫不能妄下定論。 ...

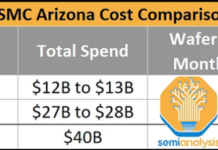

3nm晶圓超過14萬元 台積電做夢都笑醒:價格暴漲22%

快科技1月23日消息,根據分析師Dan Nystedt披露的數據,2023年第四季度,300mm晶圓的平均價格高達6611美元,約合人民幣4.8萬元,創下歷史新高,相比一年前飆升了22%!

當季,台積電出貨的晶圓折合300mm總計295.7萬塊,最近三年第一次不足300萬塊,相比2022年第四季度的370.2萬塊少了足足20%。

但因為價格上去了,台積電的收入卻沒怎麼少。

當然,工藝越先進,晶圓就越貴,N3 3nm級別工藝的每塊最貴可達2萬美元(約合人民幣14.3萬元),確實比N4/N5、N6/N7節點上貴得多。

工藝節點分布方面,N3隻是第二個季度取得收入,就奉獻了29.43億美元,占比已達15%。

N5依然是絕對主力,收入68.67億美元,占比高達39%。

N7收入也有33.354億美元,占比為17%。

以上三種先進工藝合計占了台積電總收入的67%,如果在算上16nm,所有的FinFET工藝收入占比為75%。

成熟工藝方面,28nm 7%,40/45nm 4%,65nm 5%,150/180nm 4%,110/130nm 3%。

來源:快科技

台積電籌劃第三座日本晶圓廠:最先進的3nm工藝

快科技11月22日消息,據媒體援引知情人士的消息稱,台積電正籌劃在日本建設第三座晶圓工廠,而且會生產至少目前最先進的3nm工藝。

這幾年,台積電在全球多地布局晶圓廠,包括美國、德國、日本。

其中在日本的第一座工廠位於日本南部的熊本縣,由索尼、電裝株式會社投資,正在建設中,進展順利,預計2024年底投產12nm工藝。

第二座工廠與之緊鄰,預計2025年投產5nm工藝。

規劃中的第三座工廠同樣位於熊本縣,編號“Fab 23 Phase-3”,也就是三期工程,將跨越到最新的3nm工藝。

不過,新工廠是否能夠落地、何時開建尚不明確。

即便能以最快速度開工,投產至少也要到2026年甚至是2027年,到時候3nm工藝將不再是最先進的,但依然是頂流。

甚至有說法稱,台積電有可能在日本建造第四座晶圓廠,或選址在熊本以北的另一個縣。

近年來,日本不斷在先進半導體工藝方面加碼,一方面通過數萬億日元的高額補貼吸引外企,包括台積電、美光、三星、力積電等,另一方面積極推動本土企業追趕世界先進水平,比如幫助本土創業公司Rapidus在北海道建立2nm工藝生產線。

對於熊本縣來說,能得到台積電如此青睞,無疑會讓當地經濟有一個巨大的飛躍,預計其GDP 2035年可達75萬億日元左右,比想現在增加足足50%。

來源:快科技

開天闢地第一次 Intel x86 CPU交給台積電代工

快科技11月22日消息,網上傳出一份Intel下下代處理器Lunar Lake的曝料,包含詳細的架構與技術規格、生產與製造工藝。

Meteor Lake開始,Intel採用了分離式模塊化結構,將原本完整的單顆晶片分成Compute、GPU、SoC、IO等不同模塊,可以採用不同工藝製造並組合,其中既有自己的Intel 4,也有台積電外包代工(具體仍未公布)。

明年的Arrow Lake也是如此,會首次加入Intel 20A。

後年的Lunar Lake還是如此,此前路線圖上顯示會加入Intel 18A,結合外部工藝。

此前9月底的技術創新大會上,

最新流出的信息顯示,Lunar Lake MX Compute模塊也就是包含CPU核心的部分,居然會交給台積電N3B,也就是第一代3nm。

如果屬實,這將是Intel x86高性能核心第一次由第三方代工!

Lunar Lake的定位有些特殊,並非多平台通吃,而是單獨面向低功耗移動平台專門設計的(所以不知道會不會叫第三代酷睿Ultra),包括8W無風扇設計、17-30W風扇設計。

它還是大小核混合架構,但布局與現在截然不同,最多4個Lion Cove架構的大核心單獨一組,有自己的二/三級緩存,最多4個Skymont架構的小核心另外單獨一組,有自己的二級緩存,彼此通過North Fabric交叉開關連接在一起,另外還有獨立的8MB系統緩存。

NPU 4.0 AI引擎和GPU部分都與大核心放在同一個Die里邊,其中GPU部分級為第二代Xe架構,也就是和明年的Battlemage獨立顯卡同源,只是功耗更低,核心數最多8個,支持實時硬體光追。

它甚至會將LPDDR5X-8533內存整合進來,封裝在一起,最多兩顆,容量16GB或者32GB,估計比傳統分離式設計可節省100-250平方毫米的封裝空間,但也是去了擴展性。

此外,擴展連接方面支持四條PCIe 5.0、四台PCIe 4.0、三個雷電4/USB4 40Gbps、兩個USB 3.1 10Gbps、Wi-Fi 7、藍牙5.4。

來源:快科技

AMD Zen5c架構巨變 三星4nm斜刺里殺出 與台積電3nm共舞

AMD將從明年起全年導入Zen5、Zen5c架構,包括桌面上的Granite Rapids、筆記本上的、伺服器上的Turin。

LinkIn上的AMD員工信息顯示,Zen5c架構的代號為“Promethus”,也就是普羅米修斯,古希臘神話中泰坦族的神明之一,父親是地母蓋亞與烏拉諾斯的兒子伊阿珀托斯,母親是名望女神克呂墨涅,曾與智慧女神雅典娜共同創造了人類。

更重要的是,Zen5c的代工工藝將同時包含台積電3nm、三星4nm(4LPP),這意味著AMD將採用雙代工模式,但具體如何分工暫不清楚。

媒體指出,AMD可能會讓三星試產或代工特定的IO晶片,但不太可能將重要的IP晶片交給三星。

三星為其Exynos手機處理器引入了AMD RDNA系列GPU架構授權,先後發布了RDNA架構的Exynos 2200、RDNA3架構的Exynos 2400,後續據說還有RDNA4架構的Exynos 2500。

雖然這些表現一般,但是三星和AMD的關系迅速升溫,拿下一部分代工也在意料之中,只是三星的工藝一直不讓人放心,AMD肯定有所保留。

畢竟過去這幾年,AMD一直依賴台積電,後者穩定、強大的工藝也是AMD取得今日成功的關鍵。

回顧一下歷代Zen架構代號:

Zen 2 (7nm) – Valhalla(英靈殿)

Zen 3 (7nm) – Cerberus(刻耳柏洛斯,古希臘神話地獄三頭犬)

Zen 4 (4/5nm) – Persephone(珀耳塞福涅,古希臘神話冥後)

Zen 4c(4/5nm) - Dionysus(狄俄尼索斯,古希臘神話酒神)

Zen 5 (3/4nm) –...

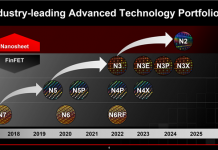

台積電豪言:我們的3nm就能打敗Intel 1.8nm

Intel正在積極推進“四年五個製程節點”計劃,將在2024-2025年搞定20A、18A工藝,分別相當於2nm、1.8nm,尤其後者預計會反超台積電,重奪領先。

對此,台積電自然不會坐視不理,對自己的技術也非常自信。

台積電總裁魏哲家聲稱,根據內部評估,台積電N3P 3nm工藝在性能方面就可以媲美Intel 18A,而且更早推出、更成熟、更省成本。

他還強調,台積電的2nm工藝比Intel 18A更加先進,2025年推出的時候將成為最先進的製程工藝。

Intel 20A/18A將會引入全環繞柵極電晶體RibbonFET,以及背部供電PowerVia。

台積電的N3/N3E/N3P/N3X 3nm系列則依然是傳統的FinFET電晶體,2nm工藝上才會上馬GAA全環繞電晶體。

其中,N2版本計劃2025年下半年量產,N2P版本計劃2026年底量產。

在過去的第三季度,5nm工藝為台積電貢獻了37%的收入,遙遙領先其他節點,其次是7nm 16%、28nm 10%、16nm 9%。

3nm在這個季度第一次為台積電創收,就帶來了約10.3億美元(感謝蘋果)。

相比之下,5nm工藝在2020年第三季度首次商用取得收入約9.7億美元,占比約8%。

來源:快科技

台積電、三星3nm實際良率只有50%?蘋果可能被坑了

據韓媒Chosun Biz近日報導,台積電、三星這兩大先進位程晶圓代工巨頭,在3nm製程上遭遇重大瓶頸卻未被曝光,稱這兩家廠商的3nm的良率可能都難以超過60%,遠低於吸引晶片設計廠商所需的水平。

若要成功吸引高通、英偉達等重量級買家,需要達到至少70%的良率才足夠。

報導稱,目前台積電和三星的3nm製程良率都維持在50%區間。

此前有報告一度顯示,三星為大陸客戶設計的晶片已達60%良率,但後來發現這個數字不包括邏輯晶片的SRAM,也就是非完整的3nm製程。

同一時間,為蘋果iPhone 15 Pro系列提供3nm的A17 Pro處理器代工台積電,其3nm工藝仍基於FinFET製程。

雖然此前一些專業人士預估,其良率最高可達70%以上,最新的信息顯示,A17 Pro實際良率僅大約在在55%上下,相當於生產2片晶圓就會有1片得報廢,也讓其下半年的運營展望增添變數。

根據台積電最新公布的9月營收計算,其三季度營收將達到5466億元,環比增長13.6%,創下同期第3高紀錄,營收表現優於財測預估。

除台積電和三星都准備在2024年和2025年生產更先進、更高效的升級版3nm製程,英特爾也計劃推出3nm的Sierra Forest和Granite Rapids晶片,並計劃在2024年量產Intel 20A和Intel 18A製程,預計2025年將會有相關產品上市。

英特爾今年7月曾表示,製造已達到產量和性能目標,但卻未給出具體數字。

來源:快科技

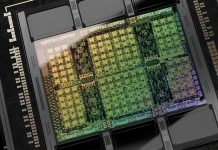

NVIDIA明年上馬3nm 私人定製 但不是遊戲卡

快科技9月26日消息,NVIDIA將在明年推出採用台積電3nm級工藝的下一代高性能計算GPU Blackwell GB100,以及下一代加速卡B100。

NVIDIA現有的GH100 GPU使用的是台積電4nm工藝,而且是定製版。

台積電3nm有多種版本,包括性能增強版N3P、高性能計算專屬N3X,NVIDIA GB100具體用哪個尚不清楚,估計很可能也會是定製版本。

事實上,NVIDIA Ampere、Ada Lovelace使用的台積電工藝,同樣都有很大的定製成分。

至於下一代遊戲顯卡GB20x GPU,應該也會是台積電3nm工藝代工,但要到2025年才能見到了。

蘋果是迄今唯一推出3nm工藝的廠商,A17 Pro用的是台積電第一代N3B,而聯發科已經使用第二代N3E工藝,完成下一代旗艦天璣9400的流片。

未來兩年,Intel、AMD、高通等也都會紛紛升級台積電的3nm工藝。

來源:快科技

緊追台積電 三星3nm工藝已量產三款晶片:功耗降低50%

快科技7月29日消息,在3nm節點,三星去年6月份就宣布量產,進度比台積電還快,不過後者拿到了蘋果等大客戶的訂單,三星沒有重量級客戶,這方面有所不如。

在日前的財報中,三星表示3nm工藝的良率已經穩定,代工廠正在順利量產第三款3nm晶片,不過三星沒有透露是為誰代工的。

日前有傳聞稱AMD也在尋求三星3nm工藝代工,但AMD的官方態度很模糊,沒有承認,但也表示確實在考慮台積電以外的晶圓代工夥伴。

三星的3nm工藝放棄FinFET電晶體技術,直接上了GAA電晶體,技術很激進。

根據三星說法,與7nm製造工藝相比,3nm GAA技術的邏輯面積效率提高了45%以上,功耗降低了50%,性能提高了約35%。

不過三星3nm工藝初期的良率確實不高,最近才傳聞提升到了60%,比台積電的3nm工藝55%的良率要好。

此外,除了第一代3nm工藝之外,三星還提到第二代3nm工藝及2nm工藝的進展良好,很有信心的樣子。

來源:快科技

全球首款3nm晶片 正式發布:不是蘋果的

雖然台積電3nm晶片已經量產,但截止昨天,我們都沒有看到晶片公司發布相關產品。到了今天,這個局面終於被打破了。

美國晶片公司Marvell表示,公司基於台積電 3 納米 (3nm) 工藝打造的數據中心晶片正式發布。

據Marvell介紹,公司在該節點中的業界首創矽構建模塊包括 112G XSR SerDes(串行器/解串行器)、Long Reach SerDes、PCIe Gen 6 / CXL 3.0 SerDes 和 240 Tbps 並行晶片到晶片互連。

按照Marvell所說,SerDes 和並行互連在晶片中充當高速通道,用於在chiplet內部的晶片或矽組件之間交換數據。與 2.5D 和 3D...

性能提升24% 蘋果M3處理器更強了:升級台積電N3E工藝

快科技4月10日訊,晶片行業的製程競賽,將在今年被拉到3nm。

據CT報導,相關法人透露,蘋果新款MacBook Air、iPad Air/Pro等,都將採用台積電3nm N3E工藝量產,分別在今年下半年和明年上半年對外亮相。

筆記本和平板上自然是M3處理器,而N3E則是台積電第二代3nm,對比N5同等性能和密度下功耗降低34%、同等功耗和密度下性能提升18%,或者可以將電晶體密度提升60%。

此前爆料顯示,M3處理器單核比M2 Max(12核)提升24%、多核提升6%。

就目前的進度來看,同樣是3nm,M3不太可能會早於A17處理器,也就是說15寸MacBook Air會在iPhone 15系列之後登場,這或許意味著其無緣在6月6日的蘋果WWDC開發者大會上首秀。

來源:快科技

台積電3nm加持 蘋果M3處理器跑分曝光:8核比12核M2 Max性能提升24%

A17和M3被認為是蘋果甚至是業內首批台積電3nm製程工藝的處理器產品,一款用於iPhone 15系列,另一款則將在Mac上首發。

日前,爆料人Vadim Yuryev分享了號稱是M3晶片的GeekBench 6跑分,單核3472,多核13676。

對比搭載12核M2 Max處理器的2023款16寸MacBook Pro(2793/14488),單核提升約24%、多核提升約6%。對比10核的M2 Pro,單核增幅類似,多核提升則擴大到12%。

需要注意的是,這顆M3晶片應該僅為8核設計,可見蘋果的研發功力以及台積電3nm基本讓人放心。

畢竟按照傳言,A17對比A16的跑分據說能高出43%之多,可謂擠爆牙膏。

外界預計蘋果M3會由13寸和15寸MacBook Air首發,最快於今年春季或者6月的WWDC開發者大會登場。

來源:快科技

蘋果包圓首批產能 消息稱台積電3nm日產量超千片:良率不是問題

在3nm工藝上,雖然三星在去年6月份搶先宣布量產,晚了半年的台積電卻後發先至,因為他們拿到了最重要的客戶——蘋果訂單,而且首批的3nm產能是蘋果包圓的,其他廠商都要靠後,甚至2023年都有可能是蘋果獨占。

目前蘋果用的是第一代3nm,也就是N3工藝,相比於5nm工藝,3nm工藝的邏輯密度將增加60%,相同速度下功耗降低30-35%,這是世界上最先進的技術。

其他廠商要等第二代3nm,也就是N3E工藝,對比N5同等性能和密度下功耗降低34%、同等功耗和密度下性能提升18%,或者可以將電晶體密度提升60%,密度比N3還縮水一些,但是成本也低。

那蘋果包圓的3nm工藝現在進展到底如何?消息人士透露,位於南科18B的3nm晶圓廠現在已經可以做到日投片量1000片,超過1000片的產量很重要,通常意味著晶片真正進入了量產階段。

有關台積電及三星的3nm良率一直都是個謎,此前的傳聞說是三星的3nm良率僅有10-20%,台積電的3nm良率可達70-80%,然而後者的良率也太高了,又被戳穿實際上只有不到50%良率。

不過隨著投片量超過1000片晶圓,台積電3nm良率爭議應該可以告一段落了,至少用於生產已經沒什麼大問題了。

來源:快科技

蘋果包圓台積電首批3nm Intel 15代酷睿明年才上:架構大改

台積電在去年12月29日宣布量產3nm工藝,雖然比三星的3nm量產晚了半年,但是台積電的優勢在於有大客戶加持,光是蘋果一家就足夠改變3nm格局。

即便當前PC市場的需求下滑,蘋果的3nm晶片似乎不受多大影響,digitimes最新報導中稱台積電3nm比預期表現更好,蘋果則首批包圓了3nm產能,其他廠商還要靠後。

台積電當前量產的3nm實際上是第一代的N3工藝,成本比較高,只有蘋果用得上倒也正常,其他廠商要等成本效益更好的二代3nm工藝N3E。

蘋果之後會有高通、聯發科等手機晶片廠商跟進3nm,Intel的計劃已經推遲,至少要到2024年Q4季度,會用在代號Arrow Lake的處理器上,3nm工藝主要用於製造GFX圖形模塊。

在此之前,Intel會在14代酷睿Meteor Lake上使用台積電5nm工藝製造的圖形模塊。

Arrow Lake被認為是15代酷睿,架構大改,而且CPU部分會用上20A工藝,2024年問世。

架構方面,Arrow Lake的CPU會升級Lion Cove微內核,IPC性能相比Golden Cove有雙位數的提升,也就是超過10%以上。

GPU單元則會受益於3nm工藝,規模大增,最高可達320組Xe單元,相當於2560個流處理器單元,遠高於當前酷睿的96組Xe單元,性能媲美獨顯不是夢。

來源:快科技

半導體急速降溫 三星產能利用率被曝僅70%:量產3nm也救不了命

2023年了,全球半導體行業的降溫還沒完,甚至情況更糟糕,台積電前不久發布的財報都顯示上半年會很難過,三星作為僅次於台積電的第二大晶圓代工廠自然也難免衰退,晶圓產能利用率預計會跌到70%,甚至更低。

來自韓國媒體的報導,多家韓國晶圓代工廠面臨著訂單下滑、產能利用率不足的問題,包括三星、DB HiTek、Key Foundry、SK Hynix IC、Magner Chip等,其中三星的工藝比較先進,12英寸居多,利用率平均70%左右。

後面幾家廠商代工的8英寸晶圓居多,利用率也是下滑最多的,DB HiTek還有60-70%利用率,更慘的一些甚至50%的利用率都沒有了。

對半導體製造來說,產能利用率不僅關繫著訂單多少,更嚴重影響了成本,光是折舊費就是一大筆費用,產線閒置太浪費了。

但是現在的需求下,三星這樣的第二大晶圓代工企業都面臨困境,該公司去年6月就宣布全球首發量產3nm工藝,比台積電早了半年,然而最先進工藝在手也沒能救命,現在需求還穩定的反而是汽車電子等成熟工藝產品。

來源:快科技

替代台積電 半導體巨頭博通稱考慮Intel晶片代工:「3nm」有戲?

在全球晶圓代工市場上,台積電是產能最大、技術最先進的公司,但是未來面臨的不確定性增加,因此很多半導體公司也在積極尋求新的代工夥伴,Intel也摻和了一腳,半導體巨頭博通表態考慮使用Intel代工,替代台積電。

博通CEO陳福陽日前在采訪談到了公司的戰略,表示還在尋求新的半導體並購,雖然2018年斥資1420億美元收購高通的案子被美國禁止,690億美元收購VMare還在歐美等國家進行反壟斷審查,但是並購依然是博通戰略的關鍵環節,他們有一個精選名單,包括半導體晶片及軟體公司。

不過博通CEO陳福陽沒有明確下一個要收購哪家公司。

此外,他還談到了公司的代工選擇,目前博通只有少部分零部件是自產的,大部分晶片依然要外包,當前主要合作夥伴是台積電,但陳福陽也表示正在考慮以Intel為潛在的代工夥伴,後者將成為台積電的替代供應商。

作為全球數一數二的無晶圓半導體設計廠商,博通這番表態對Intel是大大的利好,此前Intel也表示他們跟全球10大半導體中的7家廠商都在洽談合作,博通顯然是位列其中的。

至於博通具體使用什麼工藝,現在還不確定,但是雙方距離簽署真正的代工合同還有些時間,因此更有可能使用今年底量產的Intel 3工藝,這是Intel對外代工的主力工藝,對標友商的3nm工藝。

來源:快科技

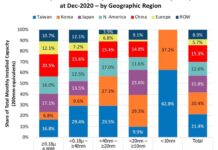

別只盯著3nm了 全球90%晶片產能都是10nm以上工藝

不可否認,我們通常會花很多時間談論領先的半導體製造。這是每個人在討論半決賽時都會犯的一個常見錯誤,我們和任何人一樣,世界正確地關注了能夠在前沿運營的公司的稀缺性,但半成品還有很多。

我們最近按工藝節點搜索了有關晶圓廠產能的數據,每個人都認為該主題的領先專家是IC Insights的Bill McClane。他保持著該主題上最嚴格的模型之一,並正確地為他的報告收取額外費用。

對於任何計劃多年半決賽路線圖的人來說,這是必讀材料。

一個快速的Google搜索從 IC Insight 的數據中得到了這段摘錄,它講述了一個重要的故事......

全球超過90%的半導體產能都在10納米或以上工藝上運行。

我們可以爭論分界線在哪里,但可以肯定地說,絕大多數產能都處於落後邊緣。

這很重要,原因有很多。

首先,當世界在2020/2021年耗盡半導體時——大部分短缺都發生在這些更成熟的工藝中。台積電的主要客戶都能夠在7nm獲得他們所需的大部分產能,但工業和汽車客戶確實感到痛苦。

這些公司需要微控制器 (MCU) 和電源管理 IC (PMIC) 等普通部件,而且這些產品通常是在較舊的節點上生產的。

如今,盡管許多品類的供應短缺已轉變為庫存過剩,但較老的產品只是在追趕兩年前被壓抑的需求。

其次,美國政府目前正在努力決定如何分配520億美元的CHIPS法案資金。

如果這些資金的目的只是為了將領先的工藝帶回美國,那就把所有的錢都給英特爾吧。

他們將向股東派發70億美元或80億美元的股息,並繼續實施他們無論如何都必須實施的趕上製造業的計劃。

另一方面,如果目標是真正確保美國半導體供應鏈的安全,那麼或許更好的計劃是更廣泛地分配這筆資金。

理想情況下,他們會花錢播下大量種子,以促成新公司的成立和基礎學術研究,然後由私營部門將其商業化。

不幸的是,目前還沒有簡單的機制來做到這一點,因此另一種方法是將資金分配給大量參與半成品製造的美國公司,只要他們承諾增加美國的產能即可。

這不僅意味著晶圓廠和代工廠,還需要包括工具公司、機器人供應商和化學品製造商——整個供應鏈。英特爾應該得到一些,但不是大部分資金。

據半導體行業協會稱,CHIPS法案通過觸發私營部門為美國半導體生產投資約2000億美元產生了積極的附帶影響。

最後,這些數字應該提醒我們,這個故事不僅僅是台積電和三星。在落後的代工廠中,仍有許多有趣、重要的工作正在進行。

最明顯的例子是Global Foundries。GloFo在矽製造方面並不處於領先地位,但它已經瓜分了一些非常可觀的“利基市場”,例如絕緣體上矽 (SOI) 和碳化矽。

雖然他們在這方面沒有台積電和三星在 7nm 上所享有的近乎雙頭壟斷,但他們的許多SOI生產線已經接近。

如果出於任何原因美國無法使用台積電,GloFo可以說是與英特爾一樣重要的解決方案的一部分。

來源:快科技

台積電、三星注意了 Intel的「3nm」工藝今年殺到:大量使用EUV

三星、台積電趕在2022年中、年末宣布量產了3nm工藝,繼續在先進工藝上領先,不過這兩家公司也不能放鬆,因為Intel追趕得很快,2023年不僅會量產Intel 4工藝,還會量產等效3nm的Intel 3工藝,迅速縮短距離。

Intel日本公司負責人日前在采訪中透露了Intel的工藝路線圖,在12代、13代酷睿的Intel工藝之後,Intel今年將在14代酷睿Meteor Lake上首發Intel 4工藝,這是Intel首次量產EUV工藝,每瓦性能提升20%。

在Intel 4之後,等效3nm工藝的Intel 3也會在年底量產,它基於Intel 4改進,每瓦性能上實現約18%的提升,也會使用EUV工藝,並且會擴大EUV使用規模。

首發Intel 3工藝的會是代號Granite Rapids的下下代至強處理器,這是一款採用全大核架構的伺服器處理器。

Intel 3工藝意義重大,不僅是Intel最後一代使用FinFET電晶體技術的工藝,也是Intel未來對外代工的重點,要跟台積電、三星搶市場的。

來源:快科技

代工價格14萬 AMD、NVIDIA等用不起 台積電3nm將降價

台積電在去年12月29日宣布3nm良率,CEO劉德音提到,相比於5nm工藝,3nm工藝的邏輯密度將增加60%,相同速度下功耗降低30-35%,這將是最先進的工藝。

台積電3nm良率傳出了一些雜音,稱第一代的N3工藝良率不足50%,而且投片量也非常少,只有蘋果一家客戶。

但是3nm真正的麻煩在於成本太貴,3nm代工價格突破2萬美元/片晶圓,也就是14萬元左右才能加工一片12英寸晶圓,生產數百顆晶片。

這樣的價格也難怪台積電3nm首發客戶只有蘋果一家,其他客戶,如AMD、NVIDIA、高通、聯發科等都認為太貴,並不基於推出3nm產品,至少要到2024年下班均為才會下單。

來自行業內消息人士@手機晶片達人的消息稱,台積電也准備降價3nm了,而且是所有3nm工藝都會降價,以便吸引客戶。

按照AMD之前的計劃,他們會在Zen5架構上使用3nm工藝,不過首發Zen4的會是4nm工藝,這意味著3nm Zen5架構至少也要到2024年年底了。

至於GPU晶片的計劃,AMD及NVIDIA下一代架構都要等到2024年,但能否上3nm工藝還有很多未知數,畢竟5nm/4nm才用了一代產品,潛力還沒挖掘完,上新一代工藝的意願不足。

來源:快科技

神話吹破 台積電3nm良率遠沒有80%:僅有蘋果少量下單

在3nm工藝上,雖然三星搶在2022年6月份就宣布量產3nm,成為全球首發,而台積電在12月29日才開始量產,只不過在3nm訂單及良率上,台積電一直被認為遠超三星,更有實際意義。

此前的傳聞說是三星的3nm良率僅有10-20%,台積電的3nm良率可達70-80%,差不多五倍優於三星,這意味著3nm工藝代工成本上的天淵之別,也難怪三星的3nm工藝沒有大客戶下單。

只不過實際情況可能並不是如此,台積電的3nm良率多少也被神話了,尤其是第一代的N3工藝。

來自半導體設備廠商的消息稱,目前量產的N3工藝良率不到50%,而且投片量非常低,只有蘋果一家少量下單,因此上半年帶給台積電的增幅並不多。

好在台積電准備了至少5種3nm工藝,N3之後還有N3E工藝,它的密度比N3其實要低,但是成本優化,因此得到了半導體廠商的追捧。

除了蘋果之外,高通、NVIDIA、AMD、聯發科等晶片公司都會跟進台積電N3E工藝,3nm代工才會放量,不過這都要2023年下半年之後了。

來源:快科技

韓國媒體:台積電3nm良率僅僅50%、三星「完美」

,台積電N3工藝目前的良品率低則60-70%,高則70-80%,與5nm工藝初期的水平類似。

相比之下,三星3GAE的初期良率要低得多,估計在10-20%左右,而且一直沒有明顯改善,晶片質量也參差不齊。

對於這樣的說法,韓國方面是絕對不服的。

1月10日消息,根據韓國經濟日報的報導,市場消息人士表示,三星目前已經大幅提高了其最尖端的3nm製程的良率與產量,用以相抗衡也已正式大規模量產3nm製程的晶圓代工龍頭台積電。

報導指出,南韓三星在2022年6月底正式宣布量產採用GAA 技術的3nm製程,而採用該製程的首家客戶是中國的一家IC 設計公司。

不過,因為當時三星的3nm製程被爆出良率僅有10%-20% 左右,使得其他潛在客戶沒有興趣。

但是,一位三星的高層指出,現階段三星的3nm製程良率已經達到“完美水準”,而且也在毫不遲疑地開發第二代的3nm製程。

報導還強調,台積電在日前才開始宣布大量生產的3nm製程,是採用傳統的FinFET 技術,而三星的3nm製程則是業界首個採用GAA 技術的節點製程技術,可以有效的提高晶片的性能與降低能耗。

因此,三星3nm製程的良率得以提升,即代表著能推進該節點製程的獲利能力的提升。

另外,雖然台積電落後三星量產3nm製程技術約半年的時間,但此前根據相關媒體報導指出,未來將由蘋果公司首先採用的台積電3nm製程良率高達85%,明顯優於三星。

不過,對於這樣的良率表現,韓國市場人士似乎並不相信,稱這樣的成績是被誇大了的。因為強調考量到台積電供應3nm晶片給首個採用的客戶——蘋果的數量與時間,預估其良率最高只有50%。

報導進一步指出,在三星與台積電都進入3nm製程的時代之後,未來3nm製程將會成為晶圓代工市場的主流。

因此,預計到2025 年之際,3nm製程市場的產值將會高達255 億美元,超越當時5nm製程預估的193 億美元產值。

根據市場調查單位TrendForce 的調查數據顯示,2022 年第三季,在全球晶圓代工市場中,台積電仍以53.4%市場份額穩居第一,排名第二的三星市場份額僅16.4%。

所以,在市場烈競爭下,也使得3nm製程將成為未來兩家公司主要競爭的關鍵。

PS:韓媒與台媒互相吹自己、踩對方早已經成習慣了,但是台積電、三星從不官方公布確切的良率數字,還是看產品吧。

來源:快科技

晶片報廢率80%的3nm可憐蟲:這下有救了

去年底台積電宣布3nm量產,預計今年年中之後在終端層面開始大規模應用。

隨後有業內專家透露,台積電3nm的良率可達80%,非常可觀。

然而,提前半年投產3nm的三星,則有些尷尬,據說良率僅20%。這個表現,難怪沒有大廠敢下單。

雖說三星上馬了GAA電晶體,技術難度高算是情有可原,然而和台積電差距這麼大顯然不是長久之計。

據DT報導,三星正在調整的一個優化方案是,在3nm EUV光刻中引進穿透率達90%的掩模保護膜,供應商是本土公司S&S Tech。

EUV光刻與此案的ArF(氟化氬)曝光設備不同,光反射到鏡子後,再到晶片,因此光源損失很大。要想使光源損失降到最低,必須使用穿透率超過90%的EUV用保護膜,從而保護光罩。

三星這一調整,能否有效提高3nm GAA晶片的良率,還有待檢驗。

來源:快科技

3nm來臨:台積電良率可達80% 三星渣得沒法看

三星、台積電已經先後宣布量產3nm工藝,台積電還特意舉辦了盛大的典禮。

台積電的命名為N3,號稱5nm之後的一個全新工藝節點,可將密度增加70%,同等功耗下性能提升10-15%,同等性能下功耗降低25-30%。

三星的命名為3GAE,首次引入GAA全環繞柵極電晶體技術(初期版本)。

據半導體專業人士分析,台積電N3工藝目前的良品率低則60-70%,高則70-80%,與5nm工藝初期的水平類似。

對於剛投入量產的先進工藝來說,這已經是非常不錯的良率水平,具備了大規模量產、供貨的條件。

台積電還在開發N3E、N3P、N3S、N3X等不同版本,這也奠定了很好的基礎。

相比之下,三星3GAE的初期良率要低得多,估計在10-20%左右,而且一直沒有明顯改善,晶片質量也參差不齊。

當然,以上數字都是業界估測,台積電、三星都不可能公布具體數字,只能走著瞧了。

不過,三星工藝拉胯也不是一次兩次了。

來源:快科技

為什麼說SRAM的死亡影響深遠?

據wikichip 報導稱,台積電的 3nm 工藝在 SRAM 密度方面與該公司之前的 5nm 節點相比,密度幾乎沒有提高。該出版物問了一個簡單的問題:我們剛剛見證了 SRAM 的消亡嗎?

至少在 Wikichip 看來,“SRAM的歷史縮放已正式死亡”。

這個想法對整個科技行業產生了巨大的影響,其影響將在未來幾年內在 PC 和其他設備中體現。但是您可能會問自己這一切意味著什麼以及您是否應該關心。

為了理解“SRAM 之死”將如何影響 PC 以及晶片設計者將如何應對,我們需要談談節點、摩爾定律和緩存。

摩爾定律逐漸消亡,現在突然

摩爾定律是半導體行業成功的基準,認為新晶片的電晶體數量應該是兩年前晶片的兩倍。英特爾、AMD 和其他晶片設計人員希望確保他們跟上摩爾定律的步伐,而跟不上就意味著將技術優勢拱手讓給競爭對手。

由於處理器只能這麼大,增加電晶體數量的唯一可靠方法是縮小它們並將它們更密集地組裝在一起。

節點或工藝是半導體製造商(也稱為晶圓廠和代工廠)製造晶片的方式;節點通常由電晶體的大小定義,因此越小越好。

升級到最新的製造工藝始終是增加電晶體數量和性能的可靠方法,幾十年來,該行業一直能夠滿足所有期望。

不幸的是,自 2010 年左右行業達到 32 納米大關以來,摩爾定律多年來一直行不通。當它試圖走得更遠時,它撞到了一堵磚牆。

從台積電到三星再到 GlobalFoundries,幾乎每家晶圓廠都在努力開發小於 32nm...

首批只有蘋果用得起 消息稱台積電3nm價格高昂:售價14萬元

台積電昨天(29日)舉行隆重的典禮,慶祝3nm工藝量產,雖然從時間上來說三星半年前就宣布首發3nm量產了,但是台積電的3nm工藝更有意義,因為會有大客戶落地。

台積電聯席CEO劉德音提到,相比於5nm工藝,3nm工藝的邏輯密度將增加60%,相同速度下功耗降低30-35%。

這是當前最先進的晶片工藝,同時也意味著這是當前最貴的工藝——來自業內人士的消息指出,3nm代工價格突破2萬美元/片晶圓,也就是14萬元左右才能加工一片12英寸晶圓,生產數百顆晶片。

不僅價格貴,目前良率還在爬坡,提升需要過程,再加上當前市場需求下滑,因此3nm首批投片量只有數千片,目前只有蘋果有需求,只有蘋果用得起這樣昂貴的新工藝。

來源:快科技

功耗降低35% 台積電3nm良率穩了:首發就不輸5nm工藝

今天上午,台積電舉行隆重的典禮慶祝3nm工藝量產。

台積電聯席CEO劉德音提到,相比於5nm工藝,3nm工藝的邏輯密度將增加60%,相同速度下功耗降低30-35%,這是世界上最先進的技術。

未來3nm量產的晶片將用於推動各種高科技產品,包括超級計算機、雲端數據中心、高速網絡及移動設備等,也包括未來的AR/VR設備等。

台積電還公布了3nm工藝的一個重要指標——良率,這個是檢驗新工藝是否真正量產以及具備競爭力的關鍵,良率一旦不達標,製造成本大增,沒有商業可行性。

台積電透露,3nm工藝的良率跟5nm工藝初期量產時的良率相當,台積電跟客戶聯合研發新品,並開始大量生產。

從台積電的表態來看,雖然沒有具體公布良率多少,但是他們的3nm良率顯然相當靠譜,至少客戶是同意開始生產的,意味著商業上是劃算的。

來源:快科技

台積電29日舉行典禮慶祝3nm量產:宣示最先進技術仍在手里

2022年就剩下最後幾天了,台積電多次提到過量產的3nm工藝終於確定下來了,將在29日舉行3nm量產典禮。

據悉,12月29日台積電將在台南科學園區的晶圓18廠新建工程基地,舉行3nm量產暨擴廠典禮,南科18廠是5nm及3nm生產基地,其中第五至九期廠房將投入量產3nm工藝。

在以往的先進工藝量產過程中,台積電從未舉行過慶祝典禮之類的活動,這次為3nm打破慣例,要通過一次盛大的活動來宣告量產,因此此次活動也備受矚目。

至於為何如此,分析認為台積電這次有2個目的,一個是展示自己的技術實力,今年6月份三星就搶先宣布量產3nm工藝了,但是三星的3nm一直被認為問題多多,而且沒有什麼大客戶支持,台積電的3nm量產才有更實際的意義,畢竟蘋果都要用。

第二個目的就是近來圍繞台積電的爭議很多,特別是台積電宣布大幅擴增在美國的投資之後,額外400億美元投資把3nm工藝都要帶給美國去,被視為在掏空台積電本土生產。

台積電這次也希望通過3nm量產典禮來澄清外界爭議,展示本土的晶圓廠依然是最先進工藝,破除有關掏空台積電的說法。

來源:快科技

台積電將舉行3nm量產儀式,以消除外界的疑慮

台積電(TSMC)原計劃完成3nm製程節點的技術研發和初步試產後,在今年第三季度下旬提升產能,將N3工藝正式帶入量產階段。不過最終由於各種原因,一直在推遲。

據UDN報導,台積電將於12月29日在台灣的台南科學園Fab18舉行3nm製程節點的量產儀式,期間還會有新工廠擴建的典禮,以消除外界對於其3nm工藝落後於時間表的疑慮。今年台積電的3nm製程節點一直處於謠言的中心,一方面有人批判台積電以新技術為由掩蓋研發上的問題,另有部分人則認為現階段沒有足夠的訂單支持這種價格昂貴的半導體工藝。

台積電一直以來都強調其3nm製程節點是按計劃推進的,台積電執行長魏哲家在2022年第三季度財報電話會議上表示,盡管庫存調整持續,但N3和N3E的客戶參與度很高,第一年和第二年的流片數量是N5的兩倍以上,目前正在與工作供應商密切合作,以准備更多的產能,應付2023年和2024年及之後的強勁需求。

台積電從2022年到2025年,將陸續推出N3、N3E、N3P、N3X等製程,後續還會有優化後的N3S製程,可涵蓋智慧型手機、物聯網、車用晶片、HPC等不同平台的使用需求。台積電在N3製程節點仍使用FinFET(鰭式場效應電晶體),不過可以使用FINFLEX技術,擴展了工藝的性能、功率和密度范圍,允許晶片設計人員使用相同的設計工具集為同一晶片上的每個關鍵功能塊選擇最佳選項,進一步提升PPA(功率、性能、面積)。 ...

Zen4差強人意 AMD急需3nm Zen5救場:可惜要到2024年

AMD今年推出了全新的Zen4架構,從技術上來說改變是很大的,升級5nm工藝,內核也做了大量改進,還帶來全新的AM5平台,支持DDR5記憶體、PCIe 5.0等新技術。

目前Zen4家族中已經有桌面版銳龍7000、伺服器版EPYC 7000系列,再過幾天的CES展會上,應該還會有銳龍7000移動版、銳龍7000G APU版及3D V-Cache版等新品。

整個2023年,AMD的CPU產品線都會圍繞Zen4進行強化布局,覆蓋每一個市場。

雖然還不到Zen4架構蓋棺論定的時候,但是從桌面版銳龍7000的表現來看,這一代的提升也不小,但沒有Zen3那一代驚艷,單核及遊戲性能也就是贏回12代酷睿的水平,略遜13代酷睿一籌,差強人意。

而且在定價上還鬧出了旗艦銳龍9 7950X首發5499沒多久就變成3999元的時間,難免打擊AMD高端用戶的信心。

A飯還能怎麼辦?眼下有2條路,一個是期待AMD繼續打磨4nm工藝的Zen4,除了銳龍7000移動版之外,3D V-Cache版銳龍7000也會上4nm工藝,再加上超大緩存的優勢,重新贏回遊戲上的領先。

只不過Zen4從5nm到4nm工藝升級,不太可能帶來質變,這就需要下一代的Zen5架構了,AMD還在開發中,但應該到後期階段了。

對於Zen5,現在是沒多少細節可說的,AMD之前提到Zen5架構會從頭投建,繼續提升性能及能效,也會有Zen5、Zen5 V-Cache、Zen5c三種架構變種。

Zen5還有個重要變化,那就是新工藝升級,這次會先上4nm,再上3nm工藝,這看上去跟Zen3先後升級7nm、6nm工藝,以及Zen4先後實用5nm、4nm差不多,但實際是不同的。

前面兩代升級工藝是兼容的,而台積電4nm是5nm的變種,3nm則是新一代工藝,跟4nm不兼容。

至於AMD為何在Zen5架構上採用這麼復雜的過度,恐怕是跟台積電的3nm工藝進度有關,一個是延期,一個是價格昂貴,初期有限的產能也只有蘋果能用得起,2023年幾乎都是蘋果獨攬,或許只有Intel能分走一部分N3E工藝訂單。

NVIDIA、AMD、高通、聯發科等客戶至少2024年才能用上3nm工藝了,即便如此2024年大家用上3nm Zen5的機會也不是很高,因為初期還是4nm Zen5,滿血版3nm Zen5到2025年都說不定。

來源:快科技

技術水平被Intel 7nm追上 台積電3nm艱難量產:下周見

2022年本來該是半導體工藝轉向3nm量產的一年,然而今年台積電低調了許多,三星搶在6月份就宣布率先3nm工藝,搶走了名義上的3nm首發,台積電早前提到的9月份量產早已無效,官方承諾的是年底。

距離2022年還剩下最後幾天了,台積電總算兌現了承諾,日前公司發布邀請函,下周將在南科舉辦量產暨擴廠典禮,屆時會正式量產3nm工藝。

這個時間點宣布量產,2022年的3nm產量可以忽略不記,只是讓台積電兌現今年量產3nm的承諾,真正有產品放量還要到2023年。

台積電之前公布了至少5種3nm工藝,現在還不好確定即將量產的是N3還是N3E,前者此前有爆料稱已經被放棄,因為成本太高,蘋果也不用了,導致沒有客戶,量產沒有意義。

根據台積電說法,對比N5工藝,N3功耗可降低約25-30%,性能可提升10-15%,電晶體密度提升約70%。

但是N3工藝實際的表現不一定有這麼好,前不久在IEDM 2022大會上,台積電論文種公布了3nm下SRAM的真實密度,表現讓人很擔心。

3工藝的SRAM單元的面積為0.0199平方微米,相比於N5工藝的0.021平方微米只縮小了區區5%!

更糟糕的是,所謂的第二代3nm工藝N3E,SRAM單元面積為0.021平方微米,跟N5工藝毫無差別。

台積電這樣擠牙膏的提升,讓Intel有了追趕回來的機會,雖然3nm的SRAM密度還是要比Intel的10nm ESF(現在的Intel 7)高不少,但跟Intel的7nm EUV工藝(現在的Intel 4)相差無幾。

台積電在下一代的2nm工藝上電晶體密度提升更少,官方數據也不過10%-20%,解釋很容易就被Intel的20A、18A工藝超越了。

來源:快科技

FinFET最後一代 台積電3nm全曝光 成本驚人

台積電 5nm 晶圓廠成本

2018年初,台積電宣布投資新晶圓廠。這個新站點將擁有其最先進的技術 N5。隨著蘋果和華為承諾在 2020 年生產 N5 晶圓,這是進行大規模擴建的絕佳機會。

台積電表示,他們對 Fab 18 第一至第三階段的投資將超過新台幣 5000 億元,約合 170 億美元。該站點計劃每月生產超過 80,000 個晶圓。

在 2020 年第一季度的財報電話會議上,台積電確認 N5 正在大批量生產,可能處於第一階段。

盡管台南科學園區的 Fab 18 仍將是...

台積電3nm N3徹底露餡了 對比5nm N5幾乎毫無差別

雖然誰都不願意承認摩爾定律已死,但是製程工藝的提升越來越難了,台積電就在3nm上遇到了極大的麻煩。

台積電曾經宣稱,3nm N3工藝相比於5nm N5可將集成密度增加60-70%之多。

但是,台積電的最新一份論文中承認,N3工藝的SRAM單元的面積為0.0199平方微米,相比於N5工藝的0.021平方微米只縮小了區區5%!

更糟糕的是,所謂的第二代3nm工藝N3E,SRAM單元面積為0.021平方微米,也就是和N5工藝毫無差別!

這種情況下的電晶體密度,只有每平方毫米約3180萬個。

與此同時,Intel 7工藝(原10nm ESF)的SRAM單元面積為0.0312平方微米,Intel 4工藝(原7nm)則縮小到0.024平方微米,改進幅度為23%,已經和台積電3nm工藝相差無幾。

照這麼看,Intel的工藝改名也是有幾分道理的。

另外,有數據表明,到了2nm及之後的工藝,電晶體密度將達到每平方毫米6000萬個左右,但需要所謂的“叉片”(forksheet)電晶體,而且還要等好幾年。

SRAM在現代晶片中一般用作緩存,比如銳龍9 7950X里的81MB緩存,比如NVIDIA AD102核心里的123MB緩存,它們往往需要先進的工藝支持,否則面積和成本會非常夸張。

事實上,考驗新工藝的第一步,普遍就是看SRAM的尺寸和密度有沒有明顯改進。

看起來,晶片廠商們越來越多使用chiplet小晶片和各種復雜封裝技術的路子是對的,單純依靠製程工藝越來越行不通。

來源:快科技

代工價格高達14萬元 台積電3nm真實性能大縮水:僅比5nm好了5%

台積電當前量產最先進的工藝是5nm及改進版的4nm,3nm工藝因為種種原因一直推遲,9月份就說量產了,又說年底量產,不過這個月就算量產,真正放量也要到明年了。

根據台積電之前的消息,3nm節點上至少有5代衍生版工藝,分別是N3、N3P、N3S、N3X及N3E,其中N3工藝是最早量產的,但是這版工藝遭到客戶棄用,很大可能就放棄了,明年直接上N3E工藝。

對比N5工藝,N3功耗可降低約25-30%,性能可提升10-15%,電晶體密度提升約70%。

N3E在N3的基礎上提升性能、降低功耗、擴大應用范圍,對比N5同等性能和密度下功耗降低34%、同等功耗和密度下性能提升18%,或者可以將電晶體密度提升60%,密度上甚至更低了一些。

考慮到近年來摩爾定律一直在放緩,70%左右的密度提升看起來還不錯,但這是台積電公布的最好水平,指的是純邏輯晶片,SRAM緩存的密度就只有20%了,N3E還會更低。

然而20%的提升依然是理論上的美好,台積電之前在IEDM會議上公布了更真實的數據,3nm工藝的SRAM緩存在電晶體密度上只比5nm高出5%,指標大幅縮水。

盡管3nm工藝還有10-15%的性能或者25-30%的功耗改進,但是這些指標顯然也是非常理想的情況,實際提升也會跟密度一樣存在縮水。

但是3nm晶圓的代工價格上漲是實實在在的,傳聞是2萬美元一片,約合人民幣14萬元,比5nm工藝漲價至少25%以上。

而且14萬元的價格還是基準價,如果廠商的訂單量達不到台積電的要求,價格還會大漲,超過10萬美元也很正常,也就是70萬人民幣了,這樣的價格下晶片設計廠商的成本根本撐不住。

也難怪台積電在需求下降的時候依然想逆勢漲價,但蘋果強硬拒絕,反擊台積電的理由就是蘋果這幾年的利潤率一直沒提升,台積電自己的利潤率已經從50%提升到60%了。

來源:快科技

3nm工藝 NVIDIA下一代顯卡GPU首曝光:代號Blackwell

這一代的NVIDIA GPU,在數據中心和遊戲顯卡,分別採用Hopper和Ada Lovelae兩套核心架構。

按慣例,下一代會按照兩年的周期進行更迭。

日前,在Arete技術大會上,NVIDIA副總裁、數據中心業務總經理Ian Buck確認了會在2024年推出Hopper繼任者的消息。

根據爆料,取代Hopper的下代GPU代號Blackwell。在此之前,外界就曾挖到名為GB100和GB102的新核心,算是比較有力的證據。

據稱NVIDIA正與台積電協作,致力於採用3nm工藝節點來製造Blackwell GPU。

從規格上來看,當前的Hopper的計算密度比RTX 4090還要高,下一代Blackwell肯定會更加強力。稍稍遺憾的是,到底RTX 50系顯卡的新GPU會選用哪位科學家代號,還是個謎。

資料顯示,David Harold Blackwell(戴維·布萊克維爾)是美國科學院首位黑人院士,加州大學伯克利分校首位黑人終身教授,一位傑出的數學家、統計學家,2010年去世。

來源:快科技

「3nm」工藝明年量產 Intel確認先進工藝投資不減:重回領先地位

由於市場需求下滑,PC領域也遭遇寒冬,作為龍頭的Intel也難免感受到了寒氣,前不久提出了削減成本的要求,愛爾蘭的工廠也開始自願性的無薪休假。

但是這並不會動搖Intel在先進工藝上重奪第一的決心,Intel副總裁、技術開發主管Ann Kelleher日前在采訪中透露了Intel在這方面的進展。

Intel當前量產的是Intel 7工藝,接下來的是Intel 4(等效4nm)工藝,首次使用EUV光刻工藝,已經准備量產。

再往後是Intel 3(等效3nm)工藝,是Intel 4的改進版,同時也是Intel大力推進用於代工的先進工藝,非常重要。

按照Intel的規劃,Intel 3工藝將在2023年H2量產,再往後就是2024上半年的20A工藝,2024年的18A工藝,等效2nm、1.8nm工藝,還會引入RibbonFET電晶體及PowerVias背面供電兩種黑科技。

以上幾種工藝就是Intel之前說的2021到2025四年內掌握5代CPU工藝的路線圖,但是這些先進工藝無一不是要燒錢的,一座晶圓廠投資都是百億美元起步。

根據Intel的計劃,包括美國及歐洲的工廠在內,投資額高達800億美元,再算上封測工廠之類的,整個IDM 2.0計劃可能要耗資1000億美元以上。

Intel的一個目標就是在2025年重新回到半導體行業的領導地位,不僅可以自產先進晶片,同時IFS代工業務也會贏得勝利,成為台積電、三星的強力對手,甚至坐三望二。

但是現在寒冬時節,Intel也制定了計劃在2025年前削減100億美元成本的目標,那先進工藝還能不能實現。

對於這個擔憂,Ann Kelleher在采訪中給出的答案就是不會,Intel在先進工藝上的投資不會削減。

來源:快科技

成本上天了 消息稱三星3nm良率僅有20%:急找美國公司援助

在3nm節點,三星搶先台積電半年就量產了,而且首發了GAA電晶體技術,然而除了一家做礦機晶片的中國公司試水之外,大型半導體廠商中還在觀望,沒誰確定要用三星的3nm。

按照三星的說法,目前量產的是3nm GAE工藝,夠降低45%的功耗,減少16%的面積,並同時提升23%的性能。

第二代的3nm GAP工藝可以降低50%的功耗,提升30%的性能,同時面積減少35%,效果更好,不過要到2024年才能量產,還有2年時間。

這樣的指標很誘人,如果三星能量產,不會沒有廠商使用,畢竟台積電3nm不僅量產時間晚,而且價格還高,優先供應蘋果也導致其他廠商在初期排不上號。

但實際情況並不是這樣,三星的3nm並沒有公司搶著上,只能說明是有些問題的,那就是良率偏低,根本沒法大規模量產,有消息稱3nm良率只有20%,這意味著要浪費80%的晶圓。

三星3nm工藝的代工價格不確定多少,台積電這邊傳聞是2萬美元,約合14萬人民幣,三星就算是打折代工估計也要10萬元,20%的良率用於生產的話,晶片成本要增加數倍以上,毫無競爭力。

正因為此,三星最近才跟美國Silicon Frontline公司達成了合作協議,雙方的合作有段時間了,成果會體現在3nm工藝上。

Silicon Frontline的技術可以減少晶圓加工中的缺陷,也就是說提高晶片的良率,兩家公司對彼此的技術合作很滿意,但具體提升多少良率還沒有相應數據公布。

來源:快科技

大量擴產3nm、5nm晶片:台積電將在美設3nm晶圓廠?官方回應尷尬未確定

台積電要在美國大量生產3nm、5nm先進位程晶片?官方回應了,結果很尷尬了,因為還沒有確定。

對於此前有信息稱台積電創始人張忠謀表示,台積電已經“差不多敲定”計劃在位於美國亞利桑那州的新工廠生產3nm晶片,台積電今晚回應《科創板日報》記者稱:“本月9日台積電曾回應,目前正在建設的亞利桑那州晶圓廠,包含一部份可能用於二期廠房的建築,透過利用一期同時建設的資源來提高成本效益。

按照官方的說法,這座建築能夠讓台積電保持未來擴張的靈活性。但就目前為止,台積電公司尚未確定亞利桑那州晶圓廠二期的規劃。

有鑒於客戶對台積公司先進位程的強勁需求,我們將就營運效率和成本經濟因素來評估未來計劃。目前尚無進一步消息。

對於是否擴產,台積電也是比較猶豫,因為目前環境非常的尷尬,全行業需求正在快速減退。

事實上,隨著全球半導體產能從緊缺轉向過剩,台積電也今年的資本支出從400億美元砍到了360億美元,主要是減少了先進工藝的投資,3nm的量產時間一再推遲。

雖然台積電之前一直強調3nm進度良好,客戶也很踴躍,然而就算是3nm首發客戶蘋果也在削減支出,智慧型手機、平板及PC需求下滑,蘋果也放緩了3nm量產步伐。

來源:快科技

三星3nm EUV工藝有救了 美國公司出手合作:可改善良率

現在先進工藝上,三星這幾年一直落後於台積電,但是3nm節點上三星搶先了,6月底就宣布量產了,比台積電至少提前半年時間。

然而三星的3nm量產除了一家礦卡公司採用之外,一直沒有大客戶支持,之前傳聞還有個手機晶片廠商,但是到現在也沒有見到產品爆料。

三星3nm為何雷聲大雨點小?其實廠商謹慎是對的,三星在良率方面多少都有不太好的歷史,3nm工藝不僅上了新一代的GAA電晶體,同時也更依賴EUV工藝,大規模生產良率很難保證,之前傳聞三星的4nm工藝良率也只有35%,先進一代的工藝只怕更難了。

三星也在想辦法優化改良工藝,韓國媒體爆料說三星跟美國Silicon Frontline公司達成了合作協議,雙方的合作有段時間了,成果會體現在3nm工藝上。

Silicon Frontline的技術可以減少晶圓加工中的缺陷,也就是說提高晶片的良率,兩家公司對彼此的技術合作很滿意,但具體提升多少良率還沒有相應數據公布。

對三星來說,只要晶片工藝技術問題能夠解決,從台積電手中搶到份額不是問題,高通前不久發布二代驍龍8的時候也明確表態了,會繼續跟三星合作,最快2年內就用上GAA工藝,也就是說三星的3nm工藝是有戲的。

來源:快科技