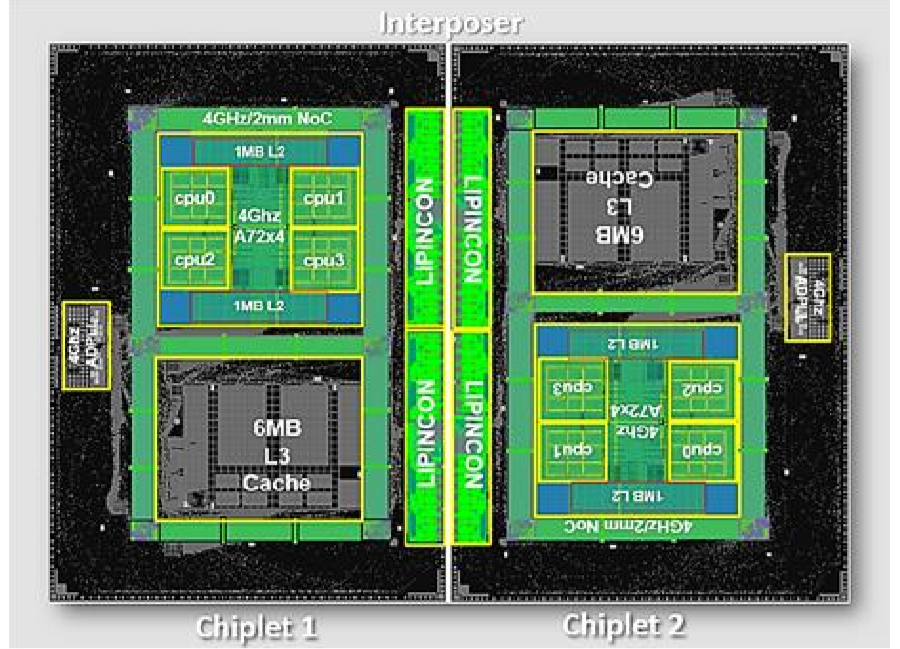

台積電和ARM在今天聯合宣布他們首創了業界第一個基於7nm工藝的多晶片系統(Chiplet System)。這個用於高性能計算(HPC)領域的多晶片系統的原型是基於多個高速ARM核心和一條Mesh總線,使用了台積電最新的LIPINCON內部互聯技術以及CoWoS封裝工藝。

AMD在Zen 2架構上面使用的架構就是一個典型的Chiplet System,CPU的計算核心以4個為一組CCX,CCX之間使用Infinity Fabric進行相互聯系,2組CCX也就是8個核心為一組CCD,而一個CCD就是一塊獨立的小晶片,而原本集成在一起的CPU Uncore部分被拆分出來單獨作為一片I/O Die,CCD與I/O晶片同時封裝在一塊基板上,這就是一個比較典型的Chiplet System。

採用多晶片的設計可以有效降低晶片的製造成本,尤其在7nm時代,大核心的良率達不到要求,生產成本也非常高,所以如AMD就直接在Zen 2處理器家族上面使用了兩種不同工藝生產的晶片封裝到一個基板上的技術以控制整體成本,並且可以提高良率,結果證明AMD的選擇還是比較明智的。

而這塊台積電與ARM聯手打造的新原型系統包含了兩片Die,每片Die上面有四個運行在4GHz下的ARM A72核心,它們擁有2MB的L2緩存以及6MB的L3緩存,兩片Die之間通過台積電的LIPINCON總線相連接,這個總線在0.3V的電壓、8GT/s傳輸速度的情況下,每秒帶寬可以達到320GB,而結合CoWoS封裝工藝,台積電宣稱它的功耗效能能達到每bit消耗0.56微微焦耳,而帶寬密度則可以達到每平方毫米1.6Tb/s,對比之下,AMD的Infinity Fabric總線約是2pJ/bit,Intel聲稱他們的EMIB總線為0.3pJ/bit,而MDIO為0.5pJ/bit。

台積電稱這個系統的試樣已經在2018年12月份就出了,今年4月份的時候已經開始生產了,他們將會在今年的VLSI上面披露更多細節。

來源:超能網