Sapphire Rapids是英特爾下一代至強(Xeon)可擴展處理器,使用了Golden Cove架構,採用10nm Enhanced SuperFin工藝製造,TDP為350W。新平台還支持PCIe Gen5、CXL 1.1(Compute Express Link)和八通道DDR5記憶體,同時會延續英特爾的內置AI加速策略,支持英特爾高級矩陣擴展(AMX)。此外,Sapphire Rapids還會推出HBM版本,搭載了容量為64GB的HBM2E記憶體。

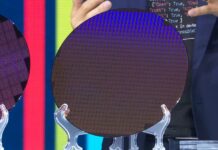

近日,有網友根據英特爾在ISSCC 2022(IEEE 國際固態電路會議)演講文稿中的高解析度晶片透視圖,對Sapphire Rapids做了注釋,以便更清晰地看到處理器的結構。作為一款成熟的多核心處理器,Sapphire Rapids具備了CPU內核、集成的北橋、記憶體和PCIe接口、以及其他的相關I/O部分。其內部有四個XCC晶片,每個會使用五個EMIB橋接器。

Sapphire Rapids使用的XCC晶片里,包含了15個Golden Cove架構內核,每個內核都有2MB的L2緩存,另外處理器總共會有112.5MB的L3緩存。雖然Sapphire Rapids的四個XCC晶片合計有60個內核,但出於良品率的考慮,只會最多開啟56個內核。每個XCC晶片會有一個128位(包括ECC在內是160位)的記憶體控制器,負責兩個DDR5通道,使得整個封裝內共支持八通道DDR5記憶體。

此外,每個XCC晶片都有一個PCIe 5.0/CXL 1.1接口,共32通道,意味著Sapphire Rapids會有128個PCIe 5.0/CXL 1.1通道。在Accelerator tile里,包含了Intel Data-Streaming Accelerator(DSA)、QuickAssist Technology(QAT)和DLBoost 2.0,這是涉及加速深度學習神經網絡構建和訓練的硬體。還有一個模塊里有24個UPI,用於插座間的互聯工作。

來源:超能網